来源:《半导体芯科技》杂志 10/11月刊

作者:Gayle Murdoch, imec技术团队主要成员;Zsolt Tokei, imec FELLOW兼纳米互连项目总监

半镶嵌集成是一种将互连工艺流程扩展至用于低于20nm金属间距的方法,该方法富有吸引力且具成本效益。IMEC是在五年前提出这种方法的,现今确认:已对一款18nm金属间距的功能性双金属级半镶嵌模块进行了首次实验演示。

半镶嵌集成和BEOL发展路线图

20多年来,铜(Cu)双镶嵌(dual-damascene)一直是构建可靠互连的主要工艺流程。但是,当尺寸继续缩小,并且金属间距(metal pitches)变得像20nm及以下那样紧密时,由于电阻电容(RC)乘积的急剧增长,后段制程(BEOL)越来越受到RC延迟的不利影响。这个问题迫使互连行业着手寻找替代集成方案,以及在紧密金属间距下具有更好品质因数的金属。

在本文中,imec的研究人员Gayle Murdoch和Zsolt Tokei着重阐述了紧密金属间距下通孔自对准的重要性,解释并演示了模块的主要技术参数,包括通孔和线路电阻以及可靠性。该研究结果在2022年IEEE VLSI技术与电路研讨会(VLSI 2022)上发表。

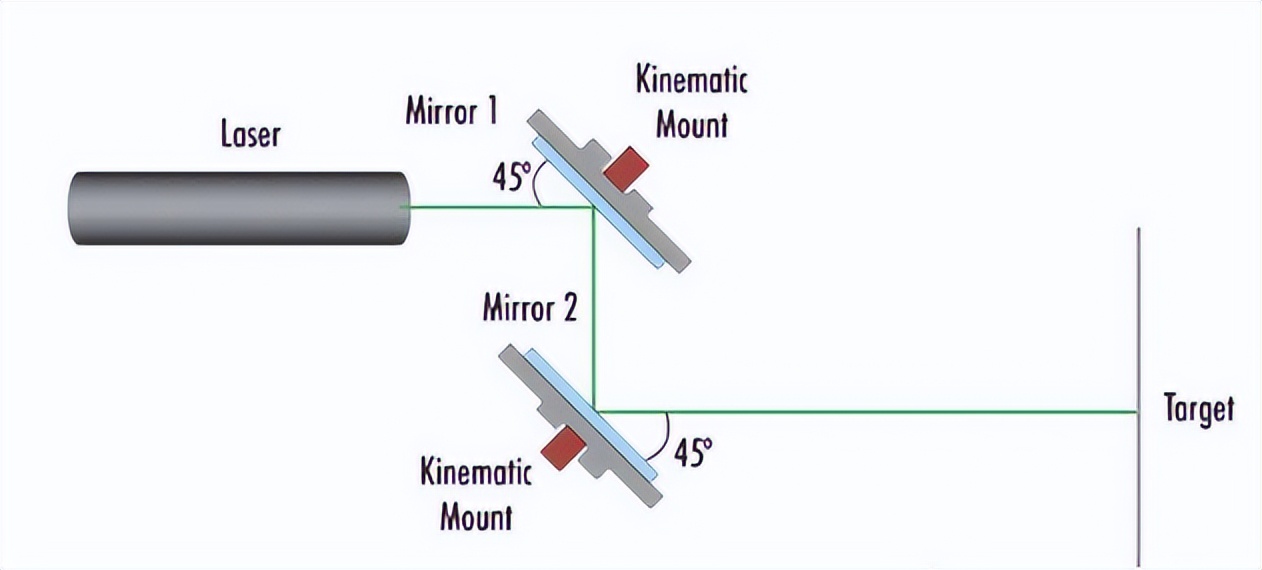

△图1:imec的半镶嵌流程:a)Ru蚀刻(底部局部互连线(Mx)的形成);b)间隙填充;c)通孔蚀刻;d)通孔填充和顶线(Mx+1)形成(在VLSI2022大会上展示)。

大约五年前,imec最初提出半镶嵌(semi-damascene)作为铜双镶嵌的可行替代方案,用于集成1nm(及以下)技术节点的最关键的局部(Mx)互连层。

与双镶嵌不同,半镶嵌集成依赖于互连金属的直接图案化来制作线条(称为减材金属化-subtractive metallization)。不需要采用金属的化学机械抛光(CMP)来完成工艺流程。

连接后续互连层的通孔以单镶嵌方式图案化,然后用金属填充和过度填充,这意味着金属沉积会继续进行,直到在电介质上形成一层金属。接着,对该金属层进行掩膜和蚀刻,以形成具有正交线的第二互连层。

在金属图案化之后,线之间的间隙可以用电介质填充,或用于在局部层处形成(部分)气隙。请注意,在半镶嵌流程中,一次性形成两层(通孔和顶部金属),就像传统的双镶嵌一样。当以双镶嵌为基准进行评估时,这使其具备很好的成本竞争力(见图2)。

△图2:18nm金属间距下半镶嵌与双镶嵌成本的比较。

半镶嵌集成流程的好处

据imec Fellow兼纳米互连项目总监Zsolt Tokei称,与铜双镶嵌相比,半镶嵌在紧密的金属间距下具有多项优势。他表示:“首先,它允许更高的线路纵横比,同时保持电容处于受控状态,这有望带来整体RC优势。其次,由于没有金属CMP工艺步骤,因而造就出更简化和成本效益更高的集成方案。最后,半镶嵌集成需要一种无阻挡层(barrierless)、可图案化的金属,例如钨(W)、钼(Mo)或钌(Ru)。通过使用不需要金属阻挡层的金属(这不同于铜),珍贵的导电区域就可以被互连金属本身充分利用,从而确保在微缩尺寸上具有竞争力的通孔电阻。”

△图3:沿Mx(左)和跨Mx(右)的自对准通孔。X-TEM显示自对准通孔落在18nm间距Ru线上(在VLSI 2022大会上演示)。

当然,除了上述好处之外,在这样的一项计划获得业界认可之前,还有许多挑战需要解决。朝这个方向迈出的一步是实际演示了双金属级方案。虽然迄今仅通过仿真和建模显示了这些好处,但是imec首次为双金属级半镶嵌模块提供了实验证据。

完全自对准的通孔:一个至关重要的构建块

在金属间距小至20nm的情况下,控制通孔降落在窄线上是半镶嵌集成模块成功运行的关键。当通孔和线路(在通孔顶部和底部)没有正确对齐时,通孔和相邻线路之间存在泄漏的风险。这些泄漏路径是由小通孔的常规图案化引起的过大覆盖误差造成的。

imec技术团队主要成员Gayle Murdoch说:“找到一种方法来制作功能性、完全自对准的通孔一直是半镶嵌工艺的‘圣杯’。我们通过imec的集成、光刻、蚀刻和清洗团队之间的密切合作实现了这一里程碑。凭借我们完全自对准的集成方案,我们能够补偿高达5nm的覆盖误差,这是一项重要的成就。”

通过在间隙填充后选择性去除氮化硅来确保底部自对准,从而允许在下部金属线的范围内形成通孔。朝向顶部金属层(Ru)的自对准是通过Ru过度蚀刻步骤实现的,该步骤在通孔过度填充和Ru图案化之后应用。

△图4:Ru线和Cu线的导电面积与线电阻的关系(在VLSI 2022大会上演示)。

新的里程碑:18nm间距下的良好电阻和可靠性

使用具有完全自对准通孔的Ru减法蚀刻(subtractive etch)产生了18nm金属间距的功能性双金属级器件。结合自对准双重图案化(SADP)的EUV光刻用于对9nm“宽”的Ru底部局部互连线(Mx)进行图案化,而单次曝光EUV光刻则用于印刷顶线(Mx+1)和通孔。顶部金属与气隙相组合以抵消电容的增加。

当将Ru与Cu的线路电阻与导电面积进行基准比较时,在目标金属间距下,Ru明显优于Cu。通孔自对准在形态学和电学上都得到了确证。实现了优异的通孔电阻(对于26~18nm的金属间距,其阻值范围在40Ω和60Ω之间),并且证实通孔到线击穿电场>9MV/cm。

Zsolt Tokei说道:“我们展示了所有关键技术参数的卓越价值,包括通孔和线路电阻及可靠性。该演示表明,半镶嵌是双镶嵌的一种有价值的替代方案,用于集成1nm技术节点及以后的前三个局部互连层。我们的具有完全自对准通孔的双金属级器件已被证明是关键的构建块。”

研究人员表示,通过增加线路的纵横比(这可以降低电阻),同时保持气隙(这可以控制电容),可以实现进一步的改进。与此同时,对使用半镶嵌技术(它允许在标准单元级别进一步减小面积)实现中段制程(MOL)和BEOL技术下一步改进,imec也已经有了具体的想法。

参考文献

Gayle Murdoch于1997年毕业于爱丁堡大学,获化学物理学荣誉学士学位。她的职业生涯先是在NECSemiconductors公司担任光刻工程师,后来加入Filtronic Compound Semiconductors公司,从事GaAs器件的蚀刻开发和集成工作,并最终成为首席蚀刻工程师。2008年,她加入了imec的先进光刻技术团队,然后在2013年转到BEOL集成部门。她从事过一系列课题的研发,包括低k电介质集成,完全自对准通孔,以及最近的半镶嵌集成。目前,她是技术团队的主要成员职位,并领导BEOL集成团队。

Zsolt Tokei是imec Fellow兼纳米互连项目总监。他于1999年加入imec,先是作为低k铜互连领域的一名工艺工程师和研究人员,接下来担任了金属部门的主管。之后,他成为了纳米互连项目的首席科学家和总监。他1994年在匈牙利德布勒森的科苏特(Kossuth)大学获得物理学硕士学位。1997年在匈牙利科苏特大学和法国艾克斯-马赛第三大学(Aix Marseille-III)大学共同指导的论文框架内,他获得了物理学和材料科学的博士学位。1998年,作为博士后研究员,他开始在德国杜塞尔多夫的马克斯-普朗克研究所工作。加入imec后,他继续从事一系列互连问题的研究,包括微缩、金属化、电气特性分析、模块集成、可靠性和系统等方面。

审核编辑 黄昊宇

-

模块

+关注

关注

7文章

2718浏览量

47560 -

IMEC

+关注

关注

0文章

57浏览量

22261

发布评论请先 登录

相关推荐

TRCX:掺杂过程分析

Techwiz LCD:基板未对准分析

热继电器的双金属片加热方式有几种

双金属片热继电器的工作原理作用

温度继电器的双金属片是什么形状

imec推出超导处理器,基于现有的CMOS制造工具

imec CEO建议台积电分散设厂降低风险

激光对准技巧的介绍

IMEC制造首个完全自对准的双金属级半镶嵌模块

IMEC制造首个完全自对准的双金属级半镶嵌模块

评论