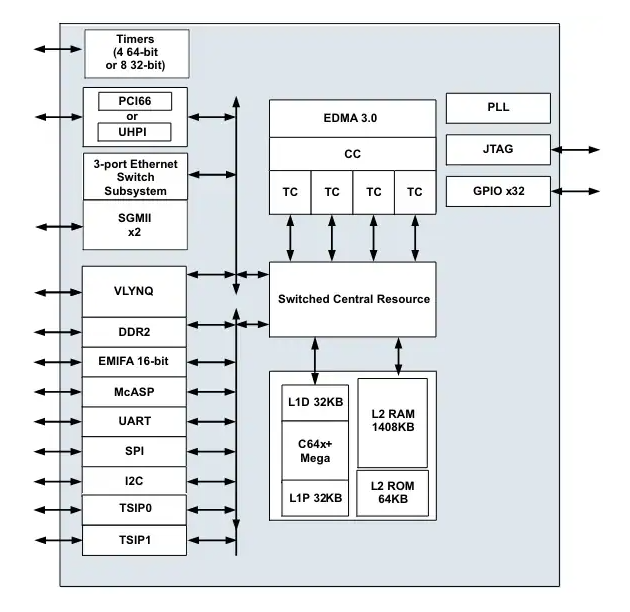

TI公司的TMS320C6655/57是不定点/浮点数字信号处理器(DSP),基于KeyStone多核架构,内核速度高达1.25GHz,集成了各种包括C66x内核,存储器子系统,外设和加速器在内的各种可编程子系统,非常适用于高性能可编程应用,如任务关键型,测试与自动化,医疗影像以及基础设施设备等领域。

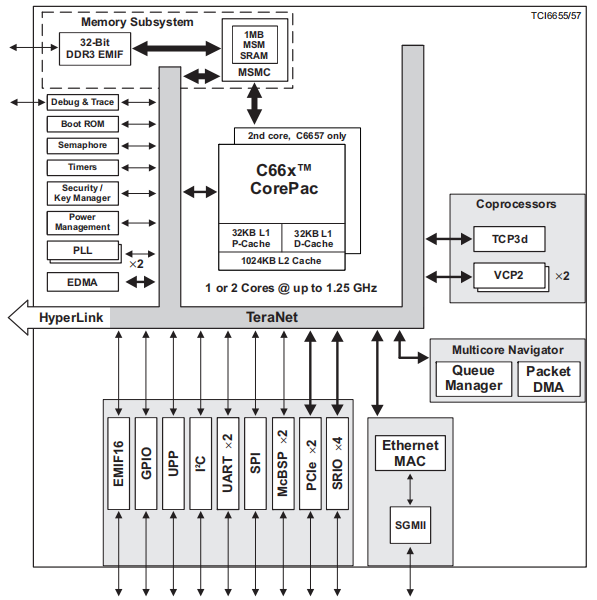

本文介绍了TMS320C6655/57主要特性,框图以及C6657+XC7Z035评估板XQ6657Z35-EVM主要特性,方框图,DSP部分电路图。

TI TMS320C6655/57 DSP 是一款性能最高的定点/浮点 DSP,基于 TI 的 KeyStone 多核架构。该器件采用全新的创新 C66x DSP 内核,能够以高达 1.25 GHz 的核心速度运行。对于任务关键型、医学成像、测试和自动化以及其他需要高性能的应用等广泛应用的开发人员,TI 的 TMS320C6655/57 DSP 提供高达 2.5 GHz 的累积 DSP,并支持高能效且易于使用的平台。此外,它与所有现有的C6000系列定点和浮点DSP完全向后兼容.

TI的KeyStone架构提供了一个可编程平台,集成了各种子系统(C66x内核,存储器子系统,外设和加速器),并使用多种创新组件和技术来最大化设备内和设备间通信,从而使各种DSP资源能够高效无缝地运行。此架构的核心是关键组件,例如多核导航器,它允许在各种设备组件之间进行有效的数据管理。TeraNet 是一种无阻塞交换机结构,可实现快速且无争用的内部数据移动。多核共享内存控制器允许直接访问共享内存和外部内存,而无需从交换机结构容量中汲取资金。

对于定点使用,C66x 内核具有 4× C64x+ 内核的乘法累加 (MAC) 能力。此外,C66x 内核集成了浮点功能,每个内核的原始计算性能是业界领先的 40 GMACS/内核和 20 GFLOPS/内核(@1.25 GHz 工作频率)。它每个周期可以执行 8 个单精度浮点 MAC 操作,可以执行双精度和混合精度操作,并且符合 IEEE754 标准。C66x 内核包含 90 条新指令(与 C64x+ 内核相比),旨在实现浮点和面向矢量数学的处理。这些增强功能对信号处理、数学和图像采集功能中使用的常用DSP内核的性能有了相当大的改进。C66x 内核向后兼容 TI 上一代 C6000 定点和浮点 DSP 内核的代码,确保软件可移植性并缩短迁移到更快硬件的应用的软件开发周期。

TI C6655/57 DSP 集成了大量片上存储器。除了 32KB 的 L1 程序和数据缓存外,每个内核还有 1024KB 的专用内存,可以配置为映射的 RAM 或缓存。该器件还集成了 1024KB 的多核共享内存,可用作共享 L2 SRAM 和/或共享 L3 SRAM。所有 L2 存储器都集成了错误检测和纠错功能。为了快速访问外部存储器,该器件包括一个运行频率为 1333 MHz 的 32 位 DDR-3 外部存储器接口 (EMIF),并支持 ECC DRAM。

该系列支持许多高速标准接口,包括 RapidIO ver 2、PCI Express Gen2 和千兆以太网。它还包括 I2C、UART、多通道缓冲串行端口 (McBSP)、通用并行端口和 16 位异步 EMIF,以及使用通用 CMOS IO。对于设备之间或与FPGA的高吞吐量、低延迟通信,包括一个称为HyperLink的40 Gbaud全双工接口。

TI DSP C6655/57 器件具有一套完整的开发工具,其中包括:增强型 C 编译器、用于简化编程和调度的程序集优化器,以及用于查看源代码执行情况的 WindowsR 调试器接口。

TI TMS320C6655/57主要特性:

1、一个 (C6655) 或两个 (C6657) TMS320C66x ™ DSP 内 核子系统 (CorePacs),每个系统都拥有

1.1、850 MHz(仅 C6657),1.0 GHz 或 1.25 GHz C66x 定点/ 浮点 CPU 内核

1.25 GHz 时,定点运算速度为 40 GMAC / 内核

针对浮点 @ 1.25GHz 的 20 GFLOP / 内核

1.2、存储器

每内核 32K 字节一级程序 (L1P) 内存

每核 32K 字节一级数据 (L1D) 内存

每核 1024K 字节本地 L2

2、多核共享存储器控制器 (MSMC)

2.1、1024KB MSM SRAM 内存 (由 C6657 的两个 DSP C66x CorePacs 共享)

2.2、MSM SRAM 与DDR3_EMIF 的内存保护单元

3、多核导航器

3.1、带有队列管理器的 8192 个多用途硬件队列

3.2、基于包的 DMA 支持零开销传输

4、硬件加速器

4.1、两个 Viterbi 协处理器

4.2、一个 Turbo 协处理器译码器

5、外设

5.11、4 个 SRIO2.1 线道

每通道支持 1.24/2.5/3.125/5G 波特率运行

支持直接 I/O,消息传递

支持四个 1x,两个 2x,一个 4x,和两个 1x + 一个 2x 链路配置

5.12、PCIe Gen2

单端口支持 1 或 2 个通道

每通道支持的速率高达 5 GBaud

5.13、HyperLink

连接到其它支持资源可扩展性的 KeyStone 架构连接

支持高达 40 Gbaud

5.14、千兆以太网 (GbE) 子系统

一个 SGMII 端口

支持 10/100/1000 Mbps 工作速率

5.15、32 位 DDR3 接口

DDR3-1333

8GB 可寻址空间

5.16、16 位 EMIF

5.17、通用并行端口

两个通道,每个 8 位或 16 位

支持 SDR 和 DDR 传输

5.18、两个 UART 接口

5.19、两个多通道缓冲串行端口 (McBSP)

5.20、I2C 接口

5.21、32 个 GPIO 引脚

5.22、SPI 接口

5.23、信号量 (Semaphore) 模块

5.24、8 个 64 位定时器

5.25、两个片上 PLL

5.26、SoC 安全支持

商用温度:0°C 至 85°C

扩展温度范围:-40°C 至 100°C

扩展低温:-55°C 至 100°C

TMS320C6655/57框图

基于TMS320C6657+XC7Z035评估板XQ6657Z35-EVM

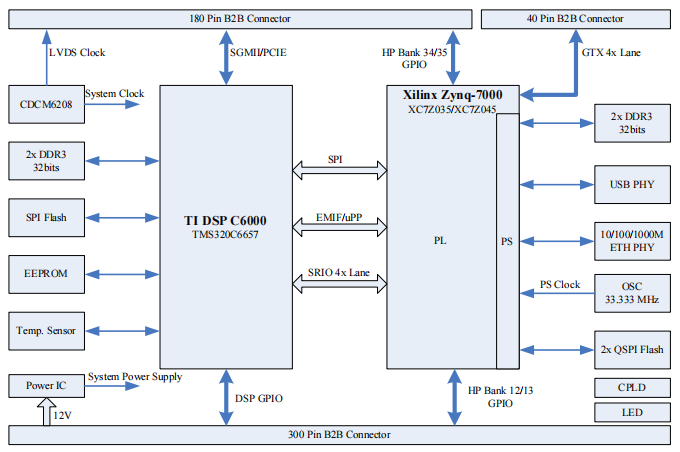

TI DSP TMS320C6657+XC7Z035评估板由广州星嵌电子科技有限公司自主研发,是基于TI 多核DSP TMS320C6657 和Xilinx Zynq SoC处理器XC7Z035设计的,由核心板与底板组成。

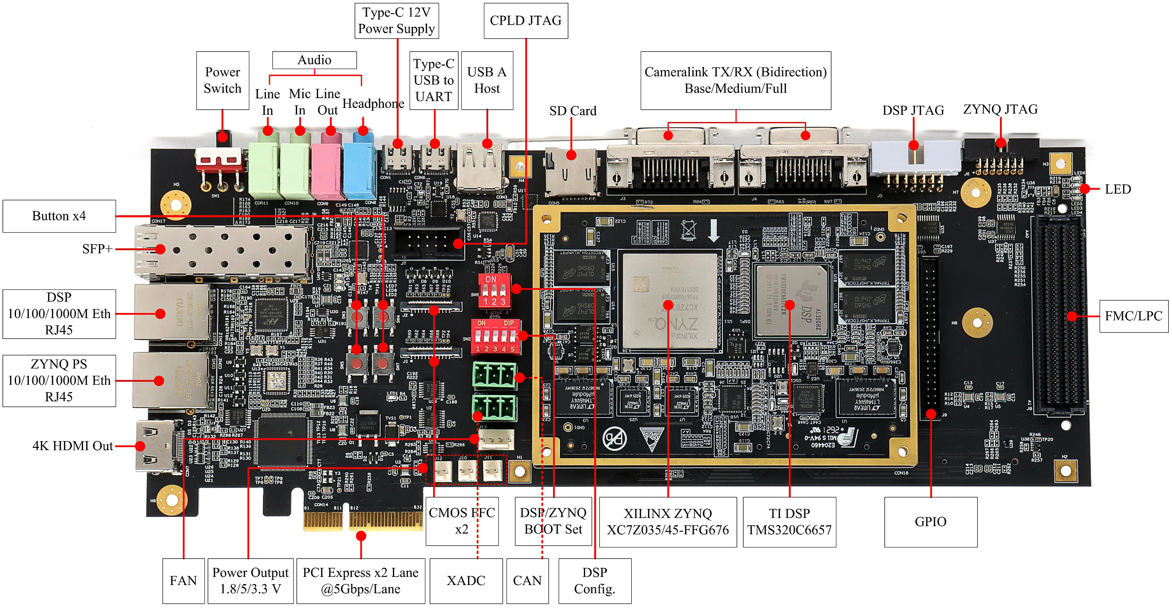

核心板内部通过SPI、EMIF16、uPP、SRIO 通信接口将DSP 与Zynq 结合在一起。底板接口资源丰富,引出2路 CameraLink 双向可输入输出、1路 SFP+光口、2路千兆网口、双通道 PCIe、USB2.0、Micro SD、LPC FMC、M.2、音频输入输出等接口,方便用户快速进行产品方案评估与技术预研。

XQ6657Z35-EVM是一个高性能、经济高效的独立开发平台,使用户能够评估和开发德州仪器的应用程序。评估模块 (EVM) 还可用作 TMS320C6657 DSP 的硬件参考设计平台。

提供原理图、代码示例和应用笔记,以简化硬件开发过程并缩短上市时间。http://web.xines.cn/pingguban/28.html

评估板XQ6657Z35-EVM主要特性:

1、DSP处理器型号:TI TMS320C6657CZHA25,双核C66x,主频1.25GHz

2、FPGA处理器:Xilinx Zynq7000 SoC XC7Z035-2FFG676I(2x ARM Cortex-A9,主频 800MHz(-2),2.5DMIPS/MHz ,1x Kintex-7 架构可编程逻辑资源)

3、CPLD:MAX10型号10M02SCM153

4、DSP SPI Flash:32MByte

5、FPGA SPI Flash:64MByte

6、EEPROM:1Mbit

7、DSP DDR3:1GBytes

8、ZYNQ DDR3:1GBytes(PS端)

10、CameraLink :支持2路Base输入或者2路Base输出或者1路Full 输入或输出

11、SFP+:1路支持万兆光模块

12、千兆网口:DSP 1路、ZYNQ PS 1路

13、PCIe:1x PCIe 双通道 (DSP端)

14、SD:1x Micro SD

15、USB:1x USB 2.0

16、DSP IO:38个

18、HDMI:1x HDMI OUT (PL端)

19、音频:1x LINE IN、1x MIC IN、1x LINE OUT

20、LPC FMC:1路

21、电源接口:1x TYPE-C接口 12V@4A或标准PCIe供电

TMS320C6657 器件基于德州仪器 (TI) 开发的第三代高性能、先进的 VelociTI™ 超长指令字 (VLIW) 架构,专为高密度有线/无线媒体网关基础设施而设计。该设备是 IP 边界网关、视频转码和翻译、视频服务器以及智能语音和视频识别应用的绝佳选择。C66x 器件向后兼容属于 C6000™ DSP 平台的先前器件的代码。

TMS320C6657+XQ7035核心板框图

TMS320C6657+XQ703评估板正面图

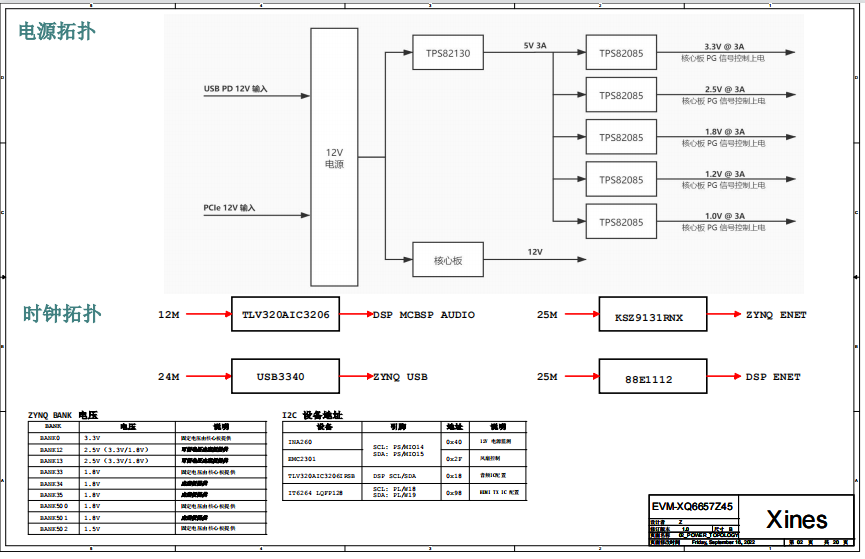

XQ6657Z35-EVM底板-DSP原理图

XQ6657Z35-EVM底板原理图1-电源时钟

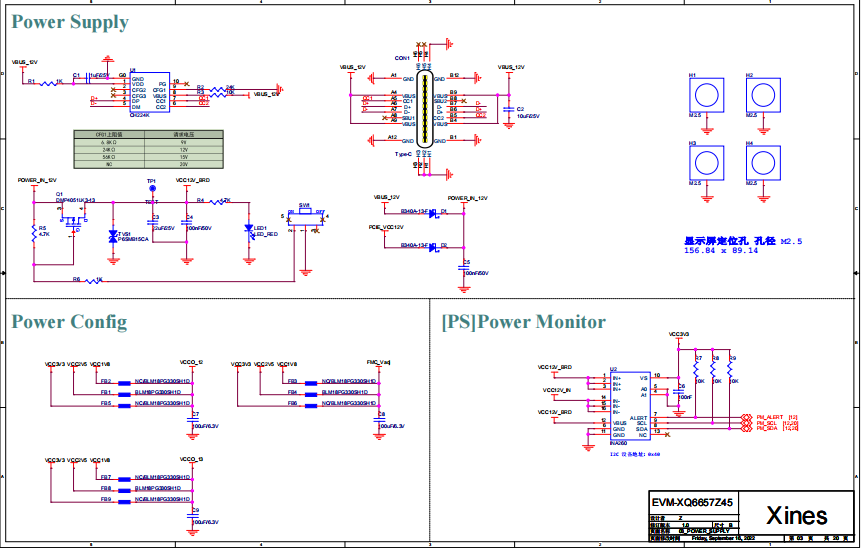

XQ6657Z35-EVM底板原理图2-Power Supply

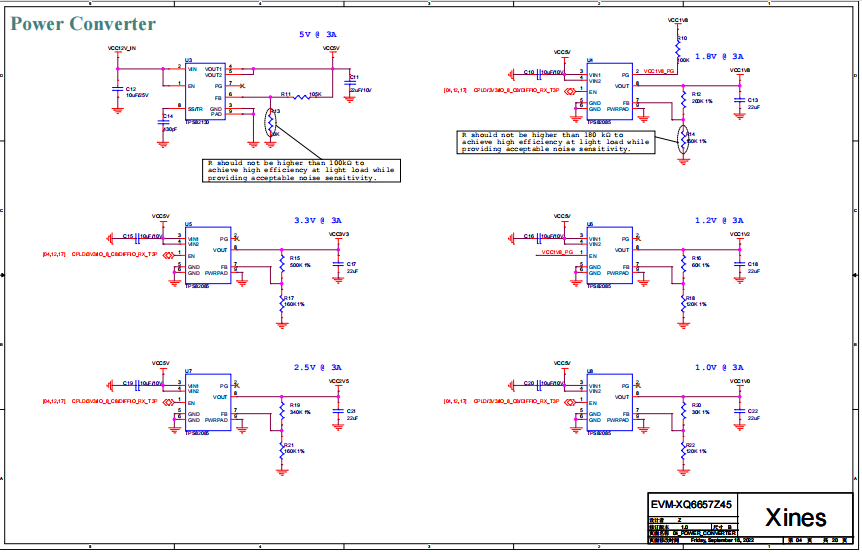

XQ6657Z35-EVM底板原理图3-Power Converter

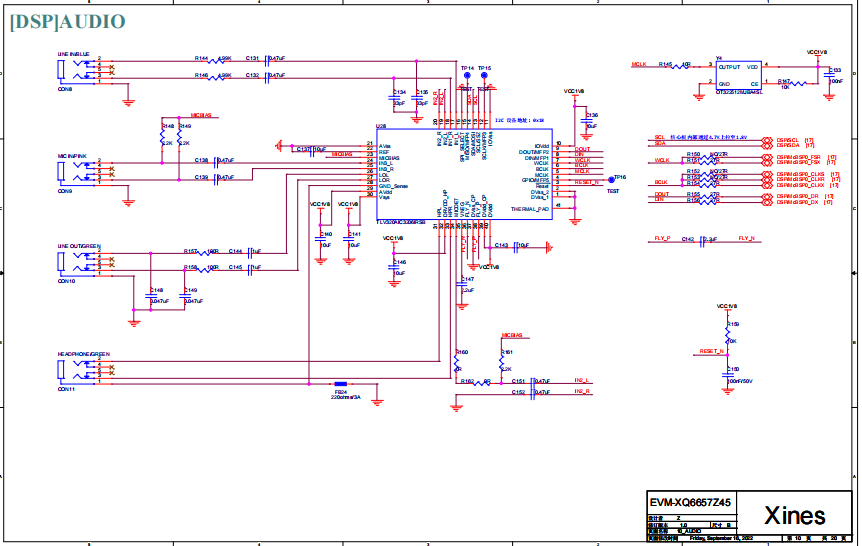

XQ6657Z35-EVM底板原理图4-音频

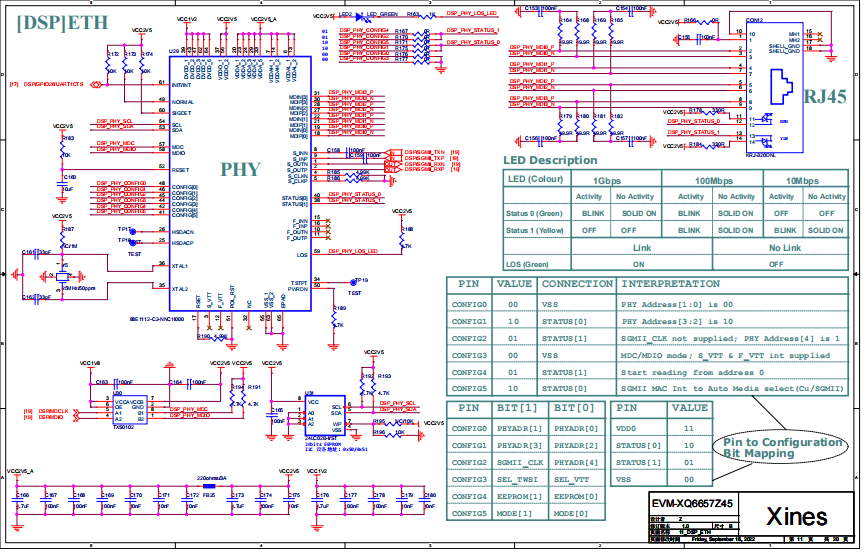

XQ6657Z35-EVM底板原理图5-网络

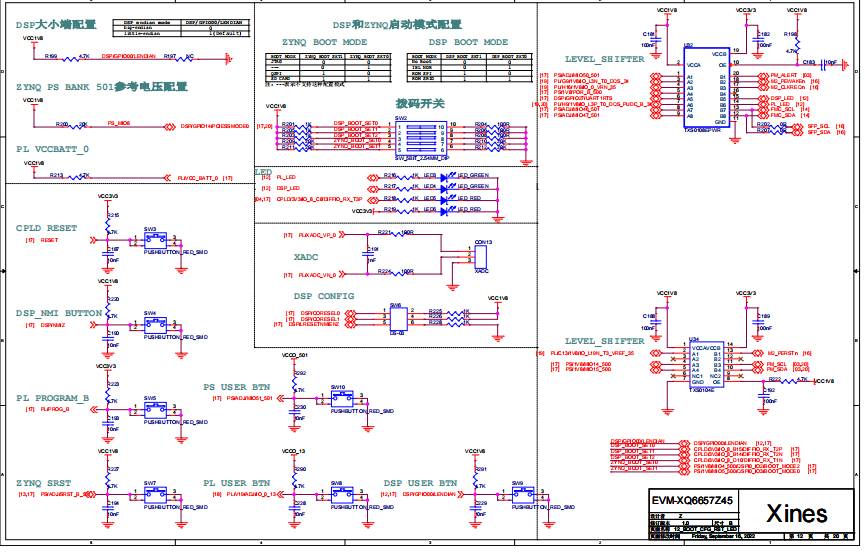

XQ6657Z35-EVM底板原理图6-启动配置

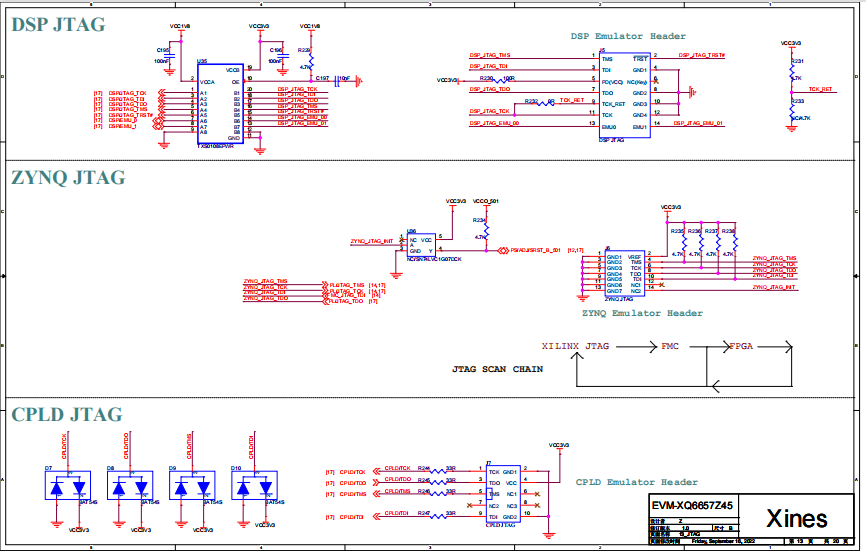

XQ6657Z35-EVM底板原理图7-JTAG

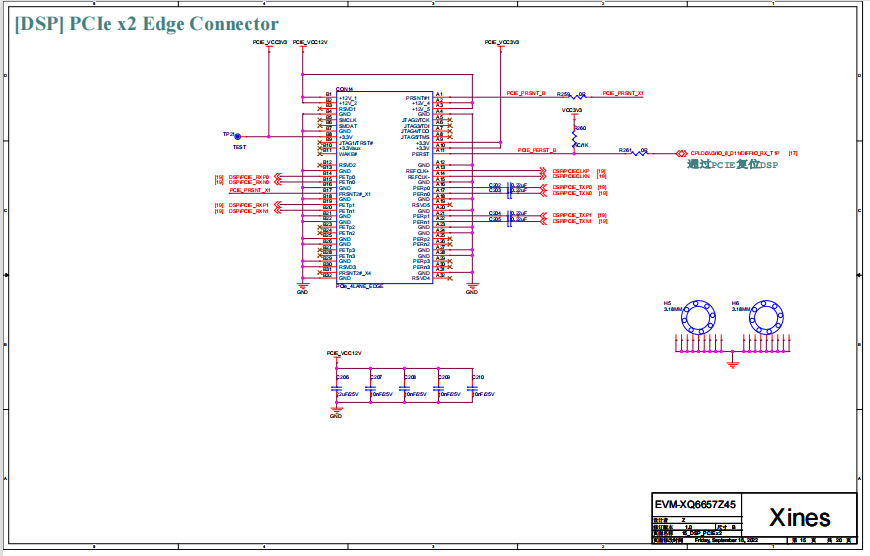

XQ6657Z35-EVM底板原理图8-PCIe x2

审核编辑 黄昊宇

-

数字信号处理器

+关注

关注

5文章

529浏览量

28518

发布评论请先 登录

TMS320F281x与TMS320C281x DSPs:功能特性与应用指南

TMS320F281x/C281x DSPs:高性能数字信号处理器的全面解析

TMS320F280x/C280x系列数字信号处理器深度解析

TMS320F243与TMS320F241 DSP控制器:数字信号处理的得力助手

TMS320C6204 定点数字信号处理器全方位解析

深入解析TMS320F280x与TMS320C280x系列数字信号处理器

TMS320LF2401A与TMS320LC2401A DSP控制器深度解析

TMS320VC5507 DSP深度剖析:从特性到应用的全方位指南

SM320F281x/C281x DSP系列:高性能与多功能的完美融合

TMS320C6211与TMS320C6211B定点数字信号处理器深度解析

TMS320x240xA 系列 DSP 控制器:特性、应用与设计要点

TMS320C206/TMS320LC206数字信号处理器深度解析

基于4片DSP6678+FPGA KU115 的VPX高速信号处理平台

TI PCI2040:PCI - DSP桥接器的深度解析

Texas Instruments TMS320C6452数字信号处理器(DSP)数据手册

DSP+FPGA评估板 TI TMS320C6657 1.25GHz-DSP原理图

DSP+FPGA评估板 TI TMS320C6657 1.25GHz-DSP原理图

评论