为了降低接触电阻和串联电阻,在集成电路制造中引入了硅化物工艺,业界先后采用了可规模生产的 WSi2、TiSi2、CoSi2、NiSi 等工艺。

早期发展起来的钨硅化物工艺采用 WF6作为钨原料,并用Si2H6作为硅原料,通过 CVD 加热技术将其沉积到多晶硅表面后生成钨硅化物。

在钨硅化物工艺之后,集成电路芯片制造中主要有如下3种硅化物工艺。

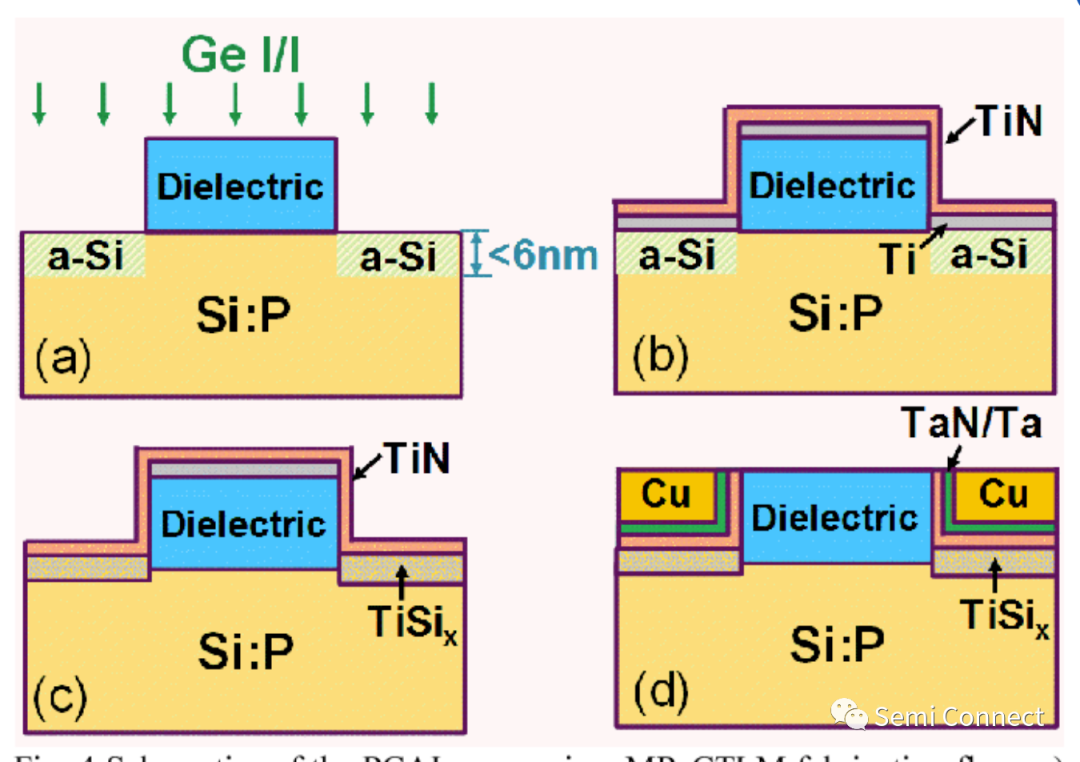

(1)钛硅化物TiSi2工艺:广泛应用于0.25umn 以上集成电路的制造,具有工艺简单、高温稳定的特点。产业中的主流工艺是采用 PVD 物理溅射方法将Ti金属沉积在晶片上形成薄膜,然后经过两次退火处理。

其中,第1次的退火温度为 600~700℃,形成高阻的中间相C49;第2次退火温度稍高,为 800-900℃,使C49相转变为低阻的 C54 相。

当线宽变得过窄时,第2次退火转变所需的温度和时间可能大幅度增加。

但因受热预算的限制,使得退火温度不能过高,避免硅加剧扩散而引起漏电和短路。因此需要精密控制温度参数,尤其是随着 MOS 尺寸变小时,应尽量控制 TiSi2相变的充分性,保证接触电阻不会增加。

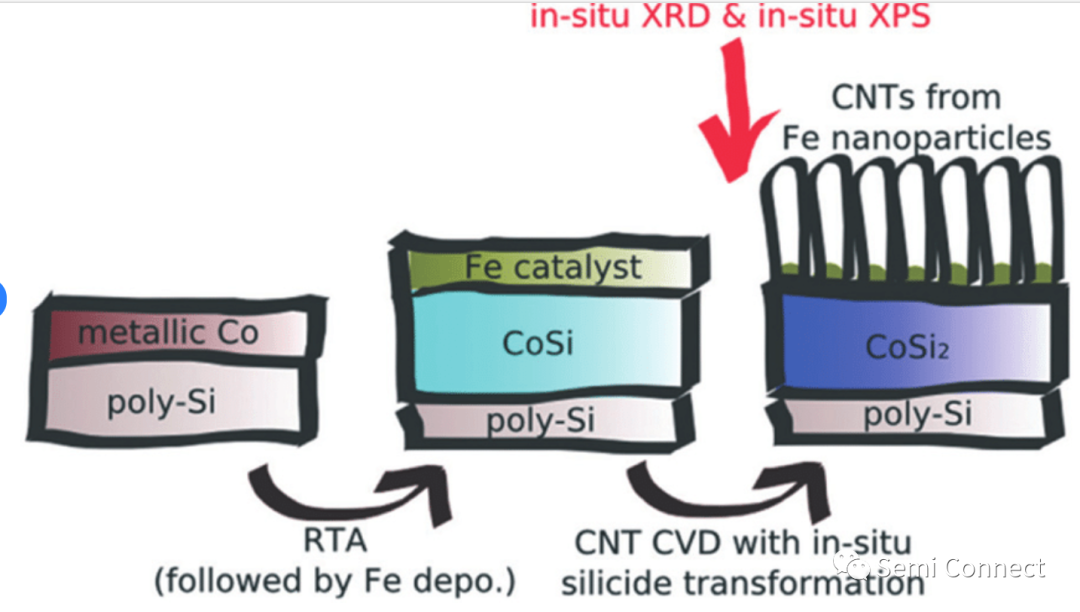

(2)钴硅化物CoSi(x)工艺:钴硅化物形成过程中所需的退火温度比钛硅化物的明显降低,这表示该工艺具有较少的热预算,因此 CoSi(x)可作为 TiSi2的替代品。

当芯片技术推进到 65nm/ 45nmn 节点以下时,线宽效应又显现出来。

另外,当CMOS 技术进入65nm/ 45nm 及更小节点以后,有源区结深越来越浅,而钴硅化物在形成过程中需消耗较多的高掺杂硅;同时对硅化物过程中的热预算有更苛刻的要求,而 CoSi2需要 700℃ 以上的二次退火,因此产业界寻找了具有更低热预算的替代者———镍硅化物。

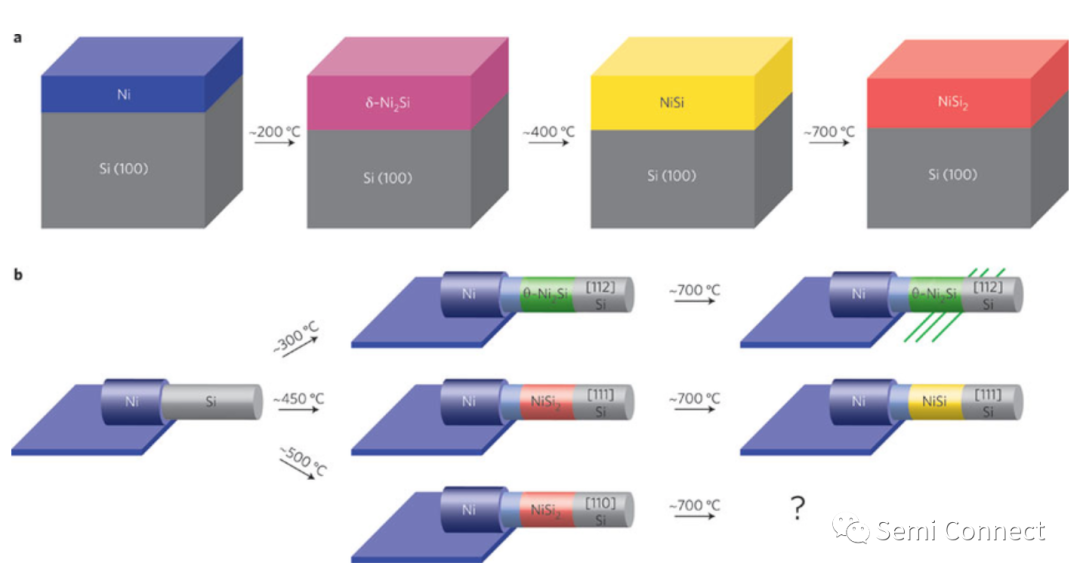

(3) 镍硅化物 NiSi 工艺:对于 65/45nm 及以下技术节点的芯片制造工艺,为了突破钴硅化物的工艺限制,产业界开发了镍硅化物(NiSi),作为替代物,其主要优势在于,即使镍硅化物工艺沿用了两步退火,但其退火温度比钴硅化物工艺明显降低(通常小于 600℃),且采用较短的退火时间,可以有效地抑制离子的扩散,降低对器件超浅结的破坏性。

镍硅化物的第1次退火多采用尖峰退火(Spike Anneal)或激光退火(Laser Anneal),此类退火方式的升/降温时间很短,且不再需要保持峰值温度的时间,缩短了总退火时间,因此掺杂离子在硅化物形成过程中的扩散被有效遏制,保持了原有的掺杂剖面。

除了上述3种硅化物工艺,Ti的低温硅化物在 14nm 及以下节点被采用,可显著降低接触电阻和减小漏电。这种Ti-Si 化合物不同于传统的 TiSi2,其本身的电阻率并不比 NiSi 的低,但是通过改变与硅接触的肖特基势垒,可有效降低其接触电阻。

审核编辑:刘清

-

串联电阻

+关注

关注

1文章

190浏览量

14759 -

CVD

+关注

关注

1文章

72浏览量

10723 -

集成电路芯片

+关注

关注

0文章

62浏览量

9488

原文标题:硅化物工艺(Silicidation)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成电路芯片制造中的3种硅化物工艺介绍

集成电路芯片制造中的3种硅化物工艺介绍

评论