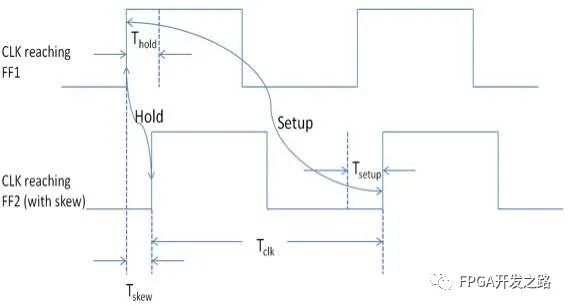

做数字电路设计的可能都见过图一所示的setup和hold时间检查,从图中可以明显看出,setup time检查下一个沿,而hold time检查同一个沿。那么这是为什么呢 ?

图1

数字电路的工作原理

以数字电路设计常见的状态机为例,下一个状态的值总是由当前状态加一些判断条件决定。为了保证下一个状态值的正确,新的状态值要在下一个时钟沿被正确采样,同时不能被当前时钟沿采样。

因此,setup time 的检查是为了保证数据在下一个时钟沿被正确采样,而 hold time 的检查是保证数据不被当前沿采样或破坏,满足了这两点,数字电路便能正常工作。

Hold Time Violation

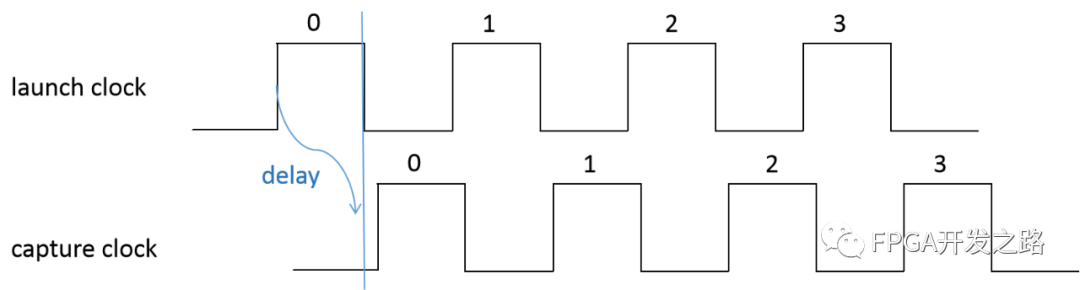

考虑一个两级移位寄存器,其launch clock 和 capture clock如图2所示。可以看到clock skew非常大,大于半个时钟周期。假设数据的延迟小于半个时钟周期,那么 hold time 的检查公式必然不满足, 即 Tcq + Tcomb < Tclk_skew + Thold。

对于这个两级移位寄存器,我们希望的值是 00(cycle0), 01(cycle1), 10(cycle2),00(cycle3)。但是由于第二级寄存器有hold time violation,数据在当前沿就被采样,那么我们实际看到的值为 00(cycle0),11(cycle1),00(cycle2),00(cycle3),完全是错误的结果。

图2

时序违反一定会有亚稳态发生吗

不一定。寄存器进入亚稳态有两个前提条件,一是数据要发生变化,二是数据的变化要发生在setup time和hold time限制的范围内。以上述图2为例,假设数据的变化没有出现在setup和hold time限制的范围内,尽管是有hold time violation,也是没有亚稳态发生的。

-

寄存器

+关注

关注

31文章

5389浏览量

121812 -

数字电路

+关注

关注

193文章

1631浏览量

81039 -

Setup

+关注

关注

0文章

30浏览量

12084

原文标题:为什么setup检查下一个沿而hold检查当前沿

文章出处:【微信号:FPGA开发之路,微信公众号:FPGA开发之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPC检查,FPC检查是什么意思

Setup/Hold Time Problem

解释下setup和hold time

什么是Setup和Hold时间

建立时间和保持时间(setup time 和 hold time)

技术研发是华为基石 华为下一个研究前沿是AI

关于FPGA的五个基本概念

Verilog中四个基础的时序分析

5个FPGA基本概念问答

通过解剖一个边沿触发器简要说明setup和hold产生原因

为什么setup检查下一个沿而hold检查当前沿

为什么setup检查下一个沿而hold检查当前沿

评论