在这个由两部分组成的系列的第 1 部分中,我们讨论了复杂 SoC 和系统设计中对早期功耗分析的需求,并介绍了 VisualSim 图形建模工具作为全面的能源仿真解决方案。在第 2 部分中,我们将展示 VisualSim 在多核嵌入式环境中预测和表达多个场景(偏移并发任务;比较 1 GHz 的单核与 250 MHz 的四个核;动态电压频率缩放 (DVFS)和功率门控)的功率值时的性能。

对新状态的更改可以是开始新的执行、在一段时间不活动后进入深度睡眠、执行低优先级与高优先级用例,以及内存激活和刷新等特定条件。功率表达式值必须与时钟速度和温度等时序属性同步变化。

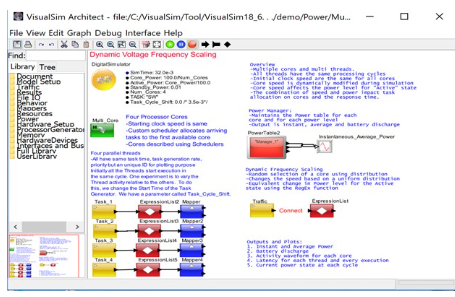

系统级功耗探索可以评估各种功耗降低和低功耗技术的优点和节省的能源。在这里,我们将讨论这些技术,并使用 VisualSim 中的模拟模型解释它们的影响。出于本研究的目的,我们使用四核处理器、调度程序代替 RTOS、四个并发线程以及按顺序触发处理资源上的线程的中断。我们已经针对内核上的可变时钟速度、1 到 4 之间的可变内核数以及线程触发之间的偏移对模型进行了参数化。此外,我们还集成了电压和时钟速度动态变化的逻辑。

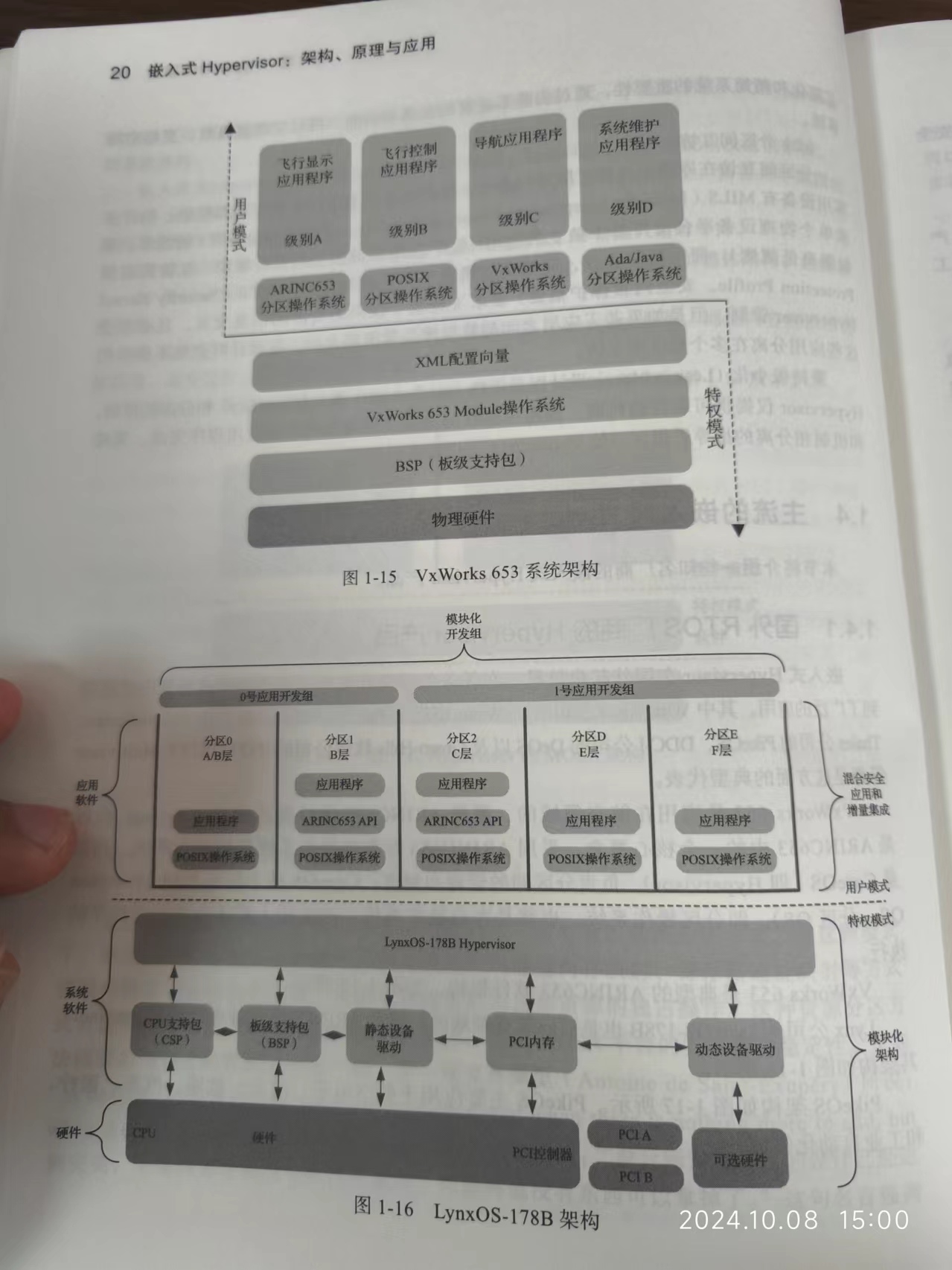

与此描述相关的框图如图 2 所示。

图2.多核架构和四个并发线程的系统级框图

进行以下实验,我们查看每个场景的延迟和功耗。

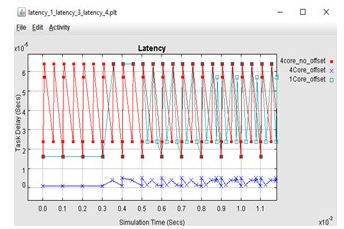

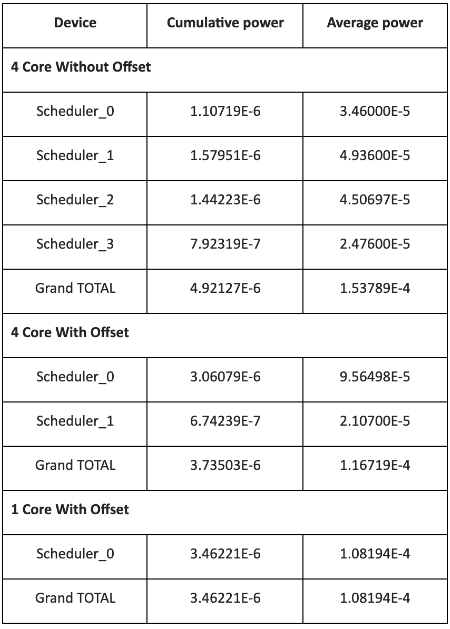

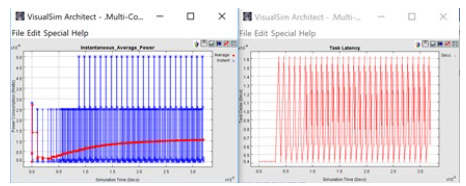

偏移并发任务:有四个任务,默认情况下,这些任务是同时触发的。在这个实验中,我们将每个任务移动了 3.5 毫秒。这样,任务就不会同时启动。如图3所示,这种方法降低了功耗尖峰。最大尖峰从 1.0mW 到 7.5mW,节省 25%。从图 4 可以看出,延迟确实从 7ms 降低到 0.5ms,这是一个显著的改进。从图 3 和表 1 中得出的有趣推论是,所有四个内核都不再被利用,并且处理资源的任务请求中只有偶尔的重叠。对平均功耗没有影响。

比较运行在 1 GHz 的单核和运行在 250 MHz 的四个内核:在这个实验中,我们将所有任务都定位在一个以 1GHz 速度运行的单个内核上。我们使用线程的偏移量。图3的结果显示,瞬时功率和平均功率均显著降低。从图 4 中我们可以看到延迟图没有显著影响。可以看到,峰值功率与1.0mW的非失调值相同,但平均功率减少了一半,为0.15mW。这是因为处理速度存在相当大的浪费。

图3.LHS 显示随时间推移的平均功率/RHS 显示随时间变化的即时功率

图4.一段时间内的延迟

表 1.上述实验的累积和平均功效

任务中具有偏移的一个内核的累积和平均功耗小于有偏移和不带偏移的 4 个内核。

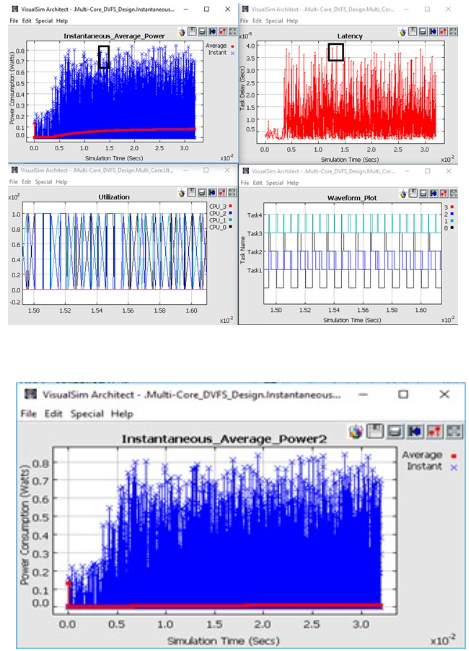

动态电压频率调节 (DVFS):这是节省功率的首选技术,通过根据任务要求改变时钟速度来完成。一个很好的例子是 x86 处理器,其额定频率为 3.2GHz,但在笔记本电脑上以 1.8 GHz 运行。使用原型板,当电压频繁调整时,很难预测任务的延迟。在相关模型中,我们没有实现特定的算法,并且能够看到功率和延迟在很宽的时钟速度范围内的变化。结果如图 5 所示。我们将使用四个内核和四个偏移线程进行此运行。请注意,由于时钟速度的变化,功率和延迟会波动。延迟与原始偏移版本相同。DVFS帮助我们大规模降低功耗。

从图 4 中我们可以看到,所有任务的时隙都不相同,随着传入任务的增加,时钟速度会根据需求随每个内核而变化。

图 6:通过实施电源管理降低平均功耗

强制内核在特定时间段后进入待机状态将降低功耗。从图 6 中,我们可以直观地看到,实施电源管理后功耗会降低。为了扩展DVFS示例,可以修改每个任务的开始和频率。在分析生成的统计信息时,我们可以看到正在使用的内核数量减少(core_3),从而消除了额外的待机功率并减少了功耗。如您所见,同时探索电源选项和软件调度非常重要。这将确保所需的响应时间,同时减少功耗。

功率门控:这是在一段时间不活动后将处理单元移动到较低功率状态的过程。一个常见的例子是笔记本电脑从活动到待机再到睡眠和休眠。在此模型中,我们将功率门控状态机逻辑添加到电源表中。我们将空闲延迟设置为 10us,将转换时间设置为 1 us。设备在待机状态下停留的时间较短。从图 6 中,我们可以看到,只要内核处于非活动状态,内核的状态就会从待机变为空闲。转换时间对延迟的影响最小到零。

图 6:电源门控,当内核处于非活动状态 0.1ms 时,内核从待机状态移动到空闲状态,转换时间为 1.0us

结论

系统级仿真可用于半导体级和系统级的广泛功率分析。将功率探索与性能研究结合使用可确保权衡同时进行,从而确保更高质量的产品。许多功耗研究可以在产品实施之前在系统级完成,并消除集成过程中的所有意外。

这项研究的一个附带好处是,热和机械工程师可以获得经过充分验证的数据,而不是近似的最佳判断信息。VisualSim 等软件工具将性能和功耗分析集成到单个系统级模型中,有助于更快地构建模型,使用较小的模型集减少模型维护,并在设计周期的早期进行更高质量的探索。此外,这些系统级工具在设计中比以前更早地推动探索:

每个任务中偏移的含义可降低功耗和延迟

减少内核数量并提高处理器速度可显著降低功耗

根据任务要求改变内核的时钟速度是降低系统功耗的最佳方法

使内核在非活动期间空闲,减少系统中的电源浪费

审核编辑:郭婷

-

嵌入式

+关注

关注

5076文章

19049浏览量

303926 -

soc

+关注

关注

38文章

4133浏览量

218002 -

RTOS

+关注

关注

22文章

809浏览量

119498

发布评论请先 登录

相关推荐

什么是嵌入式?一文读懂嵌入式主板

【「嵌入式Hypervisor:架构、原理与应用」阅读体验】+ Hypervisor应用场景调研

【「嵌入式Hypervisor:架构、原理与应用」阅读体验】+第7-8章学习心得

嵌入式Hypervisor:架构、原理与应用 阅读体验 +Hypervisor基础概念

嵌入式系统的未来趋势有哪些?

机器视觉在嵌入式中的应用

嵌入式系统怎么学?

一文解析嵌入式多核异构方案,东胜物联RK3588多核异构核心板系列一览

VisualSim在多核嵌入式环境中预测和表达多个场景展示

VisualSim在多核嵌入式环境中预测和表达多个场景展示

评论