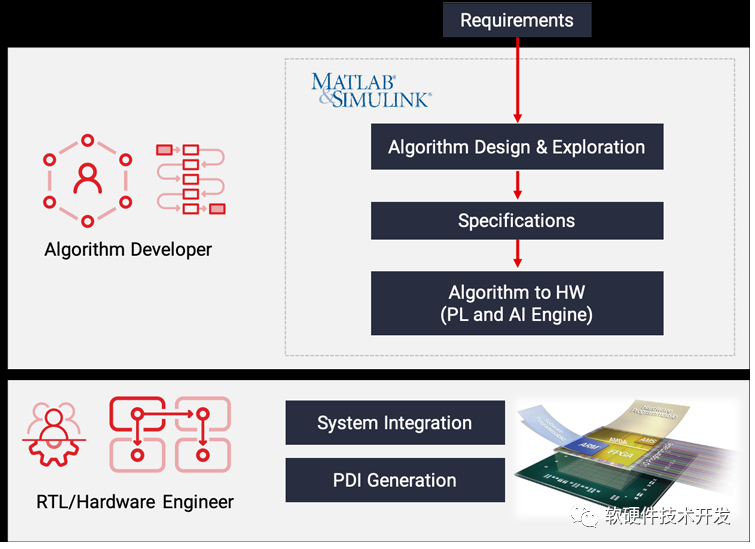

Vitis Model Composer是一个基于模型的设计工具,可在MATLAB和 Simulink 环境中进行快速设计,可通过自动代码生成在FPGA上加速投产进程。

设计的DSP算法可使用高层次性能优化模块对其进行迭代,同时还可以通过系统级仿真验证功能正确性。Vitis Model Composer可通过自动优化将设计转换为生产质量级实现方案。该工具提供一个具有200多个HDL、HLS和AI引擎模块的库,用于在FPGA上设计并实现算法。

此外,它还允许将自定义HDL、HLS和AI引擎代码按模块导入工具。Vitis Model Composer包含原System Generator的所有功能性。

分析、调试与可视化

使用 MATLAB 和 Simulink 环境分析并显示设计:

直接从 Simulink 库浏览器使用优化的 AI 引擎、HLS 和 HDL 模块

按模块导入自定义 AI 引擎、HLS 和 HDL 代码

在 Simulink 环境中运行快速仿真

将结果与 MATLAB 和 Simulink 环境中的黄金参考进行比较

利用中间信号进行调试,并让设计可视化

协同仿真异构系统

直接从该库浏览器使用优化的 AI 引擎/HLS/自适应引擎,或按模块形式导入代码

将 AI 引擎阵列与 HLS 内核模块或 HDL 模块无缝连接

代码生成

从设计生成代码,以提升生产力:

生成带有约束的图形代码

生成 RTL (Verilog/VHDL)

使用插入的程序生成优化的 HLS 代码

生成测试工作台

硬件设计验证

验证硬件设计,简单易用:

生成数据移动器、处理系统代码与配置文件

生成构建硬件设计所需的 make 文件

点击按钮,将设计移动到硬件中

支持版本说明

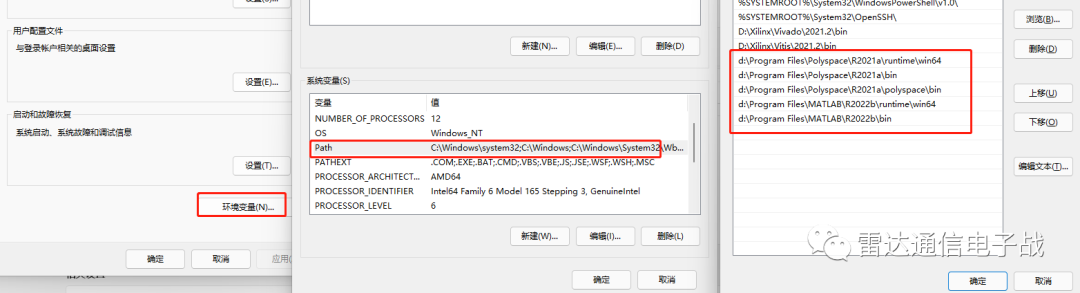

Vitis2021.2支持的Matlab版本有:R2020a,R2020b,R2021a

Vitis2022.2支持的Matlab版本有:R2021a,R2021b

若你安装了多个matlab版本,需要在环境变量的path中将支持的版本移到前面,这样打开vitis model composer时会自动打开支持的matlab版本,否则会显示该版本不支持。例如:

审核编辑:郭婷

-

FPGA

+关注

关注

1630文章

21759浏览量

604379 -

matlab

+关注

关注

185文章

2979浏览量

230662 -

编译器

+关注

关注

1文章

1636浏览量

49175

原文标题:基于vitis的模型编译器,联合Matlab/Simulink和FPGA

文章出处:【微信号:雷达通信电子战,微信公众号:雷达通信电子战】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于vitis的模型编译器在FPGA上加速投产进程

基于vitis的模型编译器在FPGA上加速投产进程

评论