本文主要阐述了在电力电子电路应用中,为什么需要驱动芯片并联使用,芯片能够并联使用应具备什么特征,以及驱动芯片并联使用应注意的问题点。

01

驱动芯片与功率管的配合

功率器件在工业、能源、汽车等应用中被广泛的使用以实现各种的功率变换,同时随着社会的迅速发展,功率变换的功率等级也越来越高。在大功率的功率因数校正电路 (PFC),低压大电流的同步整流电路中, 往往需要多个功率管并联以满足电路功率输出的需求。

多个功率管并联,导致功率管的QGC,QGE变大,若选用驱动芯片的驱动电流较小,则功率管开通时间很长,此时会导致功率管损耗很大,发热严重。驱动输出进行并联来驱动功率管是一种解决方案。

02

驱动芯片并联使用

如上述所,当功率管的门极电荷比较大,而驱动芯片能力不足时,为了选择合适的开关速度和性能,需要将驱动芯片输出端并联使用。

但驱动芯片并联时,对驱动芯片要求较高,并不是所有的驱动芯片都适合并联使用。

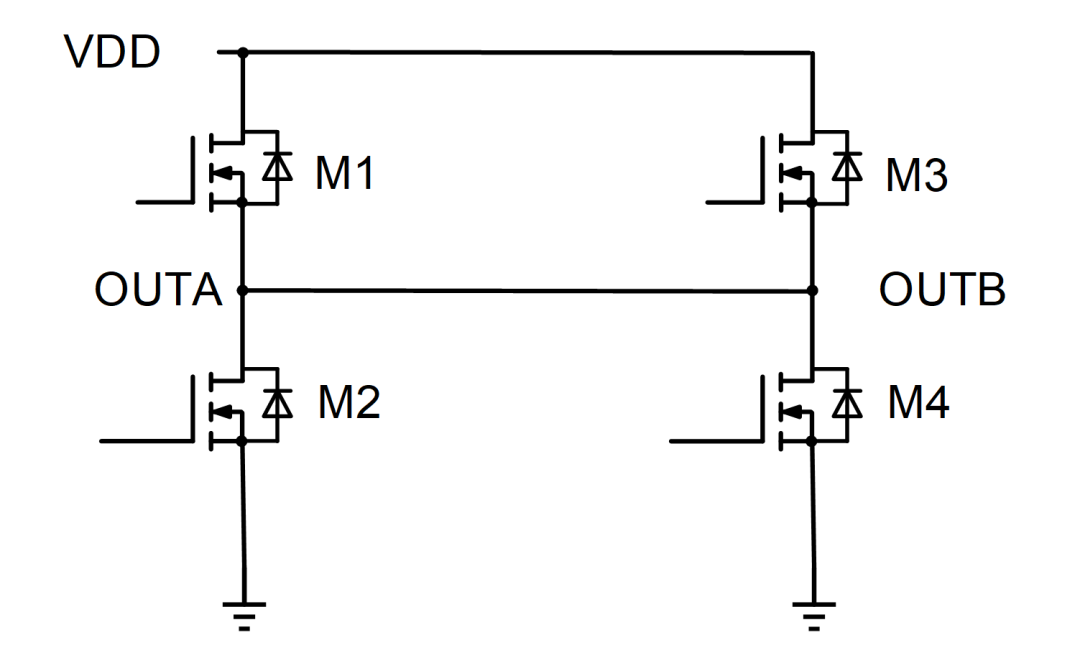

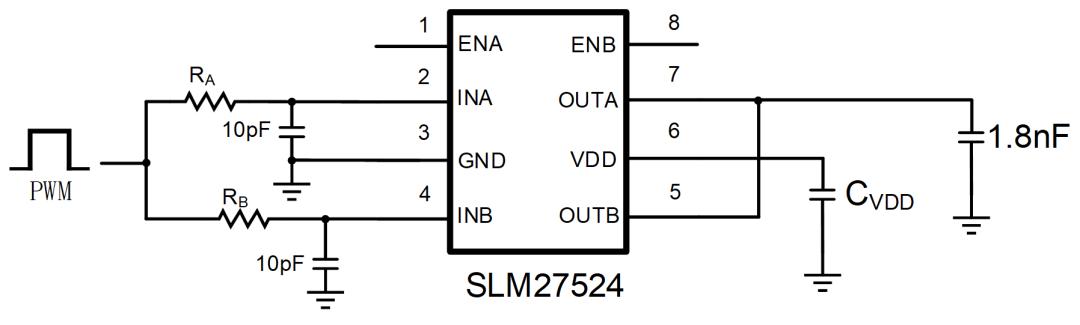

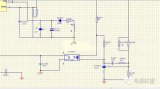

图1.显示了驱动芯片并联使用时的示意图。由于是并联使用,要求内部的MOSFET M1与M3,M2与M4同时开通,同时关断,否则OUTA与OUTB之间必然存在电位差,导致M1与M4或者M2与M3同时导通,从而导致共通的现象而损坏驱动芯片。

图 1. 驱动芯片并联使用示意图

因此,在驱动芯片并联的应用中需要特别关注以下几点:

(1)驱动芯片本身的对称问题。两个驱动通道的参数要一致,每路驱动的输入到输出的延时、输入的翻转电平以及输出的上升、下降时间要一致。

(2)两路输入信号的短接点要尽量靠近芯片的管脚,并且输入信号要有快速的dv/dt。

(3)芯片的外围应用电路上,可以在外部增加一个电阻,用来限制直通电流。

下面以SLM27524芯片为例来说明驱动并联应用中要注意的一些问题。

03

驱动芯片的一致性

驱动芯片并联对芯片本身的一致性是有要求的,如果两路驱动的一致性不好,在并联时会导致驱动芯片的损坏。SLM27524在设计的时候已经考虑了这种并联应用的需求,因此在两路驱动的延时上做了比较好的匹配。

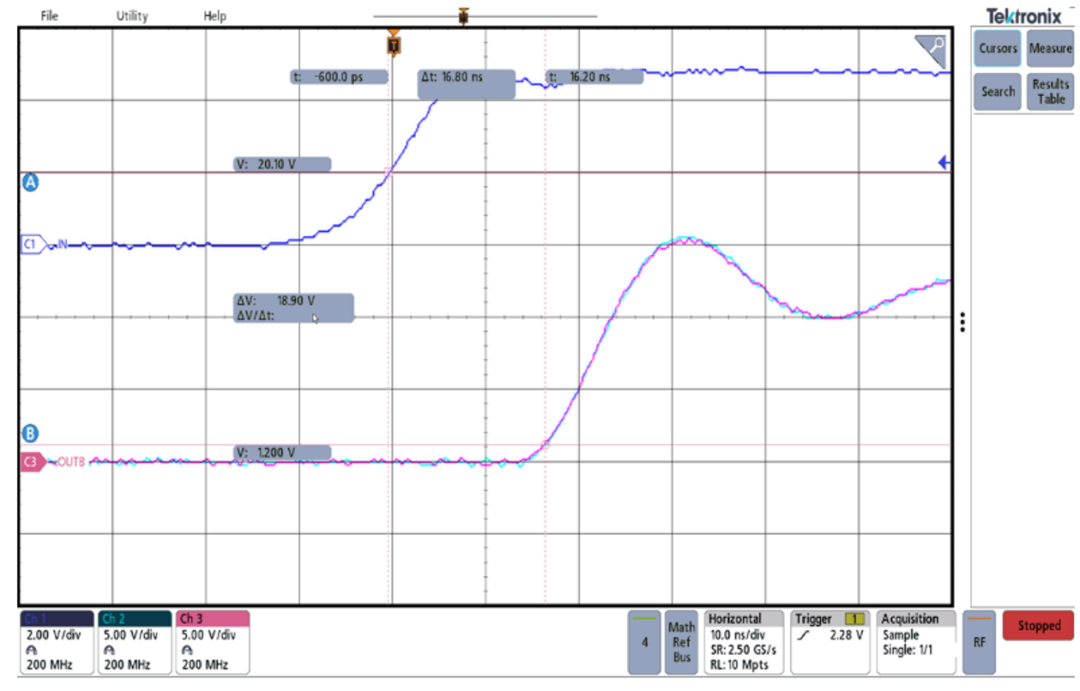

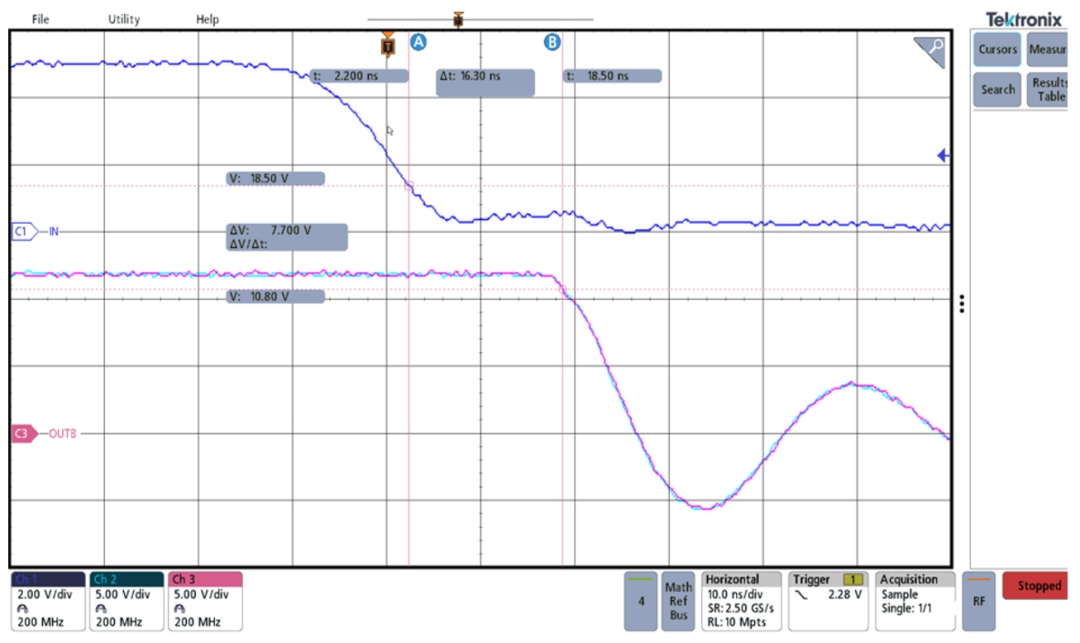

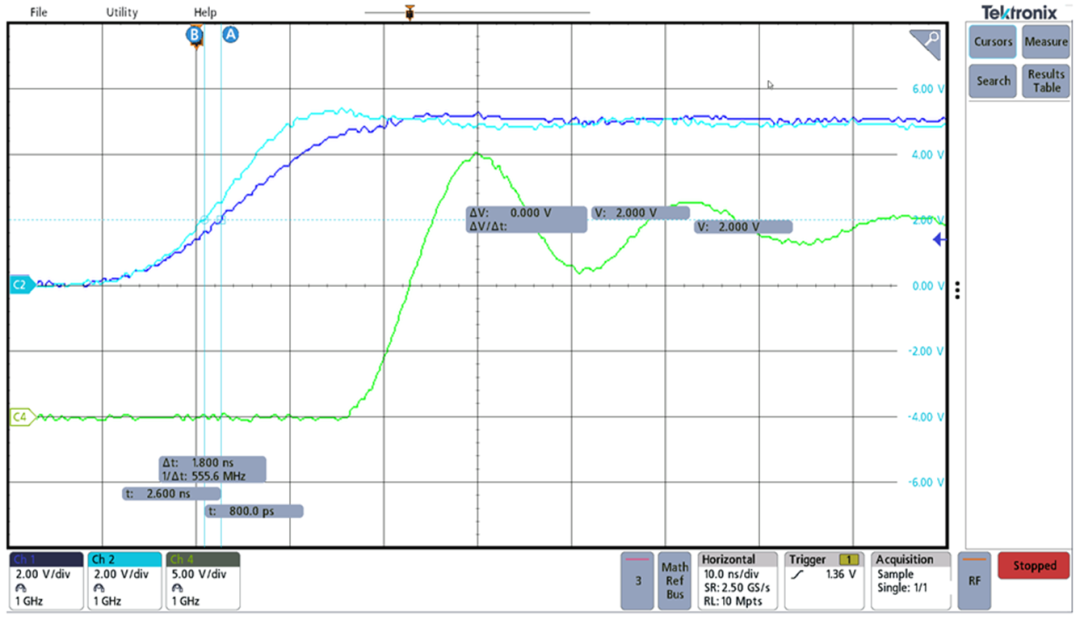

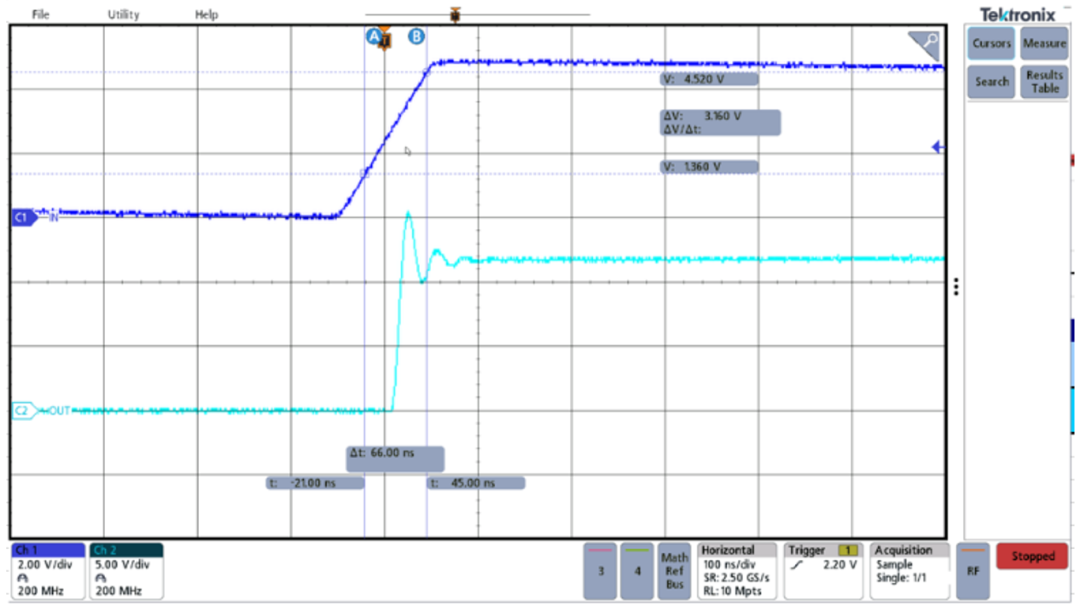

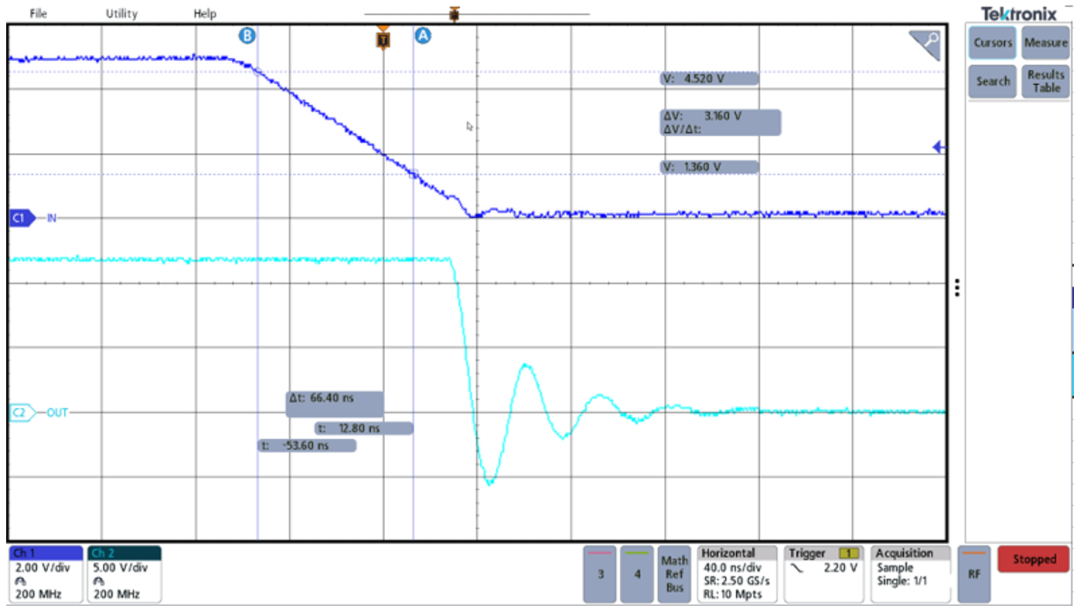

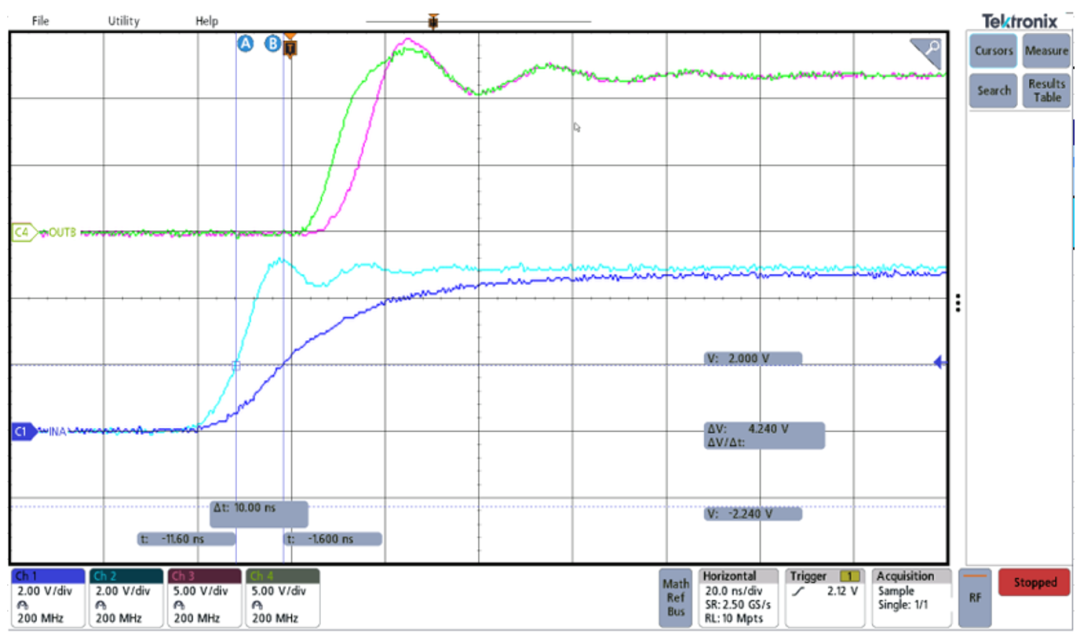

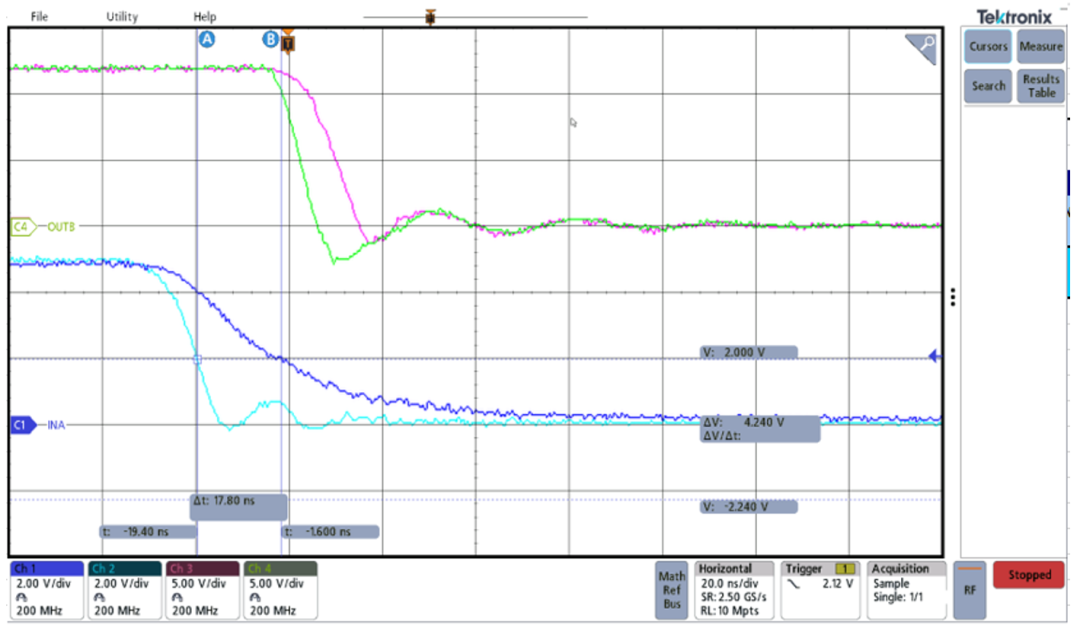

图2和图3显示了SLM27524在给同一个输入信号时,两路驱动输出在开通、关断时的波形。从波形测试上看,SLM27524的两路驱动在开通延时、关断延时、上升时间和下降时间上都有很好的一致性。

图 2. SLM27524通道开通时的波形

CH1: 驱动输人IN 丨 CH2: 驱动输出OUTA

CH3: 驱动输出OUTB

图 3. SLM27524通道关断时的波形

CH1: 驱动输人IN 丨 CH2: 驱动输出OUTA

CH3: 驱动输出OUTB

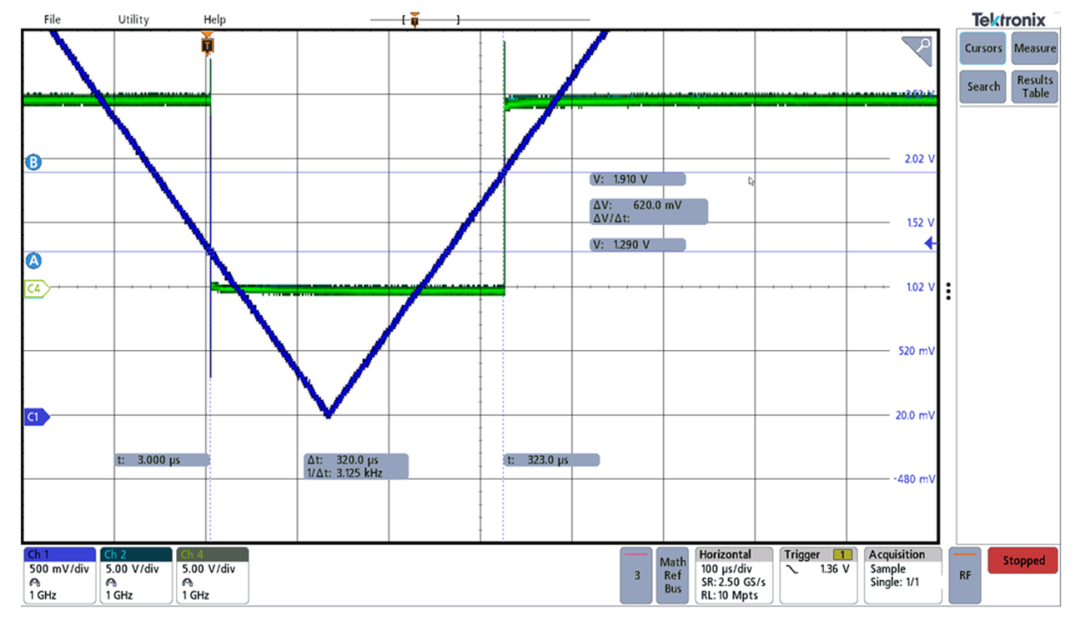

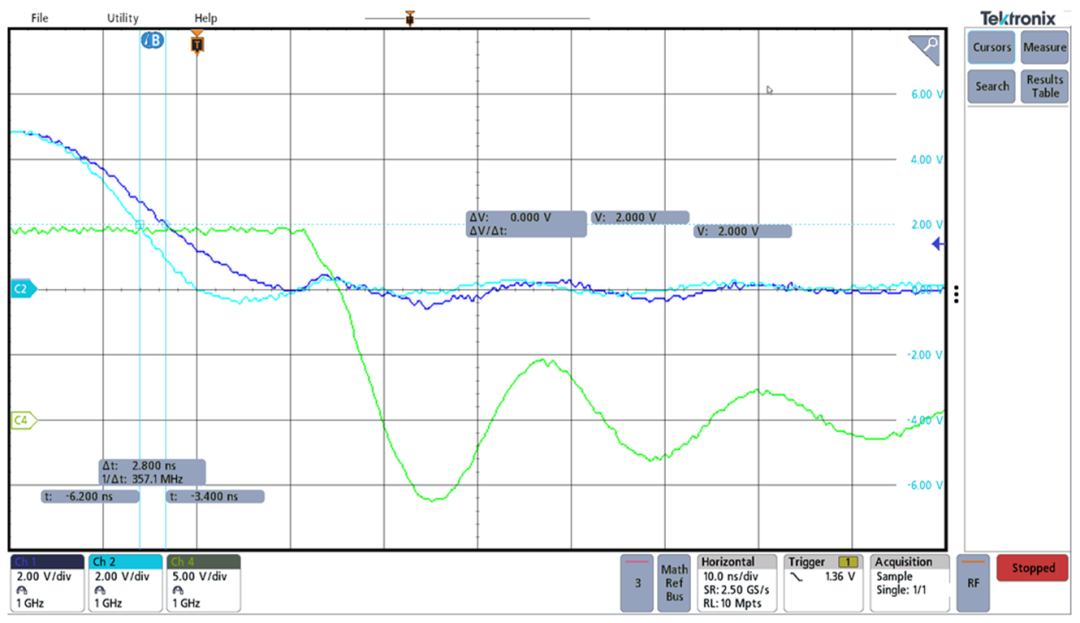

图4显示了SLM27524两个通道的输入阈值。从测试的波形上看,两个通道的输入阈值是一致的。

图 4. SLM27524 输入阈值门限波形

CH1: 驱动输人IN 丨 CH2: 驱动输出OUTA

CH4: 驱动输出OUTB

为了验证SLM27524两个通道直接并联应用的有效性,人为在两路输入信号上加入延时,并按下图5进行试验。当改变电阻RA、RB的阻值时,就改变了通道A、B之间的输入时间差。

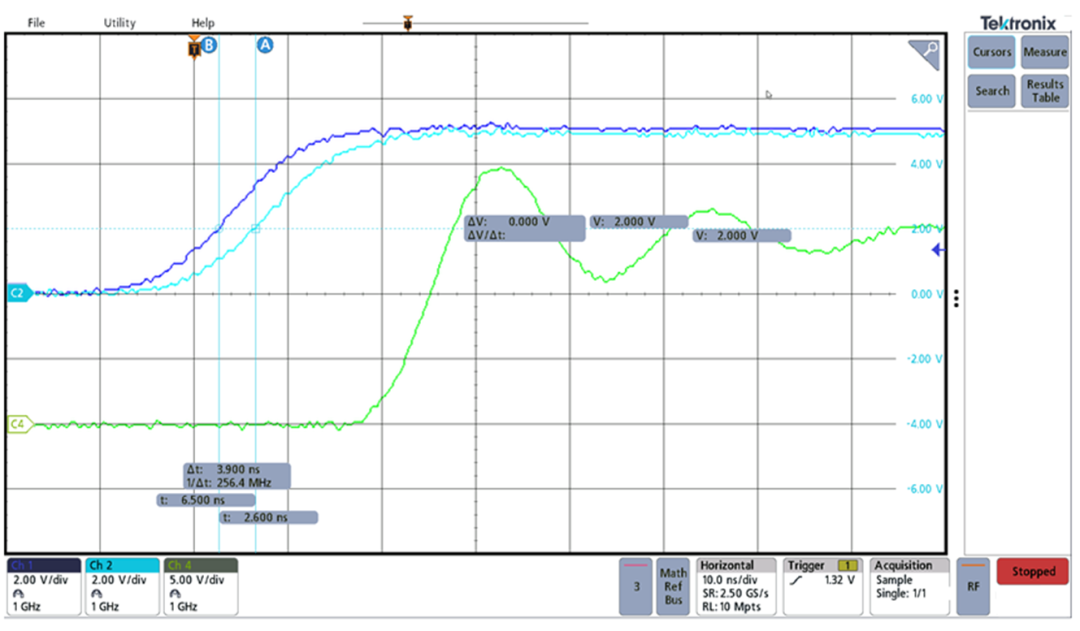

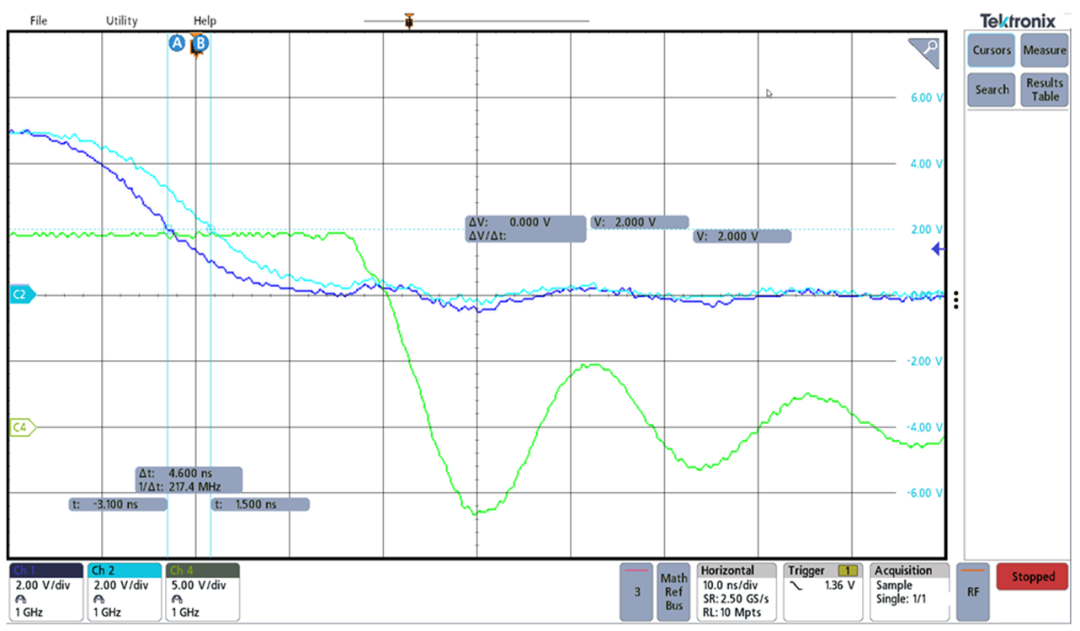

图6到图9显示了通道A和通道B在不同的输入延时情况下的输出波形。

在一定输入延时差范围内,无论是INA超前还是滞后INB,芯片直接并联仍然正常输出波形。这说明SLM27524具有较强的鲁棒性,能够容忍一定程度的输入信号延时差。

图 5. SLM27524并联鲁棒试验电路

图 6. SLM27524 INA超前INB 3.9ns并联波形

CH1: 驱动输人INA 丨 CH2: 驱动输入INB

CH4:驱动输出OUT

图 7. SLM27524 INA超前INB 4.6ns并联波形

CH1: 驱动输人INA 丨 CH2: 驱动输入INB

CH4:驱动输出OUT

图 8. SLM27524 INA滞后INB 1.8ns并联波形

CH1: 驱动输人INA 丨 CH2: 驱动输入INB

CH4:驱动输出OUT

图 9. SLM27524 INA滞后INB 2.8ns并联波形

CH1: 驱动输人INA 丨 CH2: 驱动输入INB

CH4:驱动输出OUT

04

驱动芯片并联应用技巧

在驱动芯片并联时,外部的一些应用条件和应用技巧也同样的重要。

首先,对于输入信号的处理,在PCB上应尽量靠近芯片管脚处进行并联。如果离芯片管脚距离较远处并联后再分开到各个输入管脚,那就容易存在PCB走线上的延时误差。

其次,输入通道的门限阈值不完全一致时,会导致输出延时不一样。为了降低此影响,需增强输入信号的上升下降速度。在使用SLM27524时,推荐输入信号变化速度不低于50V/us.

图 10. SLM27524 47V/us上升波形

CH1: 驱动输人IN 丨 CH2:驱动输出OUT

图 11. SLM27524 47V/us下降波形

CH1: 驱动输人IN 丨 CH2:驱动输出OUT

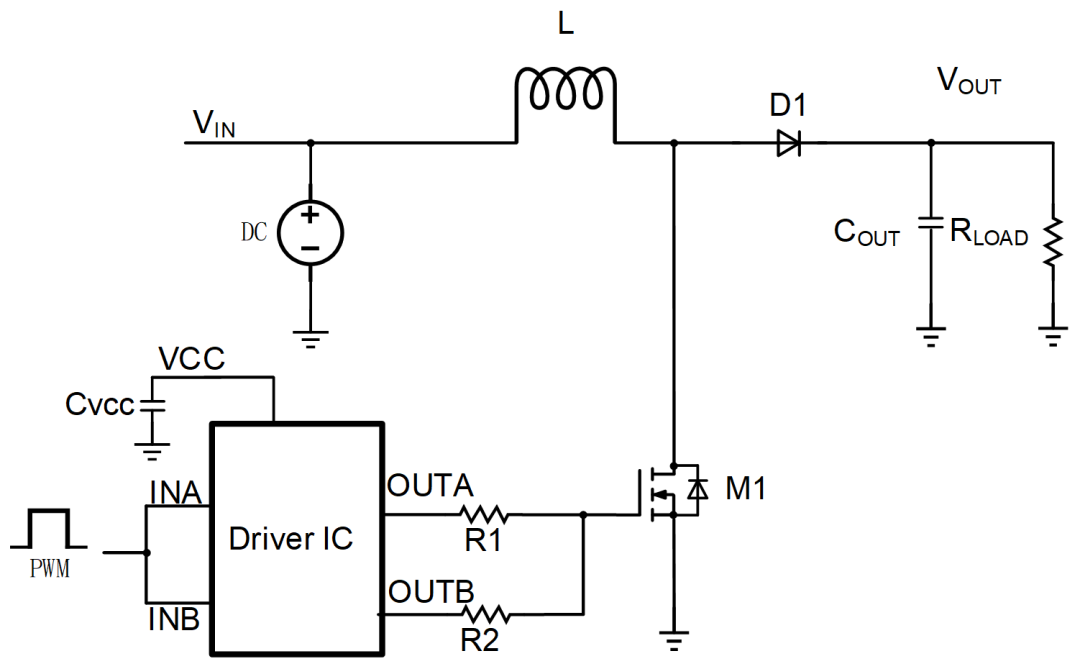

最后,为了更好的使芯片在应用端使用,推荐在输出端之间串联电阻后再进行并联,按如图12所示。如果需要OUTA,OUTB进行直接并联,则R1=R2=0。另外可以调整R1,R2参数,限制直通时电流值,保护驱动控制芯片。图13与图14显示了INA,INB之间有17.8ns的延时,如果OUTA,OUTB直接并联,芯片可能会烧毁,但OUTA,OUTB之间串接5.1Ω电阻,此时能够保证芯片正常工作而不损坏。

图 12. 芯片输出端增加输出电阻

图 13. SLM27524 INA滞后INB

且OUTA与OUTB串接5.1Ω并联波形

CH1: 输人INA 丨 CH2: 输入INB

CH3:输出OUTA 丨 CH4:输出OUTB

图 14. SLM27524 INA超前INB

且OUTA与OUTB串接5.1Ω并联波形

CH1: 输人INA 丨 CH2: 输入INB

CH3:输出OUTA 丨 CH4:输出OUTB

05

测试总结

综上所述,在采用驱动芯片并联去驱动功率管的应用中,除了注意PCB布线布局外,对芯片对称性有较高要求;另外增大输入信号变化斜率以及在芯片输出端串接电阻,可以增强输出并联的可靠性。

审核编辑:刘清

-

PFC

+关注

关注

47文章

989浏览量

106581 -

PCB布线

+关注

关注

21文章

463浏览量

42191 -

校正电路

+关注

关注

2文章

31浏览量

27425 -

电子电路

+关注

关注

78文章

1231浏览量

67118 -

驱动芯片

+关注

关注

13文章

1312浏览量

55082

原文标题:应用笔记 丨 驱动的并联使用

文章出处:【微信号:数明半导体,微信公众号:数明半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在电力电子电路应用中为什么需要驱动芯片并联使用呢

在电力电子电路应用中为什么需要驱动芯片并联使用呢

评论