工业、科学和医疗射频(ISM-RF)产品的无数应用案例表明,这些产品的印制板(PCB)布局很容易出现各种缺陷。人们时常发现相同IC安装到两块不同电路板上,所表现的性能指标会有显著差异。工作条件、谐波辐射、抗干扰能力,以及启动时间等等诸多因素的变化,都能说明电路板布局在一款成功设计中的重要性。

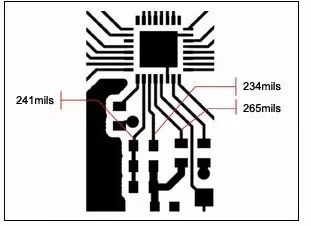

本文罗列了各种不同的设计疏忽,探讨了每种失误导致电路故障的原因,并给出了如何避免这些设计缺陷的建议。本文以FR-4电介质、厚度 0.0625in的双层PCB为例,电路板底层接地。工作频率介于315MHz到915MHz之间的不同频段,Tx和Rx功率介于-120dBm 至+13dBm之间。表1列出了一些可能出现的PCB布局问题、原因及其影响。 表1. 典型的PCB布局问题和影响

| Problem | Cause | Effect |

| LNA/tank circuit arrangement (receiver) | Inductor orientation | RF feedthrough |

| Degeneration/π-network arrangement (transmitter) | Inductor orientation | RF feedthrough |

| Shared ground vias between legs ofπnetwork | Via parasitics | Feedthrough, RF leakage |

| Shared ground vias between receiver blocks | Via parasitics | Crosstalk, RF feedthrough, RF leakage |

| Long traces for decoupling capacitors | Higher-impedance connections | Reduced decoupling |

| Wide component placement | Increased parasitics, ground loops | Detuning, crosstalk, feedthrough |

| Colinear traces in the transmitter circuit | Filter bypassing, i.e.,power amplifier(PA) directly to antenna | Harmonics radiation |

| Top-layer copper pours | Parasitic coupling | RF leakage, RF interference |

| Discontinuous ground plane | Return current concentration | Crosstalk, feedthrough |

| Crystal connection trace length | Excess capacitance | LO frequency pulling |

| Crystal connection trace separation | Excess capacitance | LO frequency pulling |

| Ground plane under crystal pads | Excess capacitance | LO frequency pulling |

| Planar PCB trace inductors | Poor inductance control |

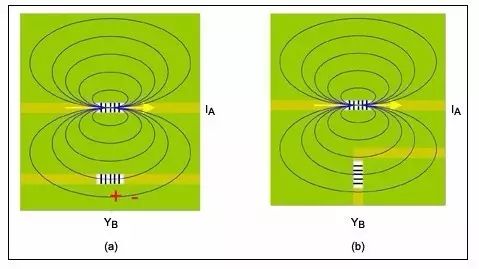

其中大多数问题源于少数几个常见原因,我们将对此逐一讨论。 电感方向当两个电感(甚至是两条PCB走线)彼此靠近时,将会产生互感。第一个电路中的电流所产生的磁场会对第二个电路中的电流产生激励(图1)。这一过程与变压器初级、次级线圈之间的相互影响类似。当两个电流通过磁场相互作用时,所产生的电压由互感LM决定:  式中,YB是向电路B注入的误差电压,IA是在电路A作用的电流1。LM对电路间距、电感环路面积(即磁通量)以及环路方向非常敏感。因此,紧凑的电路布局和降低耦合之间的最佳平衡是正确排列所有电感的方向。

式中,YB是向电路B注入的误差电压,IA是在电路A作用的电流1。LM对电路间距、电感环路面积(即磁通量)以及环路方向非常敏感。因此,紧凑的电路布局和降低耦合之间的最佳平衡是正确排列所有电感的方向。

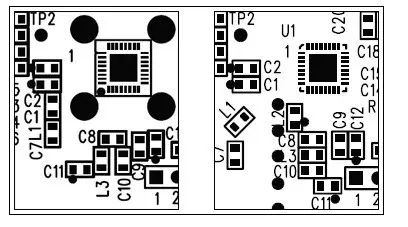

图1. 由磁力线可以看出互感与电感排列方向有关 对电路B的方向进行调整,使其电流环路平行于电路A的磁力线。为达到这一目的,尽量使电感互相垂直,请参考低功率FSK超外差接收机评估 (EV)板(MAX7042EVKIT)的电路布局(图2)。 该电路板上的三个电感(L3、L1和L2)距离非常近,将其方向排列为0°、45°和 90°,有助于降低彼此之间的互感。

图2. 图中所示为两种不同的PCB布局 其中一种布局的元件排列方向不合理(L1和L3),另一种的方向排列则更为合适。 综上所述,应遵循以下原则:

电感间距应尽可能远。

电感排列方向成直角,使电感之间的串扰降至最小。

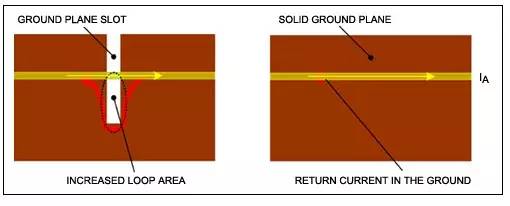

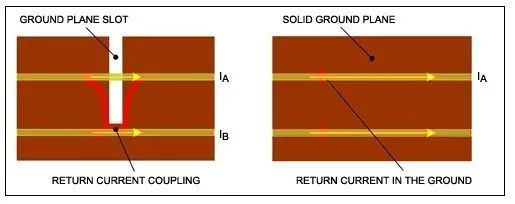

引线耦合如同电感排列方向会影响磁场耦合一样,如果引线彼此过于靠近,也会影响耦合。这种布局问题也会产生所谓的互感。RF电路最关心问题之一即为系统敏感部件的走线,例如输入匹配网络、接收器的谐振槽路、发送器的天线匹配网络等。 返回电流通路须尽可能靠近主电流通道,将辐射磁场降至最小。这种布局有助于减小电流环路面积。返回电流的理想低阻通路通常是引线下方的接地 区域—将环路面积有效限制在电介质厚度乘以引线长度的区域。 但是,如果接地区域被分割开,则会增大环路面积(图3)。对于穿过分割区域的引线,返回电流将 被强制通过高阻通路,大大提高了电流环路面积。这种布局还使电路引线更容易受互感的影响。

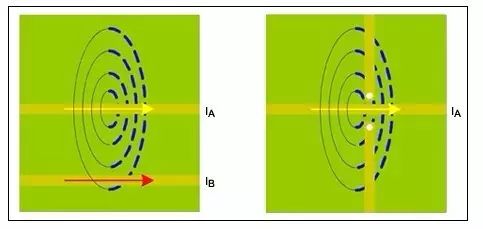

图3. 完整的大面积接地有助于改善系统性能 对于一个实际电感,引线方向对磁场耦合的影响也很大。如果敏感电路的引线必须彼此靠近,最好将引线方向垂直排列,以降低耦合(图4)。如果无法做到垂直排列,则可考虑使用保护线。关于保护线的设计,请参考以下接地与填充处理部分。

图4. 类似于图1,表示可能存在的磁力线耦合。 综上所述,布板时应遵循以下原则:

引线下方应保证完整接地。

敏感引线应垂直排列。

如果引线必须平行排列,须确保足够的间距或采用保护线。

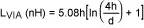

接地过孔RF电路布局的主要问题通常是电路的特征阻抗不理想,包括电路元件及其互联。引线覆铜层较薄,则等效于电感线,并与邻近的其它引线形成分布电容。引线穿过过孔时,也会表现出电感和电容特性。 过孔电容主要源于过孔焊盘侧的覆铜与地层覆铜之间构成的电容,它们之间由一个相当小的圆环隔开。另外一个影响源于金属过孔本身的圆柱。寄生电容的影响一般较小,通常只会造成高速数字信号的边沿变差(本文不对此加以讨论)。 过孔的最大影响是相应的互联方式所引起的寄生电感。因为RF PCB设计中,大多数金属过孔尺寸与集总元件的尺寸相同,可利用简单的公式估算电路过孔的影响(图5):  式中,LVIA为过孔的集总电感;h为过孔高度,单位为英寸;d为过孔直径,单位为英寸2。

式中,LVIA为过孔的集总电感;h为过孔高度,单位为英寸;d为过孔直径,单位为英寸2。

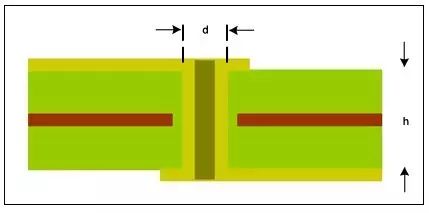

图5. PCB横截面用于估算寄生影响的过孔结构 寄生电感往往对旁路电容的连接影响很大。理想的旁路电容在电源层与地层之间提供高频短路,但是,非理想过孔则会影响地层和电源层之间的低感 通路。典型的 PCB过孔(d = 10 mil、h = 62.5 mil)大约等效于一个1.34nH电感。给定ISM-RF产品的特定工作频率,过孔会对敏感电路(例如,谐振槽路、滤波器以及匹配网络等)造成不良影响。 如果敏感电路共用过孔,例如π型网络的两个臂,则会产生其它问题。例如,放置一个等效于集总电感的理想过孔,等效原理图则与原电路设计有很大区别(图6)。与共用电流通路的串扰一样3,导致互感增大,加大串扰和馈通。

图6. 理想架构与非理想架构比较,电路中存在潜在的“信号通路” 综上所述,电路布局需要遵循以下原则:

确保对敏感区域的过孔电感建模。

滤波器或匹配网络采用独立过孔。

注意,较薄的PCB覆铜会降低过孔寄生电感的影响。

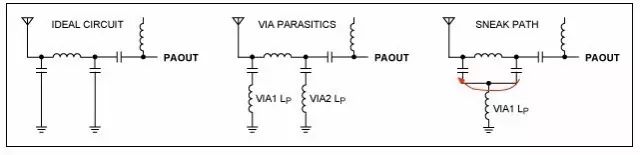

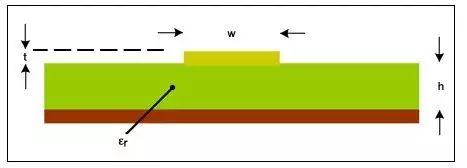

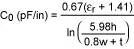

引线长度Maxim ISM-RF产品的数据资料往往建议使用尽可能短的高频输入、输出引线,从而将损耗和辐射降至最小。另一方面,这种损耗通常是由于非理想寄生参数引起的, 所以寄生电感和电容都会影响电路布局,使用尽可能短的引线有助于降低寄生参数。 通常情况下,10 mil宽、距离地层0.0625in的PCB引线,如果采用的是FR4电路板,则产生大约19nH/in的电感和大约1pF/in的分布电容。对于具有 20nH电感、3pF电容的LAN/混频器电路,电路、元器件布局非常紧凑时,会对有效元件值造成很大影响。 “Institute for Printed Circuits”中的IPC-D-317A4提供了一个行业标准方程,用于估算微带线PCB的各种阻抗参数。该文件在2003年被IPC-2251取代 5,后者为各种PCB引线提供更准确的计算方法。可以通过各种渠道获得在线计算器,其中大多数都基于IPC-2251提供的方程式。密苏里理工大学的电磁兼容性实验室提供了一个非常实用的PCB引线阻抗计算方法6。 公认的计算微带线阻抗的标准是:  式中,εr为电介质的介电常数,h为引线距离地层的高度,w为引线宽度,t为引线厚度(图7)。w/h介于0.1至2.0、εr介于1至15之间时,该公式的计算结果相当准确7。

式中,εr为电介质的介电常数,h为引线距离地层的高度,w为引线宽度,t为引线厚度(图7)。w/h介于0.1至2.0、εr介于1至15之间时,该公式的计算结果相当准确7。

图7. 该图为PCB横截面(与图5类似),表示用于计算微带线阻抗的结构 为评估引线长度的影响,确定引线寄生参数对理想电路的去谐效应更实用。本例中,我们讨论杂散电容和电感。用于微带线的特征电容标准方程为:  同理,可利用上述方程从方程式

同理,可利用上述方程从方程式 中计算得到特征电感:

中计算得到特征电感:  举例说明,假设PCB厚度为0.0625in (h = 62.5 mil),1盎司覆铜引线(t = 1.35 mil),宽度为0.01in (w = 10 mil),采用FR-4电路板。注意,FR-4的εr典型值为4.35法拉/米(F/m),但范围可从4.0F/m至4.7F/m。本例计算得到的特征值为Z0 = 134Ω,C0 = 1.04pF/in,L0 = 18.7nH/in。 对于ISM-RF设计中,电路板上布局长度为12.7mm (0.5in)的引线,可产生大约0.5pF和9.3nH的寄生参数(图8)。这一等级的寄生参数对于接收器谐振槽路的影响(LC乘积的变化),可能产生 315MHz ±2%或433.92MHz ±3.5%的变化。由于引线寄生效应所产生的附加电容和电感,使得315MHz振荡频率的峰值达到312.17MHz,433.92MHz振荡频率的峰值 达到426.61MHz。

举例说明,假设PCB厚度为0.0625in (h = 62.5 mil),1盎司覆铜引线(t = 1.35 mil),宽度为0.01in (w = 10 mil),采用FR-4电路板。注意,FR-4的εr典型值为4.35法拉/米(F/m),但范围可从4.0F/m至4.7F/m。本例计算得到的特征值为Z0 = 134Ω,C0 = 1.04pF/in,L0 = 18.7nH/in。 对于ISM-RF设计中,电路板上布局长度为12.7mm (0.5in)的引线,可产生大约0.5pF和9.3nH的寄生参数(图8)。这一等级的寄生参数对于接收器谐振槽路的影响(LC乘积的变化),可能产生 315MHz ±2%或433.92MHz ±3.5%的变化。由于引线寄生效应所产生的附加电容和电感,使得315MHz振荡频率的峰值达到312.17MHz,433.92MHz振荡频率的峰值 达到426.61MHz。

图8. 一个紧凑的PCB布局,寄生效应会对电路产生影响 另外一个例子是Maxim的超外差接收机(MAX7042)的谐振槽路,推荐使用的元件在315MHz时为1.2pF和30nH;433.92MHz时为0pF和16nH。利用方程计算谐振电路振荡频率:  评估板谐振电路应包括封装和布局的寄生效应,计算315MHz谐振频率时,寄生参数分别为7.3pF和7.5pF。注意,LC乘积表现为集总电容。 综上所述,布板须遵循以下原则:

评估板谐振电路应包括封装和布局的寄生效应,计算315MHz谐振频率时,寄生参数分别为7.3pF和7.5pF。注意,LC乘积表现为集总电容。 综上所述,布板须遵循以下原则:

保持引线长度尽可能短。

关键电路尽量靠近器件放置。

根据实际布局寄生效应对关键元件进行补偿。

少数几个常见原因4:接地与填充处理#e#

接地与填充处理接地或电源层定义了一个公共参考电压,通过低阻通路为系统的所有部件供电。按照这种方式均衡所有电场,产生良好的屏蔽机制。 直流电流总是倾向于沿着低阻通路流通。同理,高频电流也是优先流过最低电阻的通路。所以,对于地层上方的标准PCB微带线,返回电流试图流入引线正下方的接地区域。按照上述引线耦合部分所述,割断的接地区域会引入各种噪声,进而通过磁场耦合或汇聚电流而增大串扰(图9)。

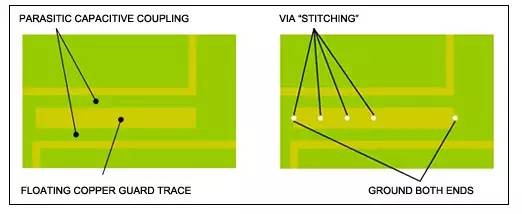

图9. 尽可能保持地层完整,否则返回电流会引起串扰 填充地也称为保护线,通常将其用于电路中很难铺设连续接地区域或需要屏蔽敏感电路的设计(图10)。通过在引线两端,或者是沿线放置接地过孔(即过孔阵列),增大屏蔽效应8。请不要将保护线与设计用来提供返回电流通路的引线相混合,这样的布局会引入串扰。

图10. RF系统设计中须避免覆铜线浮空,特别是需要铺设铜皮的情况下 覆铜区域不接地(浮空)或仅在一端接地时,会制约其有效性。有些情况下,它会形成寄生电容,改变周围布线的阻抗或在电路之间产生“潜在”通 路,从而造成不利影响。简而言之,如果在电路板上铺设了一块覆铜(非电路信号走线),来确保一致的电镀厚度。覆铜区域应避免浮空,因为它们会影响电路设 计。 最后,确保考虑天线附近任何接地区域的影响。任何单极天线都将接地区域、走线和过孔作为系统均衡的一部分,非理想均衡布线会影响天线的辐射效率和方向(辐射模板)。因此,不应将接地区域直接放置在单极PCB引线天线的下方。 综上所述,应该遵循以下原则:

尽量提供连续、低阻的接地区域。

填充线的两端接地,并尽量采用过孔阵列。

RF电路附近不要将覆铜线浮空,RF电路周围不要铺设铜皮。

如果电路板包括多个地层,信号线从一侧过度另一侧时,最好铺设一个接地过孔。

晶体电容过大寄生电容会使晶振的工作频率偏离目标值9。因此,须遵循一些常规准则,降低晶体引脚、焊盘、走线或与RF器件连接的杂散电容。 应遵循以下原则:

晶体与RF器件之间的连线尽可能短。

相互之间的走线尽可能保持隔离。

如果并联寄生电容太大,则去除晶体下方的接地区域。

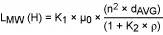

平面走线电感不建议使用平面走线或PCB螺旋电感,典型PCB制造工艺具有一定的不精确性,例如宽度、空间容差,从而对元件值精度影响非常大。因此,大 多数受控和高Q值电感均为绕线式。其次,可以选择多层陶瓷电感,多层片式电容厂商也提供这种产品。尽管如此,有些设计者还是在不得已的情况下选择了螺线电感。计算平面螺旋电感的标准公式通常采用惠勒公式10:  式中,a为线圈的平均半径,单位为英寸;n为匝数;c为线圈磁芯的宽度(rOUTER - rINNER),单位为英寸。当线圈的c 》 0.2a时11,该计算方法的精度在5%之内。 可以使用方形、六角形或其它形状的单层螺旋电感。可以找到非常好的近似方法,对集成电路晶圆上的平面电感进行建模。为了达到这一目的,对标准惠勒公式进行修改,得到非常适合小尺寸及方形规格的平面电感估算方法12。

式中,a为线圈的平均半径,单位为英寸;n为匝数;c为线圈磁芯的宽度(rOUTER - rINNER),单位为英寸。当线圈的c 》 0.2a时11,该计算方法的精度在5%之内。 可以使用方形、六角形或其它形状的单层螺旋电感。可以找到非常好的近似方法,对集成电路晶圆上的平面电感进行建模。为了达到这一目的,对标准惠勒公式进行修改,得到非常适合小尺寸及方形规格的平面电感估算方法12。  式中,ρ为充填比:

式中,ρ为充填比: ;n为匝数,dAVG为平均直径:

;n为匝数,dAVG为平均直径: 。对于方形螺旋,K1 = 2.36,K2 = 2.75。13 避免使用这种电感的原因有很多,它们通常受空间限制而导致电感值减小。避免使用平面电感的主要原因是受限制的几何尺寸,以及对临界尺寸的控 制较差,从而无法预测电感值。此外,PCB生产过程中很难控制实际电感值,电感还会将噪声耦合到电路的其它部分的趋向(参见上文中的引线耦合部分)。 总而言之,应该:

。对于方形螺旋,K1 = 2.36,K2 = 2.75。13 避免使用这种电感的原因有很多,它们通常受空间限制而导致电感值减小。避免使用平面电感的主要原因是受限制的几何尺寸,以及对临界尺寸的控 制较差,从而无法预测电感值。此外,PCB生产过程中很难控制实际电感值,电感还会将噪声耦合到电路的其它部分的趋向(参见上文中的引线耦合部分)。 总而言之,应该:

避免使用平面走线电感。

尽量使用绕线片式电感。

总结如上所述,几种常见的PCB布局陷阱会造成ISM-RF设计问题。然而,注意电路的非理想特性,您完全可避免这些缺陷。 补偿这些不希望的影 响需要适当处理表面上无关紧要的事项,例如元件方向、走线长度、过孔布置,以及接地区域的用法。遵守以上的指导原则,可明显节省浪费在修正错误方面的时间和金钱。

审核编辑 :李倩

-

电路

+关注

关注

172文章

5901浏览量

172135 -

pcb

+关注

关注

4319文章

23080浏览量

397516 -

电路板

+关注

关注

140文章

4951浏览量

97689

原文标题:【技术园地】注意!这些PCB布局陷阱会毁掉你板子

文章出处:【微信号:江西省电子电路行业协会,微信公众号:江西省电子电路行业协会】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB线路板常见缺陷原因分析:解锁电路板制造的隐秘挑战

plc与电脑无法通讯的3种可能原因

焊接时出现炸锡现象的原因有哪些?

一些可能出现的PCB布局问题、原因及其影响

一些可能出现的PCB布局问题、原因及其影响

评论