在SV功能覆盖率中通常coverpoint中变量的某些比特我们并不关心。例如对于addr[3:0],我们只希望其中的每一个比特都覆盖过“0”和“1”。

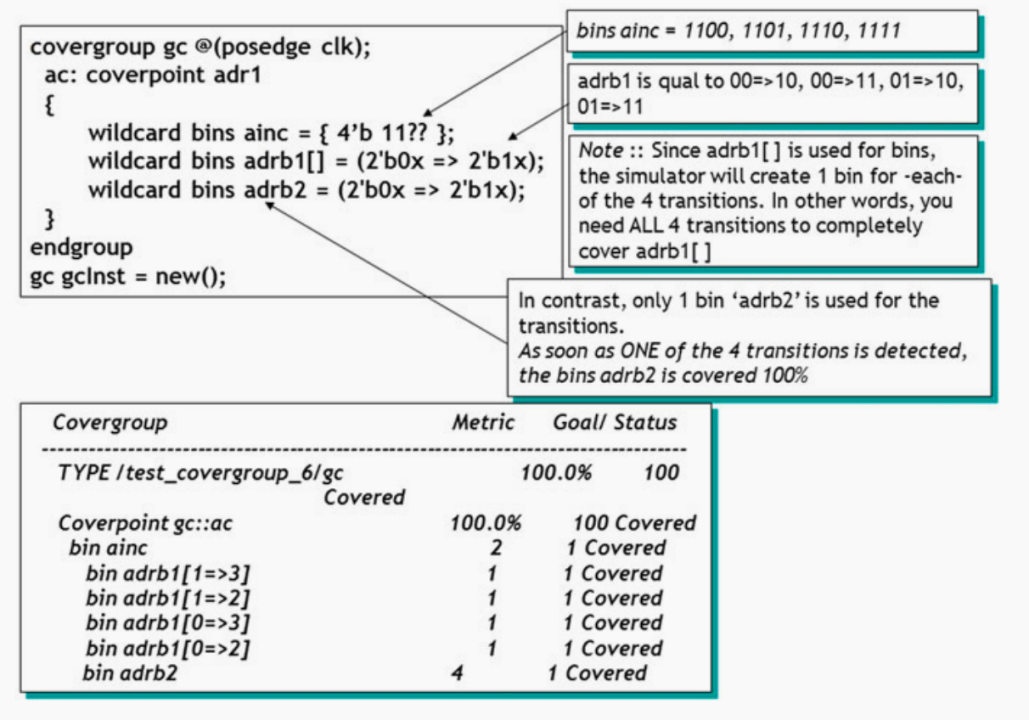

在上图中,可以用wildcard ' x '或' z '或' ?’表明某些比特我们并不关心,不管它是“0”还是“1”。

wildcard bins ainc = {4’b11??}

表示我们希望能够覆盖比特[3:2]为2’b11的场景,不关心比特[1:0],所以

4’b1100、4’b1101、4’b1110、4’b1111

都算完成了对于4’b11??的覆盖。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Address

+关注

关注

0文章

6浏览量

7571 -

BIN文件

+关注

关注

0文章

26浏览量

8282

原文标题:SV 功能覆盖率中的wildcard bin

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

关于SpinalHDL中的验证覆盖率收集简单说明

SpinalHDL 1.4.2中开始支持,在我们通过sbt构建项目时,build.sbt的依赖项配置如下:开启覆盖率收集功能 有注意上文所给例子的小伙伴或许已经注意到,我们已经开启了覆盖率

发表于 06-24 15:56

重点厘清覆盖率相关的概念以及在芯片开发流程中跟覆盖率相关的事项

较麻烦,工程师们需要针对各种各样的功能和应用场景,使用SV等验证语言去实现覆盖率模型(Coverage Model)或断言(Assertion),并且从大量的回归测试(Regression)中

发表于 09-14 11:57

Systemverilog覆盖率的合并和计算方式

说下sv里覆盖率的计算方式。 说明下,coverpoint有两种,1种是用户自动指定bins,另1种是系统自动生成bins。1个bin如果没有转换或者值,那么这个bin的结果会从Ci

发表于 03-21 14:24

针对功能覆盖率的验证过程

针对功能覆盖率的验证过程神州龙芯集成电路设计公司徐伟俊 杨鑫 陈先勇 夏宇闻[摘要]:本文在介绍传统验证过程及其局限性的基础上,阐述了针对功能覆盖率

发表于 12-23 16:12

•13次下载

基于覆盖率的功能验证方法

随着半导体技术的发展,验证已经逐渐成为大规模集成电路设计的主要瓶颈。首先介绍传统的功能验证方法并剖析其优缺点,然后引入传统方法的一种改进基于覆盖率的验证方法,最后

发表于 06-29 10:46

•22次下载

Verilog代码覆盖率检查

Verilog代码覆盖率检查是检查验证工作是否完全的重要方法,代码覆盖率(codecoverge)可以指示Verilog代码描述的功能有多少在仿真过程中被验证过了,代码覆盖率分析包括以

发表于 04-29 12:35

•8406次阅读

IP开发时如何考虑复用覆盖率

如何在开发IP的同时去巩固集成和复用覆盖率?IP的某些功能和性能是可以配置的,需要考虑的是IP被各种合理配置后的工作是否都能够正常,将功能覆盖率先整理为层次化的抽象

汽车功能安全诊断覆盖率的评估

例一种安全机制可以在本附件中具有较高的通用典型诊断覆盖率,但如果所使用的诊断测试间隔大于符合相关容错时间间隔所需的诊断测试间隔,则避免违反安全目标的具体诊断覆盖率将低得多。

嵌入式代码覆盖率统计方法和经验

代码覆盖率是衡量软件测试完成情况的指标,通常基于测试过程中已检查的程序源代码比例计算得出。代码覆盖率可以有效避免包含未测试代码的程序被发布。 1. 问题背景 代码覆盖(Code cov

统计嵌入式代码覆盖率的方法和经验

代码覆盖率是衡量软件测试完成情况的指标,通常基于测试过程中已检查的程序源代码比例计算得出。代码覆盖率可以有效避免包含未测试代码的程序被发布。 1. 问题背景 代码覆盖(Code cov

怎么才能写出高覆盖率的Verilog代码?

芯片前端工程中,测试验证的核心理念:以提高覆盖率为核心。设计工程师需要关心的主要有行覆盖率(Block),条件覆盖率(Expression),翻转覆

高覆盖率的Verilog代码的编写技巧

设计工程师需要关心的主要有行覆盖率(Block),条件覆盖率(Expression),翻转覆盖率(Toggle),状态机覆盖率。本文从ASIC设计的角度上来讨论,如何写出高

SV功能覆盖率中的wildcard bin介绍

SV功能覆盖率中的wildcard bin介绍

评论