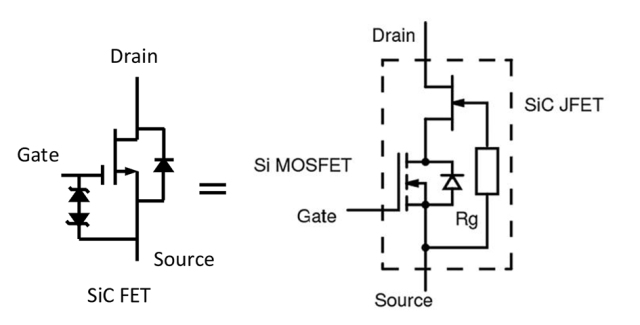

碳化硅 (SiC) MOSFET 的快速开关速度、高额定电压和低导通 RDS(on) 使其对电源设计人员极具吸引力,这些设计人员不断寻找提高效率和功率密度的方法,同时保持系统简单性。

然而,由于其快速开关速度会产生高漏源电压(VDS)尖峰和较长的振铃持续时间,因此它们会引入EMI,尤其是在高电流水平下。

了解 VDS尖峰和振铃

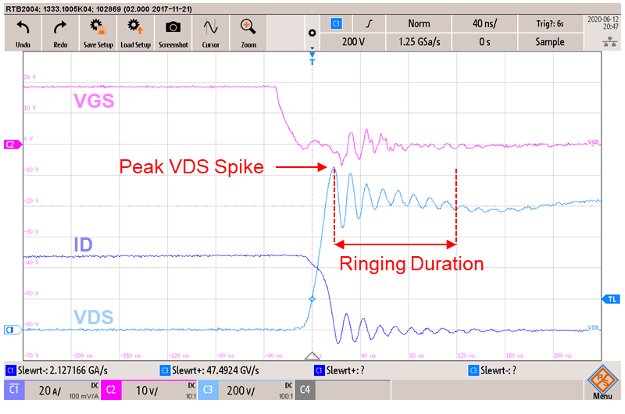

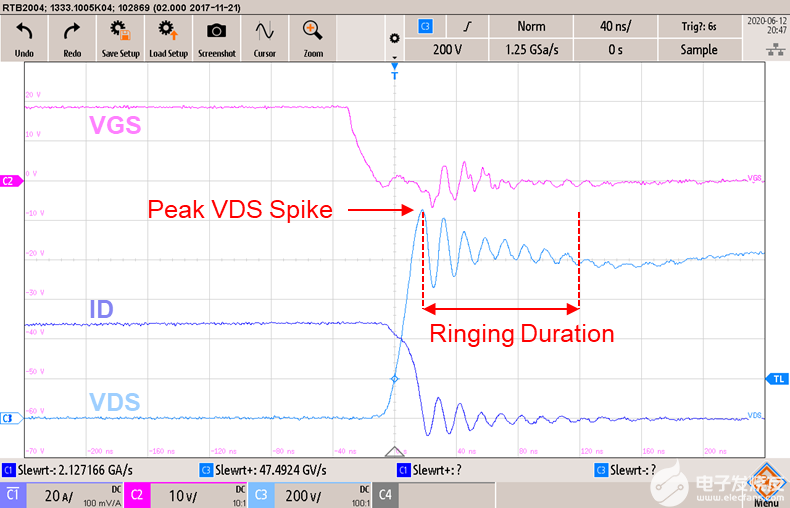

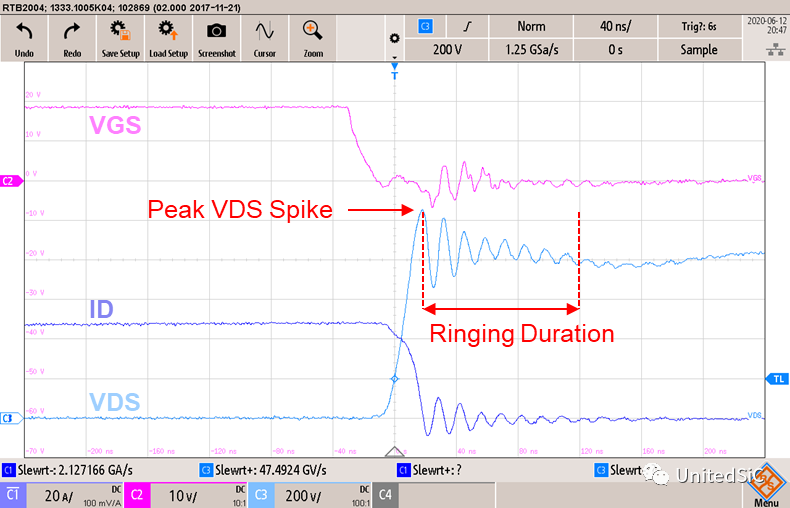

寄生电感是V的主要原因DS碳化硅 MOSFET 的尖峰和振铃。从关断波形(图1)来看,栅源电压(VGS)为18V至0V。关断的漏极电流(ID)为50A,VDS为800V。SiC MOSFET 的快速开关速度可产生高V DS尖峰和较长的振铃持续时间。该尖峰降低了器件处理雷电条件或负载突然变化的设计裕量,并且长振铃持续时间会引入EMI。在高电流水平下,这一事件更加明显。

图1.VDS尖峰和关断时振铃,采用 SiC MOSFET (1200V 40mOhm)

常见的EMI抑制技术

抑制EMI的传统方法是降低通过器件的电流流速(dI/dt),这是通过使用高栅极电阻(RG)来实现的。但高RG会显著增加开关损耗,并且在效率和EMI之间存在折衷。

抑制EMI的另一种方法是降低电源环路杂散电感。然而, 为了实现这一目标, PCB的布局需要更小, 电感更少封装。然而,最小化电源环路是有限的,并且需要遵守最小间距和间隙安全规定。使用较小的封装也会影响热性能。

滤波器设计可用于帮助满足EMI要求并简化系统权衡。频率抖动等控制技术也可以降低电源的EMI噪声。

使用 RC 缓冲器

采用简单的RC缓冲器是一种更有效和高效的方法。它控制 VDS 尖峰并缩短振铃持续时间,效率更高,关断延迟可忽略不计。对于更快的dv/dt和额外的电容,缓冲电路具有更高的位移电流,从而降低了关断转换处的ID和VDS重叠。

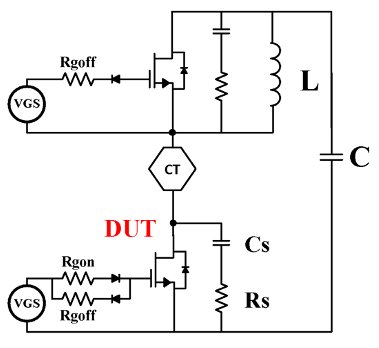

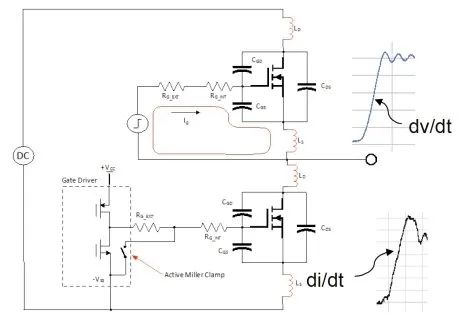

双脉冲测试(DPT)证明了RC缓冲器的有效性。它是带有感性负载的半桥配置。电桥的高侧和低侧使用相同的器件,在低侧测量VGS、VDS和ID(图2)。电流互感器(CT)测量器件和缓冲电流。因此,测得的总开关损耗包括器件和缓冲器损耗。

图2.半桥配置(顶部和底部设备相同)

RC 缓冲器只是一个 200pF 电容器和 10Ω 电阻,串联在 SiC MOSFET 的漏极和源极上。

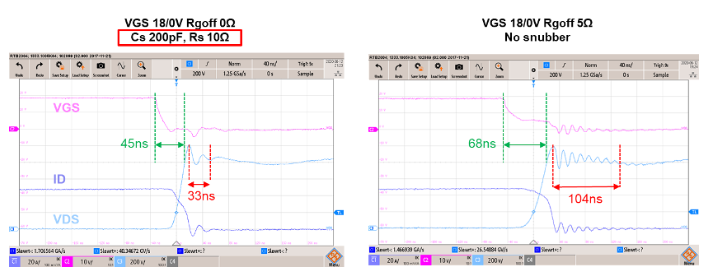

图 3:RC 缓冲器(左)比高 RG(右)更有效地控制关断 EMI

在图3中,比较了图1中同一器件的关断。左侧波形使用R G(off)低的RC缓冲器,而右侧波形具有高RG(off)且没有缓冲器。两种方法都限制了关断峰值尖峰漏源电压VDS。然而,缓冲电路通过将振铃持续时间减少到仅33ns而更有效,并且延迟时间也更短。

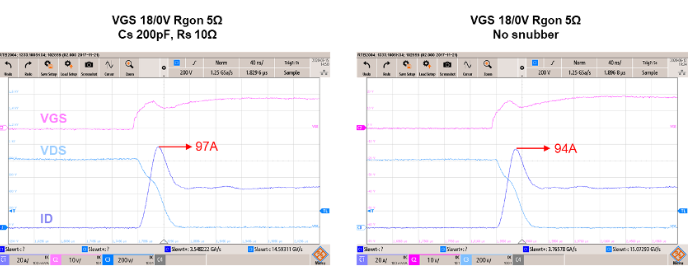

图4.比较表明,使用 RC 缓冲器在开启时的影响非常小

图4比较了R G(on)为5Ω时有RC缓冲器(左)和不带RC缓冲器的波形。RC缓冲器的导通波形具有略高的峰值反向恢复电流(IRR),但没有其他明显的差异。

RC 缓冲器比高 RG(off) 更有效地控制 VDS尖峰和振铃持续时间,但它会影响效率吗?

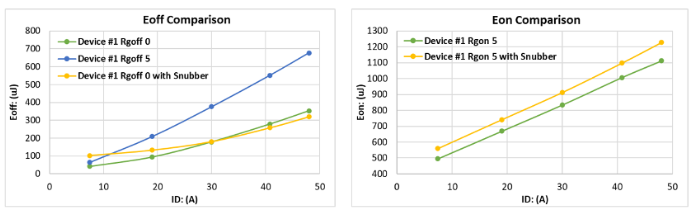

图5.缓冲器与高RG(关闭)之间的开关损耗(E 关闭、E 开启)比较

在48A时,高R G(关断)开关损耗是低RG(关断)缓冲器的两倍以上,几乎与不使用缓冲器的缓冲器相当。因此,可以得出结论,缓冲器效率更高,可以更快地切换和控制VDS尖峰和振铃。从导通开关损耗来看,缓冲器仅略微增加E。

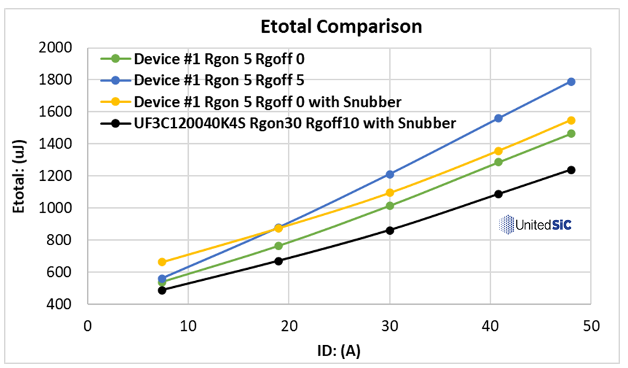

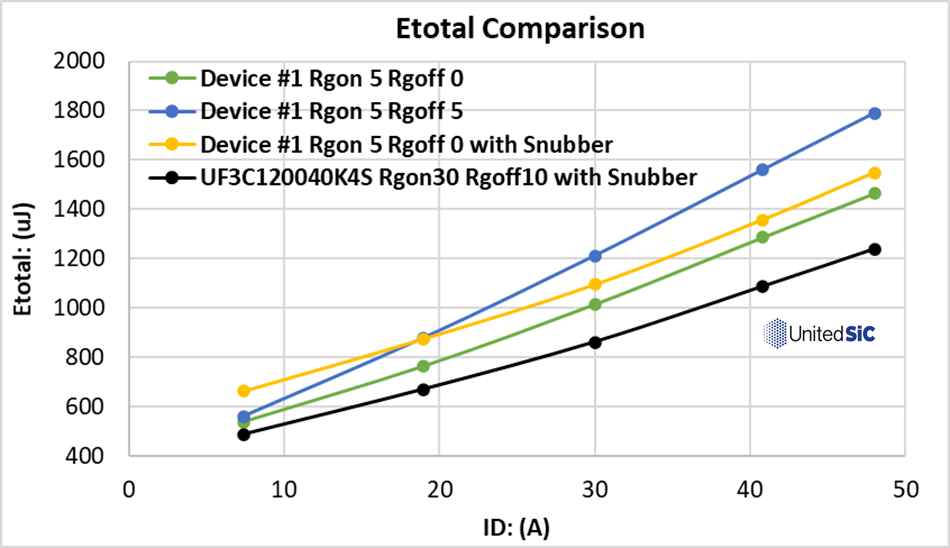

图6.缓冲器的总开关损耗(E总损耗)与高RG(off)的比较

为了更好地理解整体效率,Eoff和Eon相加 - E总计(图6)。全速开关时,缓冲器在18A以上效率更高。对于开关频率为40A/40kHz的40mΩ器件,采用RC缓冲器时,高RG(关断)之间的损耗差为11W。总而言之,缓冲器是一种更简单、更有效、更高效的方法,可以最大限度地减少EMI和开关损耗,而不是使用高RG(off)。

审核编辑:郭婷

-

MOSFET

+关注

关注

147文章

7203浏览量

213702 -

emi

+关注

关注

53文章

3596浏览量

127862 -

SiC

+关注

关注

29文章

2841浏览量

62748

发布评论请先 登录

相关推荐

如何最大限度地提高SiC MOSFET性能呢?

为何使用 SiC MOSFET

全SiC功率模块的开关损耗

开关损耗更低,频率更高,应用设备体积更小的全SiC功率模块

SiC-SBD大幅降低开关损耗

MOSFET开关损耗分析

最大限度地减少SiC FET中的EMI和开关损耗

最大限度降低SiC FET的EMI的开关损耗

全SiC功率模块的开关损耗

如何在使用SiC MOSFET时最大限度地降低EMI和开关损耗

如何在使用SiC MOSFET时最大限度地降低EMI和开关损耗

评论