本篇文章为“读懂 SmartSiC” 系列文章的下篇,将对 SmartSiC 解决方案的创新优势、研发、生产情况进行深入的介绍。

阅读“读懂 SmartSiC” 系列文章上篇

SmartSiC晶圆卓越的性能:

更环保、更高效、更出色

Soitec SmartSiC 晶圆

无论是对于 150mm 晶圆还是 200mm 晶圆而言,SmartSiC 都是一种更环保、更高效、更出色的技术解决方案,有望成为 SiC 市场的行业标准之一。

SmartSiC 将可重复利用十次的优质单晶 SiC 与超高导电性操作晶圆相结合,与传统 SiC 衬底相比,这种即插即用的解决方案可以无缝集成到所有现存的电源生产线中,并表现出明显的商用、环境与制造优势。

简单且节能的制造工艺使 SmartSiC 的碳足迹更少,更为环保。与传统 SiC 相比,每片 SmartSiC 晶圆减少的碳排放量可高达 70%。

通过重复利用稀缺的 200mm 单晶供体,Soitec 能够助力这些大尺寸衬底的快速落地应用,赋能市场的增长。SmartSiC 的优化设计所带来的卓越生产良率、更高的效率和功率密度,为电力电子设备提供了更好的解决方案。相比块状 SiC,SmartSiC 具有更高的导电性,可为每平方毫米功率器件(例如 MOSFET 或二极管)提供多达 20% 的电流。这是生成新一代功率器件的制胜秘诀。

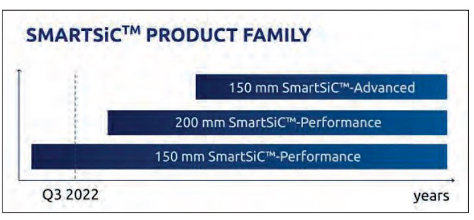

Soitec 的 SmartSiC 产品系列由 SmartSiC-Performance和 SmartSiC-Advanced 衬底组成。SmartSiC-Performance 目前处于原型开发阶段,正在与 Soitec 客户进行验证。而 Soitec 的创新团队正在研发 SmartSiC-Advanced 无 BPD 衬底,该产品目前处于送样阶段。

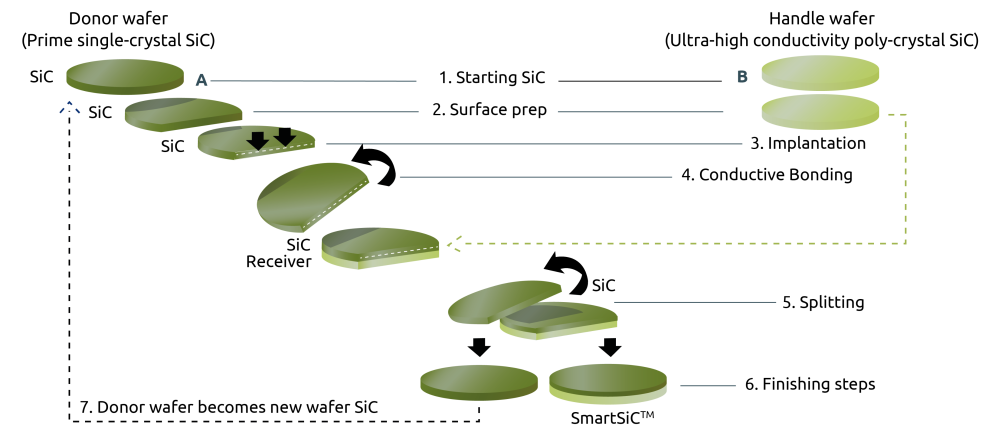

图 2:Soitec 独特且专利的 SmartCut 工艺同样适用于 SiC 材料

在具有超高导电性的多晶碳化硅操作衬底之上(其 150mm 和 200mm 晶圆的总厚度分别为 350µm 和 500µm),SmartSiC 衬底的优化设计能够提供最高水准、厚度小于 1µm 的单晶 SiC 层。供体晶圆减去用于第一个 SmartSiC 晶圆的 1µm 层之后,可重复用于第二个 SmartSiC 晶圆。以此类推,每个供体晶圆至少可用于十个 SmartSiC 晶圆。

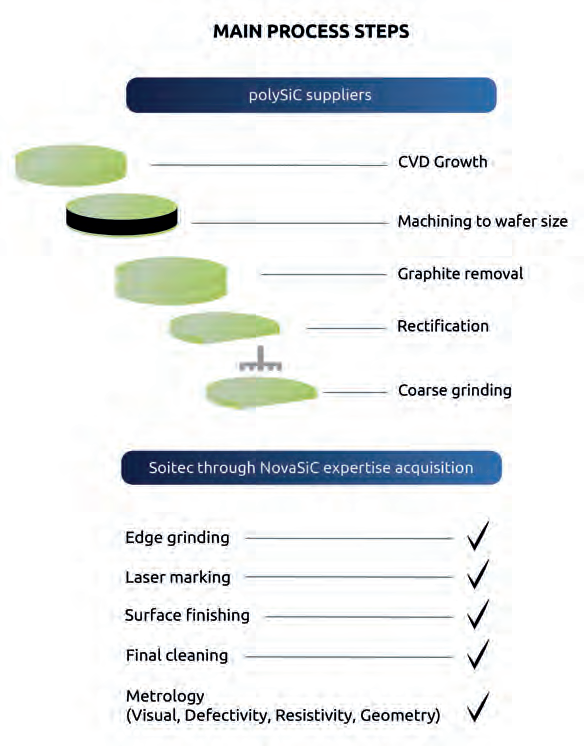

与块状 SiC 中使用的物理气相传输 (PVT) 相比,采用多晶碳化硅作为每个 SmartSiC 晶圆生产的操作晶圆则是基于更环保、用时更短的化学气相沉积 (CVD) 工艺。Soitec 和合作伙伴共同开发的 PolySiC 具有足够的掺杂来控制衬底的导电性,同时还能保持极具竞争力的成本优势(见图 3)。

图 3:PolySiC 主要工艺步骤

经过多年积淀,无论成熟度还是专业储备,Soitec 都具备能力定义并确保晶圆几何构造的完美,而这恰是掌握晶圆键合的关键所在。2021 年 11 月 Soitec 收购 NovaSiC,为公司带来超过 25 年的 SiC 晶圆生产经验,是 Soitec 在碳化硅战略路线上的又一里程碑。

截至目前,Soitec 的 SmartSiC 已在衬底工艺和设计中达到了稳定的高水平。经过密集和大规模的测试与原型设计,Soitec 生产的晶圆为市场、电力设备和电力系统带来的价值和益处显著。采用 SmartSiC 生产的 MOSFET 和二极管性能均获得大幅提升,同时拥有了更为长期的可靠性和更强的高温稳健性。目前,多家设备制造商已承诺加大资源投入力度,在其下一代产品的认证中采用 SmartSiC。

探秘 SmartSiC 的研发

Soitec 最初派遣研发团队深入研究 SmartSiC 项目时,目的在于将 SiC 的制造良率提高到全球公认的硅基功率器件标准水平。

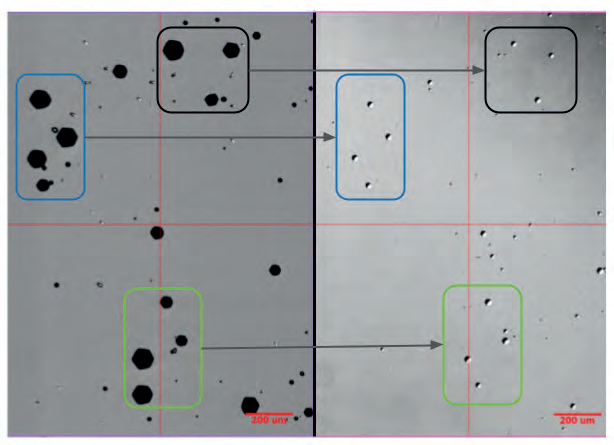

SmartCut 工艺可以保持来料供体晶圆的晶体质量。如图 4 所示,在供体和 SmartSiC 表面的相同位置可以观察到氢氧化钾(KOH) 蚀刻晶体产生的缺陷。

图 4:晶体缺陷表征、KOH 蚀刻和光学显微镜观察结果;单晶 SiC 供体(左)和 SmartSiC (右)点对点比对

为降低缺陷水平,Soitec 探索并采用了一种新的概念,即在已去除基面位错(BPD)的供体上采用 Smart Cut 工艺。

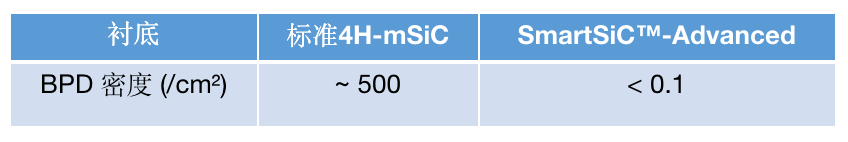

利用单晶 SiC 晶圆独特的生长特性,无 BPD 的供体能够将无 BPD 层转移到多晶 SiC 操作晶圆上。这种新型优化衬底称为 SmartSiC-Advanced。SmartSiC-Advanced 衬底的 BPD 密度值如图 5 所示。

图 5:供体 SmartSiC-Advanced 衬底中的 BPD 缺陷密度

具备无 BPD 顶层的 SmartSiC-Advanced 衬底因此成为漂移外延环节的优质晶种层。

这明显降低了致命缺陷的潜在成核位置密度,同时扩大了外延工艺窗口并简化了外延堆栈,而且无需转换缓冲层。

良率模拟和实验表明,这些改进将引入的外延生长致命缺陷密度降低了 10 倍,并且将大于 20 平方毫米的器件生产良率提高到 20% 以上。在器件可靠性方面,无基面位错层不仅可以防止位错滑动,还能消除器件中的双极退化。Soitec 的下一代 SmartSiC-Advanced 衬底消除了 SiC 晶圆中的 BPD,对整个 SiC 行业而言,有望将 SiC 器件制造良率提升至 90%。

而且,SmartSiC 中采用的多晶 SiC 操作衬底具有高掺杂水平,这使 SiC 功率器件(二极管或 MOSFET)背面的欧姆接触层更易制成。

Soitec 的最新研究证明,无需退火的欧姆接触工艺可在 SmartSiC 衬底上轻松执行,且长远芯片组装的可靠性不会因此受到影响。

Soitec 150mm 的 SmartSiC-Advanced 产品已经开始送样。其原型衬底正接受主要客户的检验,并可根据需求向其他客户弹性交付。更多数据已于 ICSCRM 2022 国际会议(2022 年碳化硅及相关材料国际会议)上进行公布。

SmartSiC 晶圆厂的启动与扩产

图 6:位于法国的新工厂贝宁 4 厂

大批量生产是 Soitec 的下一步目标举措。Soitec 用于 SmartSiC 大规模生产的新工厂 Bernin 4 已于 2022 年 3 月破土动工,开工日期定为 2023 年年中(如图 6 所示)。凭借最先进的设备设施,Soitec 将在 2024 年实现 SmartSiC 的产能提升;到 2030 年,SmartSiC 晶圆总产能(包括 150mm 和 200mm)将达到 100 万片/年。其中大部分为 200mm 晶圆,这得益于 Soitec 的两项关键技术:

经过数十年的发展,晶圆的尺寸面积不断扩大,SmartCut 工艺的效益规模也呈现出指数级增长,而 200mm 规格的晶圆变得愈发重要。

Soitec 200mm SmartSiC 晶圆所具备的 10 倍重复利用率,将成倍优化资源利用率,缓解供应链压力,并加速汽车和工业市场中高质量晶圆的高效生产与应用。

随着多个合作伙伴对 SmartSiC-Performance 产品原型的认可(如图 7 所示),2022 年的产品认证正处于紧锣密鼓地扩大范围并加速推进中。

图7:150mm 和 200mm 规格的 SmartSiC 晶圆

SmartSiC晶圆正成为新的行业标准

电动汽车正在经历百年一遇的变革,市场上的创新成果不断涌现。上一次交通业变革发生在二十世纪 90 年代左右,人类用了 15 年时间从马车交通时代转进入机械交通时代;而鉴于 CO2减排和减缓全球变暖的迫切需要,从汽油车时代进入电动车时代的转变应该会更快。

自 2018 年特斯拉引入 SiC 并开创电动汽车市场以来,这项技术已被大多数汽车制造商采纳。然而,SiC 还需要克服在电气性能、产能、成本和良率方面的众多障碍,才能在电动汽车领域独占鳌头。

Soitec 成功预见了上述挑战以及电动汽车行业蓬勃发展的势头。我们推出的 SmartSiC 是具有更高附加值的单晶 SiC 衬底替代品,能够为更高效率的电源提供更环保、更高效、更出色的解决方案。

由于单晶 SiC 供体晶圆可重复使用 10 次,并且低 RDSON 功率器件的电导率提高了10倍,SmartSiC 已能够实现大批量生产,并有望成为行业新标准。

Soitec 汽车与工业部门副总裁 Emmanuel Sabonnadiere 表示:“我们的 SmartSiC 衬底将成为加速电动汽车变革的关键,可帮助电力电子设备的能效与性能提升至新高度,赋能电动汽车的发展。”

图 8:SmartSiC 产业化蓝图

Soitec 的创新将助力提升资源利用及能效,助推经济发展和赋能商业成功。我们的创新成果正在推动众多行业和生态系统的发展,而半导体及其基础衬底的战略地位正是他们所一致认可的。

Soitec 的创新土壤孕育着美好未来!

注:Soitec 的四篇科学出版物已于 ICSCRM 2022 上正式发布。

审核编辑 :李倩

-

单晶

+关注

关注

1文章

61浏览量

14095 -

SiC

+关注

关注

29文章

2796浏览量

62582 -

SOITEC

+关注

关注

3文章

48浏览量

14290

原文标题:读懂 SmartSiC™| 助推电动汽车发展的新动力:Soitec 的 SmartSiC™ (下篇)

文章出处:【微信号:Soitec,微信公众号:Soitec】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

硬核智造驱动创新,大核桃智能巡检整体解决方案助力高危行业安全生产

解决方案 | 基于TSMaster的平板电脑解决方案

emc存储解决方案的优势

【⌈嵌入式机电一体化系统设计与实现⌋阅读体验】+磁力输送机系统设计的创新与挑战

梯度科技入选2023年信息技术应用创新解决方案名单

飞凌嵌入式技术创新日(深圳站)精彩回顾

环旭电子微小化创新研发中心为多样化市场提供SiP双引擎技术平台

SmartSiC解决方案的创新优势、研发、生产情况

SmartSiC解决方案的创新优势、研发、生产情况

评论