AIU:32个处理器核心、230亿个晶体管

IBM在AI芯片技术上的不断升级

更多热点文章阅读

“极寒之地”!数据称硅谷裁员占全球科技公司三分之一,至少8家企业裁员过千 AI技术“偏科”,V2X反应不及人眼?自动驾驶从L3过渡L4面临哪些挑战 英国阻挠中企收购!已完成收购,却被要求剥离86%的股权! 对标苹果M系列芯片,高通推出Oryon芯片内核,PC市场又起战事 转向美国制造,苹果大幅调整供应链的背后逻辑是什么?

原文标题:IBM全新AIU芯片:5nm工艺,230亿晶体管!深度学习处理性能强劲!

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电子发烧友网

+关注

关注

1011文章

544浏览量

164863

原文标题:IBM全新AIU芯片:5nm工艺,230亿晶体管!深度学习处理性能强劲!

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

消息称台积电3nm、5nm和CoWoS工艺涨价,即日起效!

)计划从2025年1月起对3nm、5nm先进制程和CoWoS封装工艺进行价格调整。 先进制程2025年喊涨,最高涨幅20% 其中,对3nm、5nm

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破

Rapidus 的 2nm 制程生产流程之中。 IBM 宣称,当制程推进到 2nm 阶段时,晶体管的结构会从长久以来所采用的 FinFET(鳍式场效应

如何测试晶体管的性能 常见晶体管品牌及其优势比较

如何测试晶体管的性能 晶体管是电子电路中的基本组件,其性能测试对于确保电路的可靠性和稳定性至关重要。以下是测试晶体管

台积电产能爆棚:3nm与5nm工艺供不应求

台积电近期成为了高性能芯片代工领域的明星企业,其产能被各大科技巨头疯抢。据最新消息,台积电的3nm和5nm工艺产能利用率均达到了极高水平,其

AI芯片驱动台积电Q3财报亮眼!3nm和5nm营收飙涨,毛利率高达57.8%

10月17日,台积电召开第三季度法说会,受惠 AI 需求持续强劲下,台积电Q3营收达到235亿美元,同比增长36%,主要驱动力是3nm和5nm需求强

晶体管的输出特性是什么

晶体管的输出特性是描述晶体管在输出端对外部负载的特性表现,这些特性直接关系到晶体管在各种电路中的应用效果和性能。晶体管的输出特性受到多种因素

CMOS晶体管的尺寸规则

CMOS晶体管尺寸规则是一个复杂且关键的设计领域,它涉及到多个方面的考量,包括晶体管的性能、功耗、面积利用率以及制造工艺等。以下将从CMOS晶体管

NMOS晶体管和PMOS晶体管的区别

NMOS晶体管和PMOS晶体管是两种常见的金属氧化物半导体场效应晶体管(MOSFET)类型,它们在多个方面存在显著的差异。以下将从结构、工作原理、性能特点、应用场景等方面详细阐述NMO

GaN晶体管和SiC晶体管有什么不同

GaN(氮化镓)晶体管和SiC(碳化硅)晶体管作为两种先进的功率半导体器件,在电力电子、高频通信及高温高压应用等领域展现出了显著的优势。然而,它们在材料特性、性能表现、应用场景以及制造工艺

GaN晶体管的基本结构和性能优势

GaN(氮化镓)晶体管,特别是GaN HEMT(高电子迁移率晶体管),是近年来在电力电子和高频通信领域受到广泛关注的一种新型功率器件。其结构复杂而精细,融合了多种材料和工艺,以实现高效、高频率和高功率密度的

芯片晶体管的深度和宽度有关系吗

一、引言 有关系。随着集成电路技术的飞速发展,芯片晶体管作为电子设备的核心元件,其性能的优化和制造技术的提升成为了行业关注的焦点。在晶体管的众多设计参数中,深度和宽度是两个至关重要的因

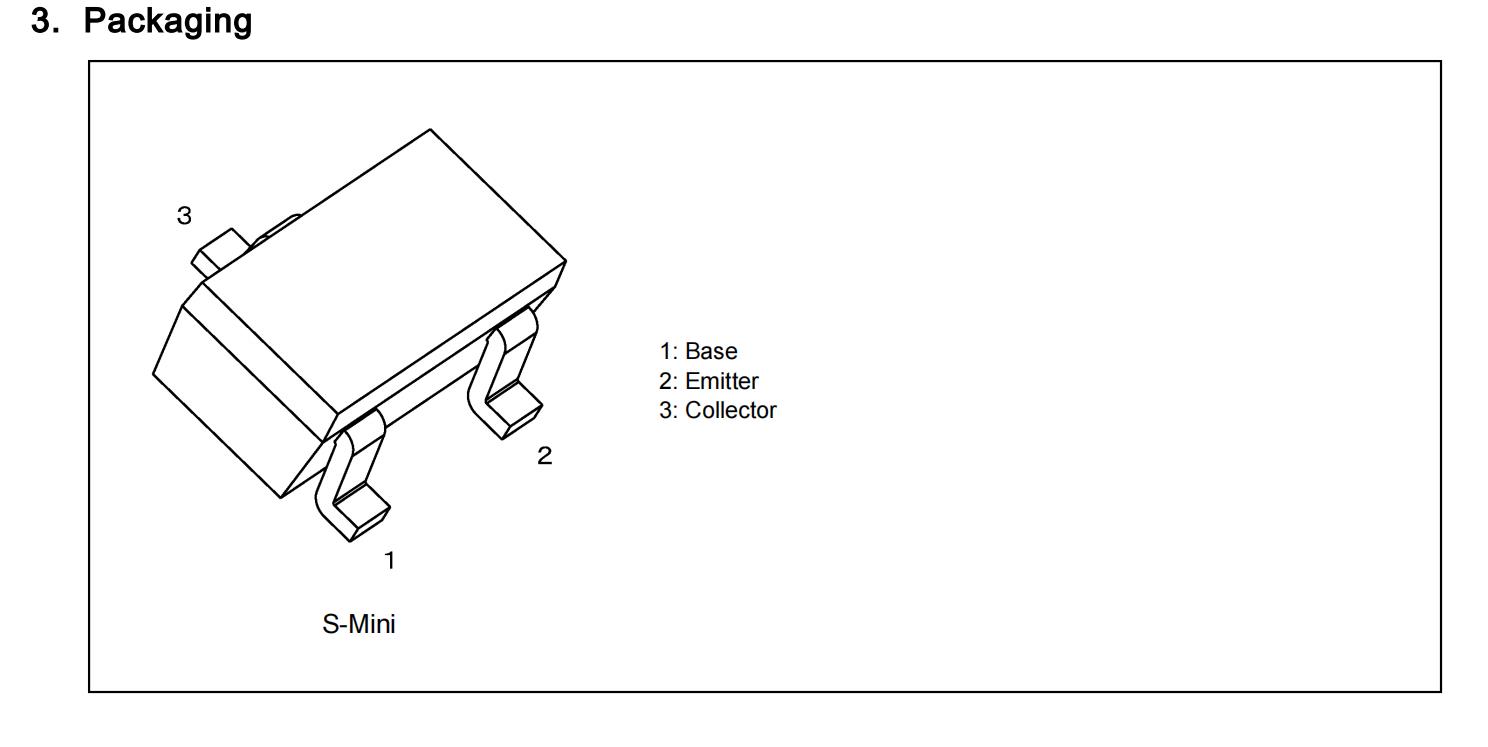

东芝2SC2712晶体管:性能强劲、应用广泛的完美选择

今天我要介绍一款在低频和音频放大应用中备受青睐的晶体管——东芝2SC2712。它不仅性能卓越,而且用途广泛,我们一起来看看它的亮点。 性能与参数 高电压和电流处理能力: 东芝2SC27

台积电升级4nm N4C工艺,优化能效与降低成本

在近日举办的 2024 年北美技术研讨会上,业务发展副总裁张凯文发表讲话称:“尽管我们的 5nm 和 4nm 工艺尚未完全成熟,但从 N5 到 N4 的光学微缩密度已提升 4%,且

IBM全新AIU芯片:5nm工艺,230亿晶体管!深度学习处理性能强劲!

IBM全新AIU芯片:5nm工艺,230亿晶体管!深度学习处理性能强劲!

评论