简介

3DIC Compiler具有强大的Bump Planning功能。它可在系统设计初期阶段没有bump library cells的情况下,通过定义pseudo bump region patterns、创建bump regions以及填充pseudo bumps、创建Bumps的连接关系、为不同net的Bumps着色等操作,快速实现bump原型创建以及复杂bump规划设计。

本视频将展示在没有bump library cells的情况下,3DIC Compiler 如何在GUI界面使用“pseudo” bumps 快速实现Bump Planning,流程包括:

定义bump region patterns

创建bump regions以及填充pseudo bumps

快速assign nets到对应的Bumps

为不同net的Bumps着色

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:【芯和设计诀窍视频】如何使用3DIC Compiler实现Bump Planning

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

相关推荐

近日,芯华章正式推出了其新一代高性能FPGA原型验证系统——HuaPro P3。这款系统集成了最新一代的可编程SoC芯片,并配备了芯华章自主研发的HPE Compiler工具链,为用户

![的头像]() 发表于

发表于 12-11 09:52

•237次阅读

芯和半导体将于11月5-6日参加在深圳福田会展中心7号馆举办的国际集成电路展览会暨研讨会(IIC Shenzhen 2024),并在DesignCon专区中展示其3DIC Chiplet先进封装一体化EDA设计平台的最新解决方案。

![的头像]() 发表于

发表于 11-01 14:12

•293次阅读

DIC EXPO 2024在陪伴中国显示产业走过14个春秋之际,DIC系列会展活动将于下周引爆年度显示盛典,以全球显示产业交流合作的纽带,助力产业可持续化健康发展。

![的头像]() 发表于

发表于 09-27 10:06

•447次阅读

新思科技宣布推出面向英特尔代工EMIB先进封装技术的可量产多裸晶芯片设计参考流程,该流程采用了Synopsys.ai EDA全面解决方案和新思科技IP。此外,新思科技3DSO.ai与新思科技3DIC

![的头像]() 发表于

发表于 08-12 09:50

•632次阅读

提供了一个统一的协同设计与分析解决方案,通过新思科技3DIC Compiler加速从芯片到系统的各个阶段的多裸晶芯片设计的探索和开发。此外,新思科技3DSO.ai与新思科技3DIC

![的头像]() 发表于

发表于 07-16 09:42

•626次阅读

近日,在备受瞩目的DIC EXPO 2024国际(上海)显示技术及应用创新展上,天马展出多项健康显示技术,并凭借卓越的视觉体验与技术创新,斩获“DIC国际显示技术创新大奖”,全面展示出了天马在健康

![的头像]() 发表于

发表于 07-10 16:23

•1023次阅读

3DIC Compiler协同设计与分析解决方案结合新思科技IP,加速英特尔代工EMIB技术的异构集成 摘要: 新思科技人工智能(AI)驱动型多裸晶芯片(Multi-die)设计参考流程已扩展至

发表于 07-09 13:42

•821次阅读

7月3日,2024 DIC AWARD国际显示技术创新大奖颁奖典礼在上海举行。本届DIC 展会,维信诺国内首发多款显示器件产品,全场景显示应用终端新品齐亮相,一举斩获7项DIC AWA

![的头像]() 发表于

发表于 07-04 16:03

•1722次阅读

7月2日至5日,2024年中国国际显示产业高峰论坛暨国际显示技术及应用创新展(DIC 2024)在上海隆重举办。

![的头像]() 发表于

发表于 07-04 11:27

•1025次阅读

新思科技EDA事业部战略与产品管理副总裁Sanjay Bali表示:“新思科技在可投产的EDA流程和支持3Dblox标准的3DIC Compiler光子集成方面的先进成果,结合我们广泛的IP产品组合,使得我们与台积公司能够助力

![的头像]() 发表于

发表于 05-11 16:25

•468次阅读

套件赋能可投产的数字和模拟设计流程能够针对台积公司N3/N3P和N2工艺,助力实现芯片设计成功,并加速模拟设计迁移。 新思科技物理验证解决方案已获得台积公司N3P和N2工艺技术认证,可

发表于 05-11 11:03

•455次阅读

报道指出,此次订单主要由苹果的功率放大器供应商威讯联合半导体(Qorvo)下达。威讯方面主要负责设计iPhone天线组件,并集成新芯片以及提供Qorvo功率放大器。这些新芯片采用联电的3DIC先进工艺进行制造。

![的头像]() 发表于

发表于 04-02 11:26

•599次阅读

; 新思科技广泛的高质量 IP组合降低集成风险并加快产品上市时间,为采用Intel 18A 工艺的开发者提供了竞争优势; 新思科技 3DIC Compiler提供了覆盖架构探索到签收的统一平台,可实现采用

发表于 03-05 10:16

•398次阅读

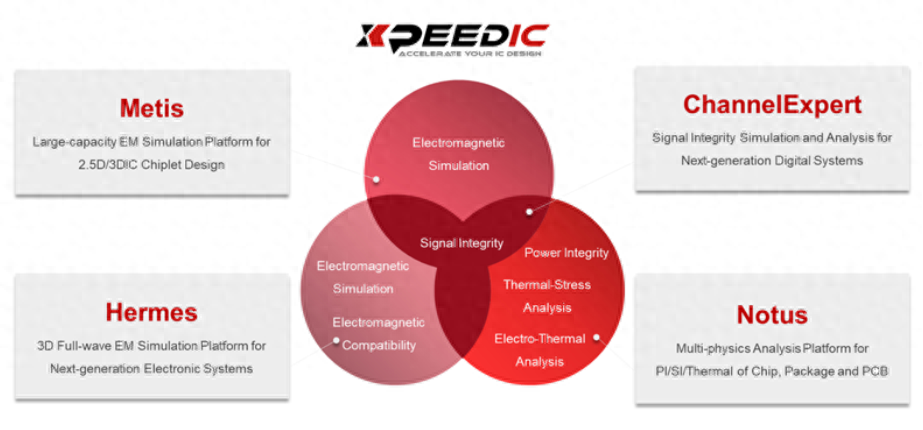

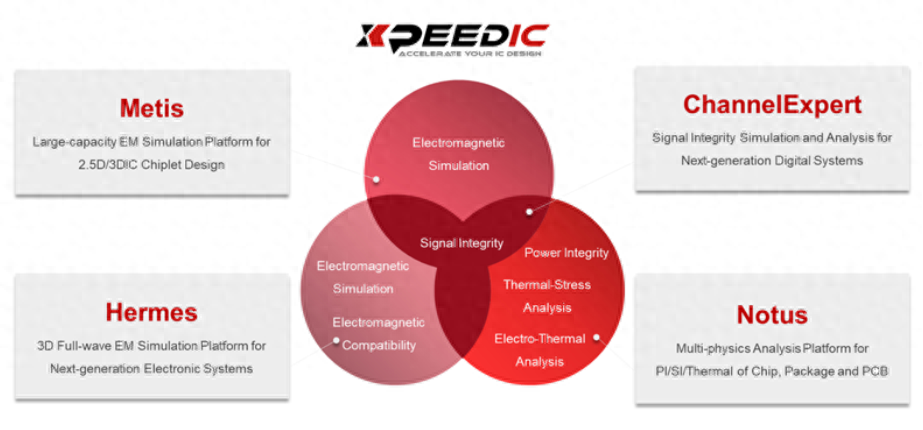

如下: 一、2.5D/3DIC Chiplet先进封装电磁仿真平台Metis 具有丰富的布线前仿真分析功能,集成业界2.5D/3D主流制程工艺的Interposer模板,用户可自定义布线形式和设置参数

![的头像]() 发表于

发表于 02-18 17:52

•654次阅读

三天。 针对下一代电子系统的SI/PI/多物理场分析EDA解决方案 发布亮点 2.5D/3DIC Chiplet先进封装电磁

发表于 02-02 17:19

•774次阅读

芯和设计诀窍概述 如何使用3DIC Compiler实现Bump Planning

芯和设计诀窍概述 如何使用3DIC Compiler实现Bump Planning

评论