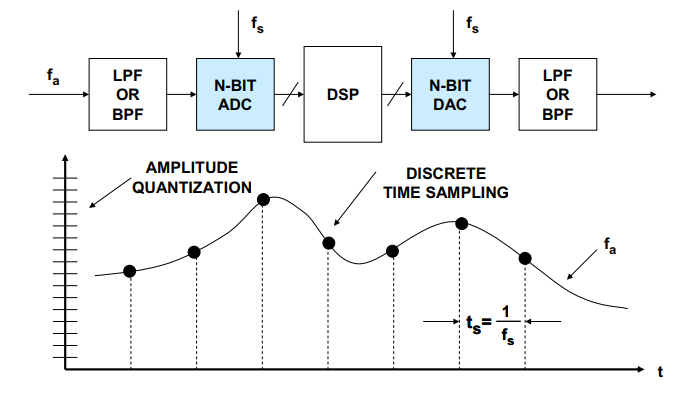

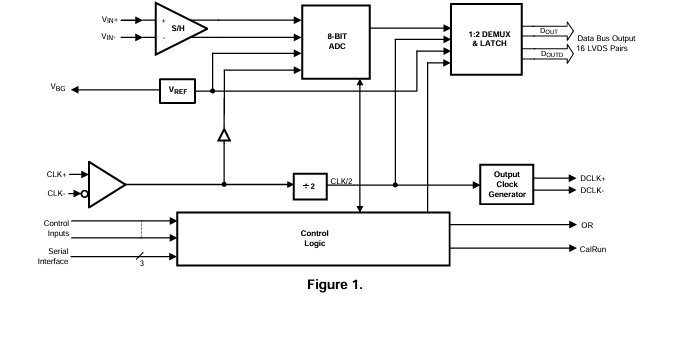

模数转换器即A/D转换器,简称ADC,将模拟信号转变为数字信号。输入端输入的模拟电压,经采样、保持、量化和编码四个过程的处理,转换成对应的二进制数码输出。

典型的数据采样系统 采样是利用模拟开关将连续变化的模拟量变成离散的数字量,由于经采样后形成的数字量宽度较窄,经过保持电路可将窄脉冲展宽,形成梯形波。量化是将阶梯形模拟信号中各个电压值转化为某个最小单位的整数倍,便于用数字量来表示。编码是将量化的结果(即整数倍值)用二进制数码来表示。这个过程则实现了模数转换。

01、分辨率与动态范围

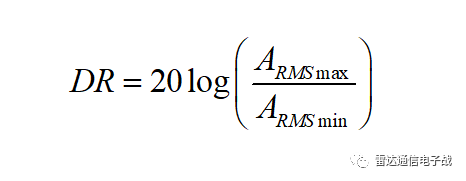

ADC分辨率为用于表示模拟输入信号的位数。为了更准确地复现模拟信号,须提高分辨率,使用较高分辨率的ADC也降低了量化误差。但成本就上去了。 动态范围(DR)定义为器件本底噪声至其规定最大输出电平之间的范围,通常用dB表示。ADC的动态范围是指ADC能够分辨的信号幅值范围;ADC的分辨率位数(N)决定ADC的动态范围,代表ADC可测量的输入信号等级范围,DR可定义为:

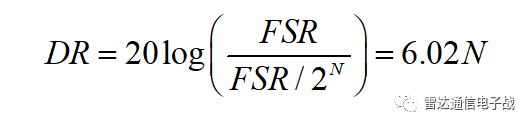

由于信号在给定时间视窗内的RMS幅值取决于信号幅值在该时间视窗内如何变化,因此ADC的DR变化取决于输入信号特征。对于其满量程范围(FSR)内的恒定DC输入而言,理想的N位ADC可分别测量FSR和FSR/2N的最大及最小RMS幅值。因此,ADC的DR为:

对于正弦波信号输入而言,正弦波输入信号的最小可测量RMS幅值受量化误差的限制,正弦波输入信号的理想ADC的DR是:DR=6.02N+1.76dB假设ADC的动态范围为60dB,则其可分辨的信号幅值为x至1000x。通常动态范围非常重要,因为如果信号太大,则会造成ADC输入过量程;如果信号太小,则会被淹没在转换器的量化噪声中。

02、信噪比与信噪失真比

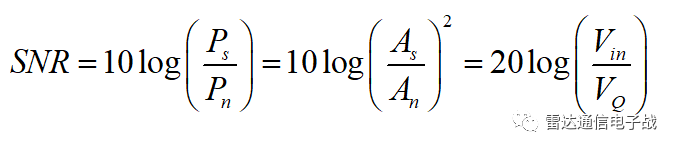

数模转换器的信噪比(SNR)是指输入信号功率与噪声功率的比值,这里用来量化数据转换器内的噪声,SNR也能使用信号幅度和噪声幅度的RMS值来衡量,以dB为单位。

在满刻度正弦波输入的条件下,ADC的理论最高SNR从量化噪声推导而得,表达式为:SNR=6.02N+1.76dB这里N是理想ADC的位数,对于理想的N位数据转换器(不考虑谐波失真)的正弦波输入,整个奈奎斯特带宽上能达到的最佳SNR。 但对于实际的ADC,除了量化噪声,数据转换器的SNR也会受到自身热噪声和采样时钟相位噪声的限制。噪声来自主要有三个源头: • 量化噪声 • ADC热噪声 • 抖动或采样不确定噪声 信号与噪声失真比(Signal to Noise And Distortion,SINAD)指输入正弦波时,RMS信号功率与总噪声功率和输出端(不含DC)的所有其他频率分量功率加上所有其他谐波分量功率的RMS和的比值。 SNDR是用于衡量数据转换器的动态性能的关键参数之一,它包含奈奎斯特带宽上的所有噪声和杂散。SNDR的表达式为:

其中,信号功率是有用信号、噪声和失真分量的平均功率。SNDR的单位是分贝(dB),SNDR将所有不良频率分量与输入频率做比较,反映的是输入信号的质量,从总体上衡量数据转换器的动态性能。SNDR越大,输入功率中的噪声和杂散比率越小

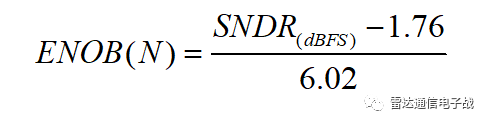

03、有效位数(ENOB)

有效位数 (ENOB) 是用于衡量数据转换器相对于输入信号在奈奎斯特带宽上的转换质量(以位为单位)的参数。 这里的ENOB假定转换器是拥有理论上完美性能,不发生失真,唯一产生的噪声是量化噪声,所以SNR 等于SNDR,即SNR(dBFS)= 6.02N+1.76dB。因此,ENOB也是SNDR的另一种表达方式:

然而,对于非理想数据转换器而言,SNDR和ENOB会发生劣化,包含噪声和其他缺陷,例如器件热噪声、输出代码缺失、谐波、AC/DC非线性、增益/偏移误差和孔径时钟相噪或抖动。外部偏置基准源和电源轨上的噪声也会降低ENOB。 总谐波失真(THD)测量信号的失真成分,用相对于基波的分贝(dB)表示。对于ADC,总谐波失真(THD)是所选输入信号谐波的RMS之和与基波之比。测量时,只有在奈奎斯特限值之内的谐波被包含在内。 类似于THD因非线性原因随输入频率增加而劣化,ENOB值也会随频率加大而劣化。ENOB来自于SNDR,而SNDR又与THD以及SNR相关联。要了解数据转换器的准确ENOB,需阅读数据手册中的详细规格和规定的条件。 大部分模拟数据转换器IC厂商一般倾向于推广理想条件下的ENOB,尤其是数据手册标题所载的ENOB值。然而,大量系统工程师和采购经理仍然好奇的是,为什么测量出的ENOB值和数据手册所载的理想值不同? 实际使用中,由于ADC自身存在噪声和误差,其输出不仅有量化噪声,还有失真引起的高次谐波,因此从未能达到这一SNR值。计算ADC的有效N:ENOB = (SNR–1.76)/6.02 dB。假设器件是一款12位ADC,ENOB可能仅为10bit。但需要注意的是这并不表示把ADC的后两位删掉就可以当成一个理想的10bit ADC来使用,这里ENOB的意思是12bit非理想ADC的SNDR与理想的10bit ADC的SNR相等。

有关ENOB的一些理解要点:

• 一般数据转换器数据手册标题显示的“位数”(12位或14位)指的是数字位或电压分辨率。这与ENOB无关。

• ENOB主要与噪声、非线性和输入频率存在函数关系。

• ENOB会因多种外部不确定性因素(例如时钟源、电源等)而劣化。

• ENOB是在整个奈奎斯特带宽上(DC到fs/2)计算的。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

9463浏览量

157210 -

adc

+关注

关注

100文章

7973浏览量

557323

原文标题:搞清ADC的动态范围(DR)和有效位数(ENOB)

文章出处:【微信号:雷达通信电子战,微信公众号:雷达通信电子战】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

探索PCM1804:高性能立体声A/D转换器的卓越之选

德州仪器PCM1804:高性能立体声A/D转换器的卓越之选

深入解析PCM1803A:高性能立体声A/D转换器的卓越之选

AD7111/AD7111A对数D/A转换器:特性、应用与设计要点

深度剖析HI5828:高速低功耗D/A转换器的卓越之选

AD9430:高性能12位A/D转换器的深度解析

LTC1603:高性能16位采样A/D转换器的全面解析

AD7226:一款高性能的CMOS四通道8位D/A转换器

ADC1175:低功耗高速A/D转换器的卓越选择

深入剖析ADC12DL080:高性能12位A/D转换器的设计与应用

深入剖析ADC08500:高性能8位500 MSPS A/D转换器的设计与应用

一文理解模数转换器中的有效位数

A/D转换器的信噪失真比和有效位数

A/D转换器的信噪失真比和有效位数

评论