1.同步电路设计

2.全异步电路设计

3.异步信号与同步电路交互的问题及其解决方法

4.SoC设计中的时钟规划策略

1.同步电路设计

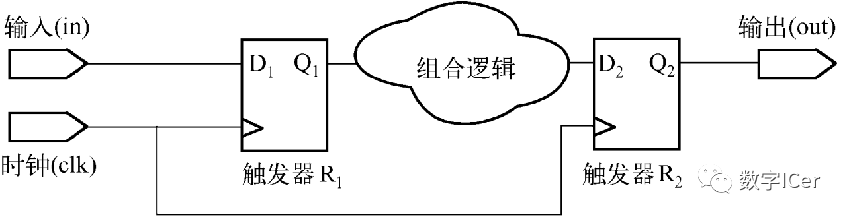

同步电路,即电路中的所有受时钟控制的单元,如触发器(Flip Flop)或寄存器(Register),全部由一个统一的全局时钟控制。

同步电路的时序收敛

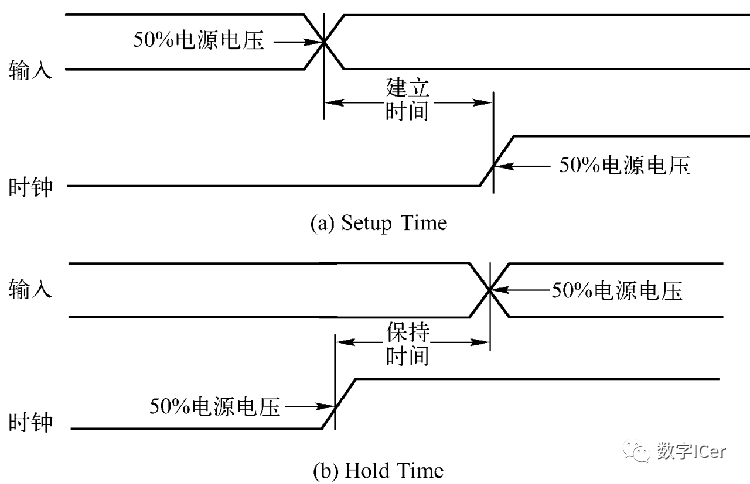

触发器的建立时间和保持时间

触发器的建立时间和保持时间

同步电路设计的优点

在同步设计中,EDA工具可以保证电路系统的时序收敛,有效避免了电路设计中竞争冒险现象

由于触发器只有在时钟边缘才改变取值,很大限度地减少了整个电路受毛刺和噪声影响的可能

同步电路设计的缺点

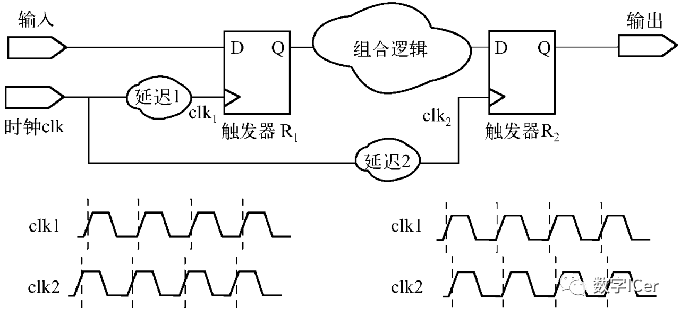

时钟偏斜(Clock Skew)

时钟树综合,需要加入大量的延迟单元,使得电路的面积和功耗大大增加

时钟抖动(Clock Jitter)

时钟偏斜

时钟偏斜

2.全异步电路设计

全异步设计跟同步设计最大的不同就是它的电路中的数据传输可以在任何时候发生,电路中没有一个全局的或局部的控制时钟。

异步电路设计的基本原理

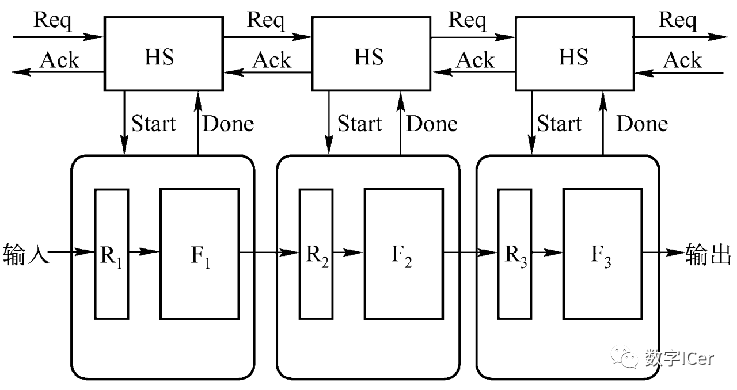

自定时的流水线数据通路

自定时的流水线数据通路

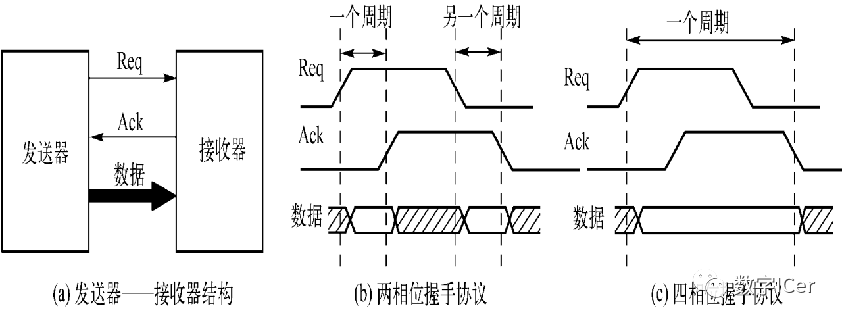

握手协议

握手协议原理

握手协议原理

异步电路设计的优点

模块化特性突出

对信号的延迟不敏感

没有时钟偏斜问题

有潜在的高性能特性

好的电磁兼容性

具有低功耗的特性异步电路设计的缺点

设计复杂

缺少相应的EDA工具的支持

在大规模集成电路设计中应避免采用异步电路设计

3.异步信号与同步电路交互的问题及其解决方法

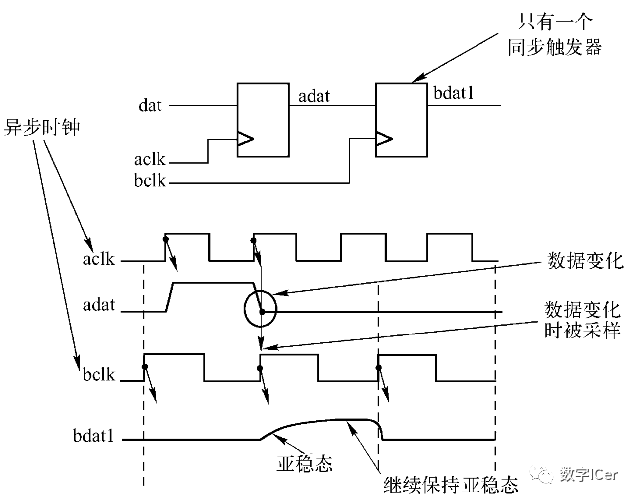

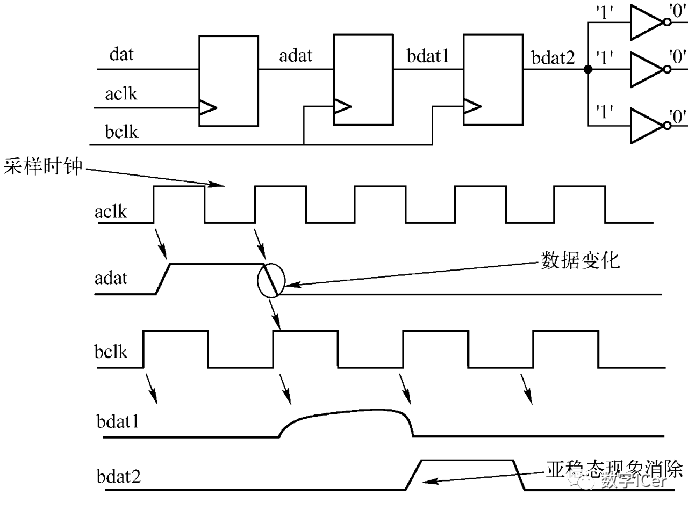

3.1亚稳态现象

亚稳态示意图

亚稳态示意图  亚稳态信号的传播

亚稳态信号的传播

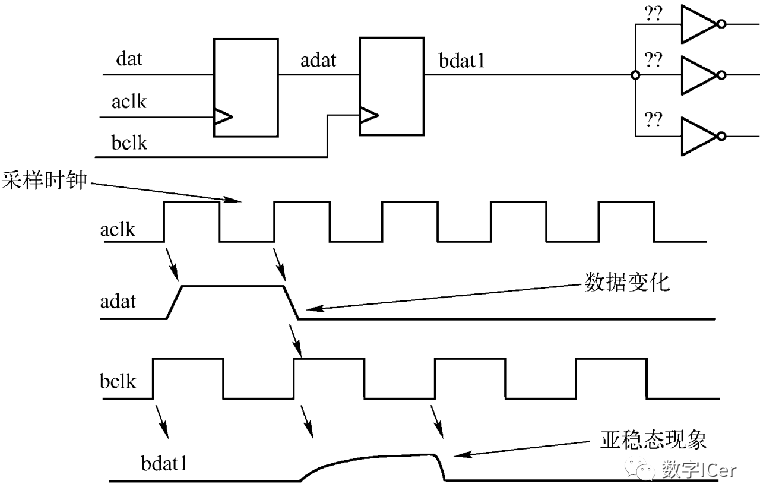

亚稳态问题的解决及其RTL实现

亚稳态现象的解决方法

亚稳态现象的解决方法

modulesynchronizer( bclk,//目的时钟,与aclk异步的时钟 reset_b,//全局异步复位信号 adat,//异步输入信号,工作在aclk bdat,//同步器输出 ); inputbclk; inputreset_b; inputadapt; outputbdat; wirebdat; regbdat1; regbdat2; always@(posedgebclkornegedgereset_b) if(reset_b) {bdat2,bdat1}<= 2 ' b0; else {bdat2,bdat1} <= {bdat1,adat}; assign bdat = bdat2; endmodule

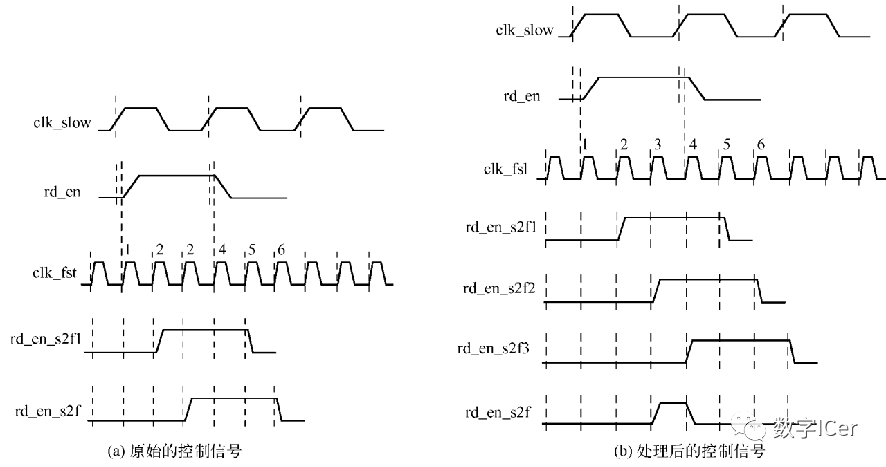

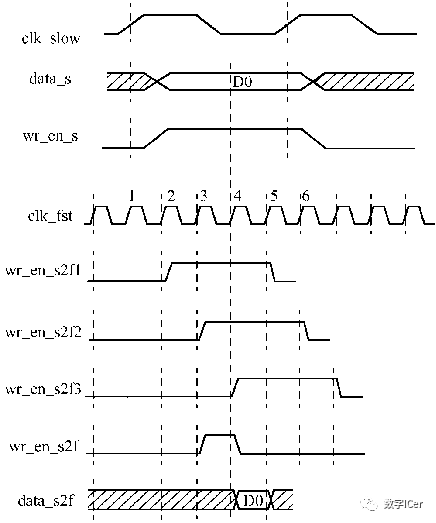

3.2快时钟同步慢时钟域下的异步控制信号

快时钟同步慢时钟信号示意图

快时钟同步慢时钟信号示意图

modulesynchronizer(

clk_fst,

reset_b,

rd_en,

rd_en_s2f

);

inputclk_fst,reset_b,rd_en

outputrd_en_s2f;

wirerd_en_s2f;

regrd_en_s2f1,rd_en_s2f2,rd_en_s2f3

always@(posedgeclk_fstornegedgereset_b)

if(!reset_b)

{rd_en_s2f3,rd_en_s2f2,rd_en_s2f1}<= 3'b111;

else

{rd_en_s2f3,rd_en_s2f2,rd_en_s2f1}<={rd_en_s2f2,rd_en_s2f1,rd_en};

always @ (rd_en_s2f3 or rd_en_s2f2)

case ({rd_en_s2f3,rd_en_s2f2})

2'b01:

rd_en_s2f <= 1'b1;

default:

rd_en_s2f <= 1'b0;

endcase

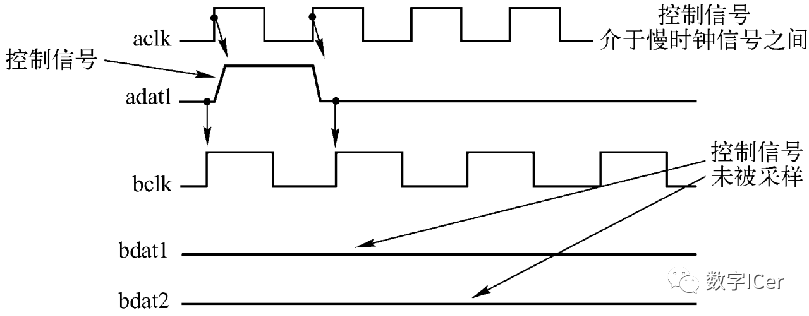

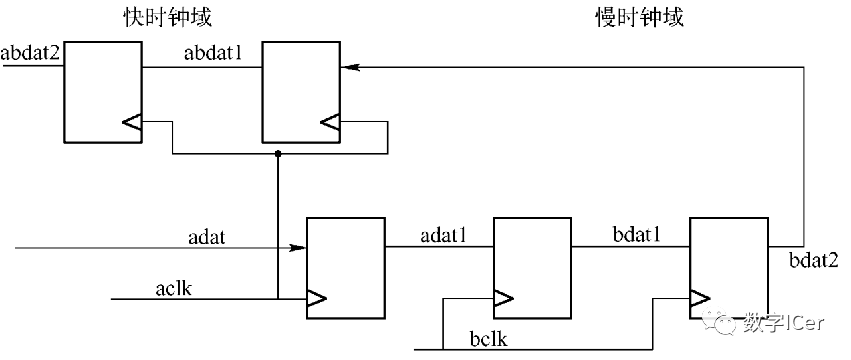

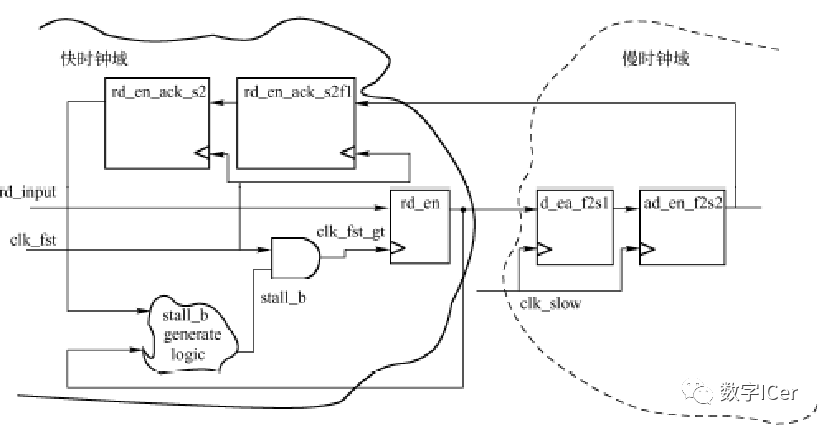

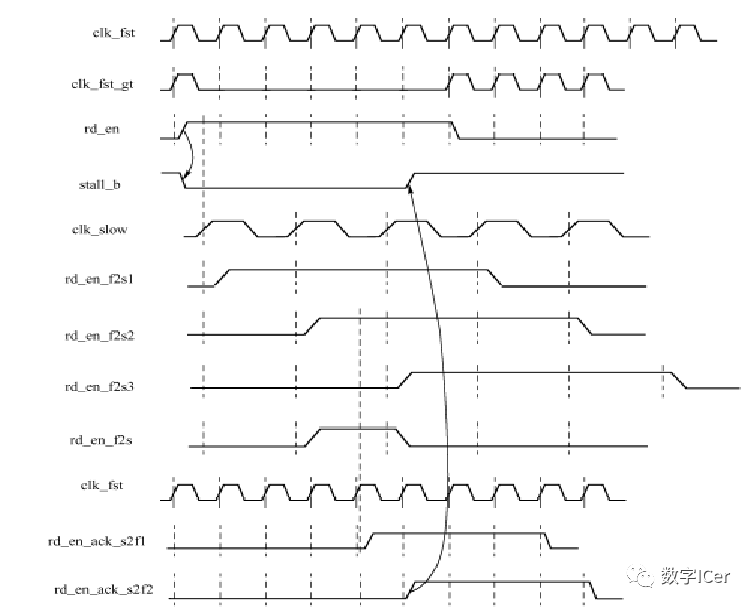

3.3慢时钟同步快时钟域下的异步控制信号

慢时钟同步快时钟信号示意图

慢时钟同步快时钟信号示意图

解决办法 : 握手机制实现方法一

moduleadapt_gen( aclk,//快时钟 reset_b,//系统复位信号 adat,//原始控制信号 abdat2, //从慢时钟域反馈回来的同步控制信号 adat1 //经过保持后的信号输出 ); inputaclk,reset_b,adat,abdat2; outputadat1; regadat1; always@(posedgeaclkornegedgereset_b) if(!reset_b) adat1<= 1'b0; else if (abdat2) adat1 <= 1'b0; else if (adat) adat1 <= 1'b1; endmoudule

解决办法 : 握手机制实现方法二

modulestall_logic( rd_en, rd_en_ ack_s2f, stall_b ); inputrd_en; inputrd_en_ack_s2f; outputstall_b; wirestall_b; always@(rd_enorrd_en_ack_s2f) if(rd_en_ack_s2f) stall_b<= 1'b1; else if (rd_en) stall_b <= 1'b0; else stall_b <= 1'b1; endmodule

3.4异步时钟域的数据同步

握手机制

握手同步异步数据

握手同步异步数据

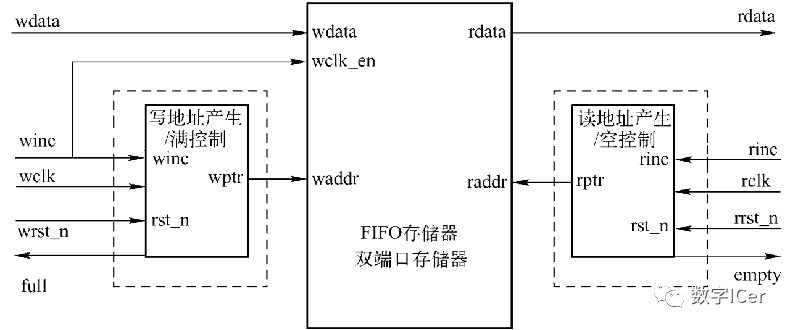

先入先出队列(FIFO)

FIFO结构图

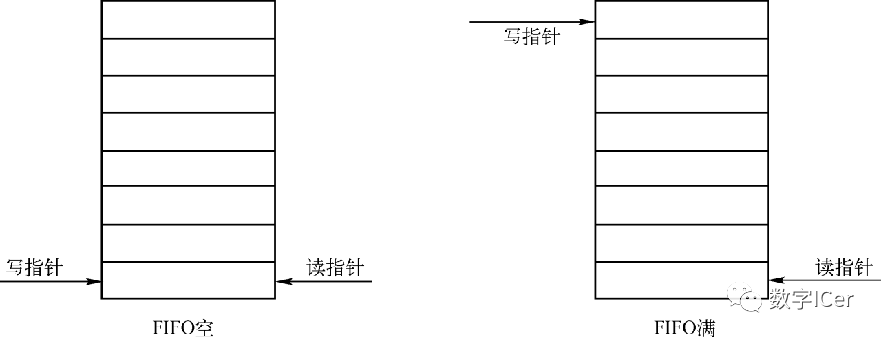

FIFO结构图  FIFO空满示意图

FIFO空满示意图

同步异步时钟FIFO的电路行为

待同步的数据时钟域会在其写信号的控制之下,将数据写入到FIFO中

目的时钟域在发现空标志位无效后,执行FIFO读动作,读出被异步时钟域写入FIFO的数据

如果只要同步一个数据,空标志位再次有效

如果需要同步多个数据,因为FIFO的读/写之间可以不受影响的进行,所以待同步

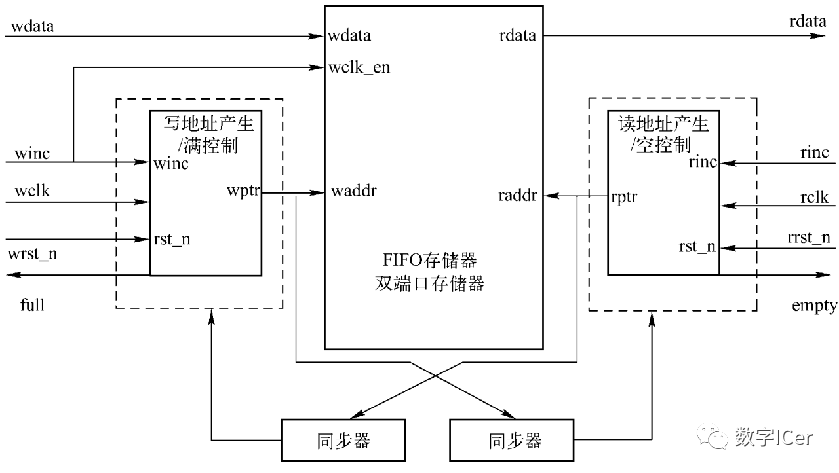

FIFO设计中的亚稳态问题

通常,通过比较读/写指针是否相等来判断FIFO是否为空。而因为读/写指针属于不同的时钟域,两者显然不能直接连到比较器的两端来产生空信号,否则会造成读FIFO的目的时钟域的电路碰到亚稳态现象.

解决办法

以格雷码编码表示读/写指针,用格雷码加法器来实现读/写地址的加一动作

用同步器将读指针同步到FIFO满标志的产生逻辑,同样用同步器将写指针同步到FIFO空标志的产生逻辑中

新的异步FIFO的结构框图

新的异步FIFO的结构框图

4.SoC设计中的时钟规划策略

首先尽可能使用同步设计:

对于同步电路,逻辑综合和时钟树综合等EDA工具能发挥更大的作用,可以用静态时序分析工具分析单时钟同步设计的时序收敛问题

可测性设计(DFT)的插入工作得到最大的简化

其次,注意同步电路设计的缺陷

噪声问题

时钟树上的功耗很大

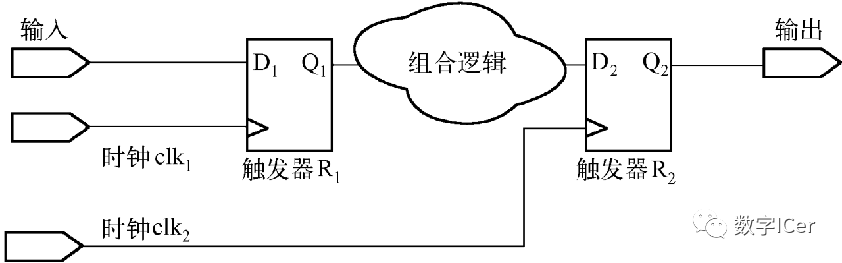

如果必须采用不同的时钟,则要注意

后端设计的复杂化,如约束条件中要考虑多周期路径(Multi Cycle Path)

可测性设计更加复杂,因为此时系统中需要有多条独立的扫描链

越多的时钟域,发生亚稳态的概率就会越大

最后,设计规划中应注意以下几点:

尽可能将不同时钟域的数量减到越少越好

尽可能将异步交互电路归入同一或多个独立的模块,这样不但方便后端设计脚本的书写,也方便代码的阅读

尽可能避免使用电平触发器(Latch),因为静态时序分析会变得复杂,不能得到EDA工具很好的支持

尽可能减小时钟树的延时,因为这个延时可能会造成系统功能失效和多余的功耗;

任何异步时钟域交互的环节都要尽可能避免亚稳态现象.

审核编辑:汤梓红

-

电路设计

+关注

关注

6656文章

2417浏览量

202667 -

同步电路

+关注

关注

1文章

60浏览量

13273 -

异步电路

+关注

关注

2文章

48浏览量

11083

原文标题:同步与异步电路信号交互的问题

文章出处:【微信号:数字ICer,微信公众号:数字ICer】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

同步与异步电路信号交互的问题

同步与异步电路信号交互的问题

评论