(文/程文智)三星电子今年7月25日在韩国京畿道华城园区V1生产线(EUV专用)为采用了新一代全环绕栅极(Gate All Around,简称GAA)晶体管制程节点的3nm芯片晶圆代工产品举行了出厂仪式。才过4个月不到,韩国媒体Naver就爆出,三星3nm制程的良率非常低,不足20%。而且其5nm和4nm节点的良率问题也迟迟没有得到改善。

其实,三星电子从2000年初就已经开始了对GAA晶体管结构的研究。自2017年开始,将其正式应用到3纳米工艺,并于今年6月宣布启动利用GAA技术的3纳米工艺的量产。是全球首家将GAA晶体管结构用于晶圆制造的代工企业。据悉,我国的一家矿机芯片企业PanSemi(磐矽半导体)是三星电子的第一家客户,目前也可能是其唯一的客户。

据报道,三星电子为了解决良率问题,找到了美国的Silicon Frontline Technology,向这家企业寻求帮助。据说目前进展情况还不错。

那么,三星电子在GAA上花的时间超过了20年,为何良率问题迟迟没有得到解决呢?问题究竟出在了哪里?我们先从芯片的最基础单元------晶体管结构的发展说起,然后看看有什么应对之策。

晶体管结构的发展历史

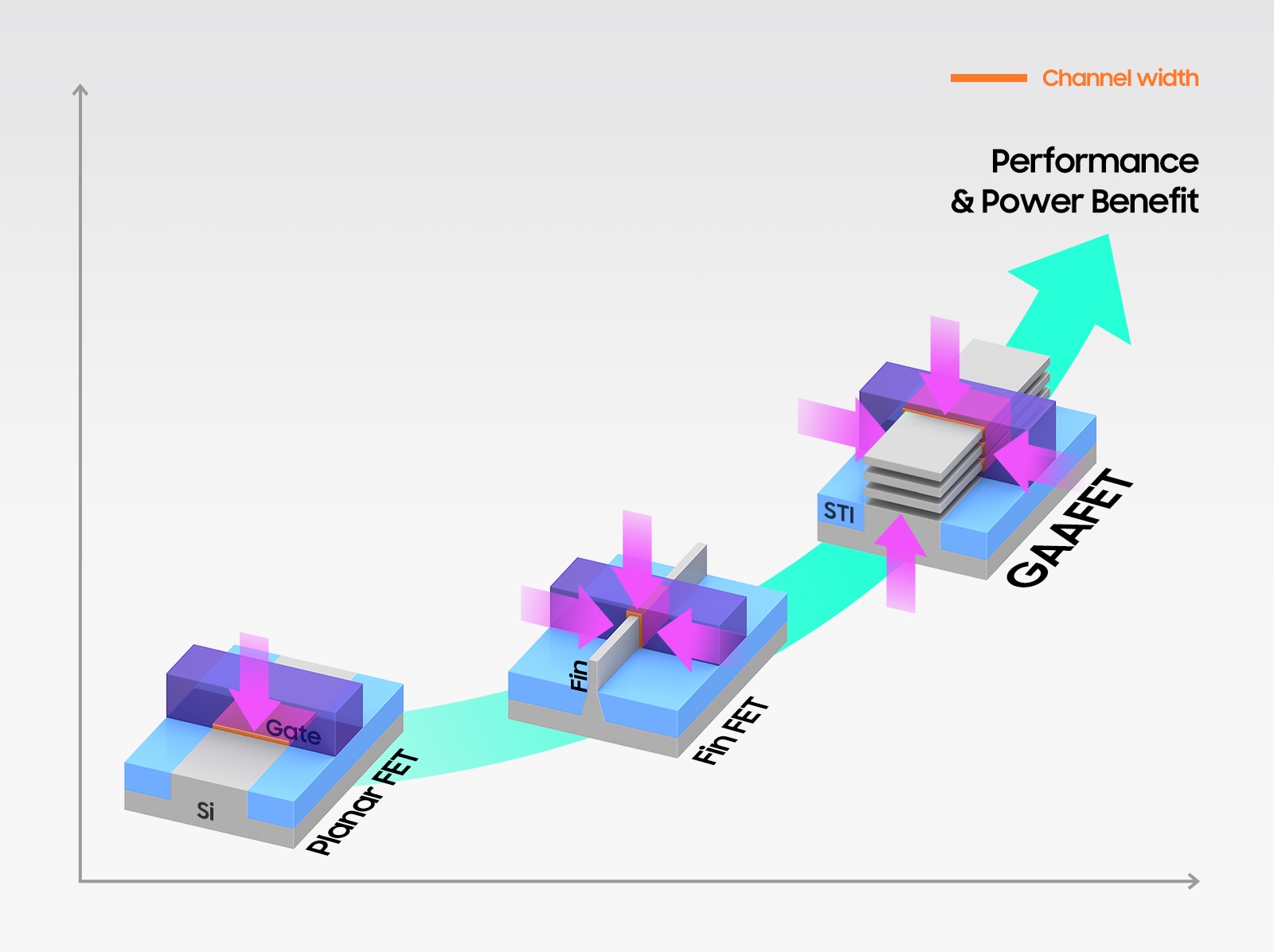

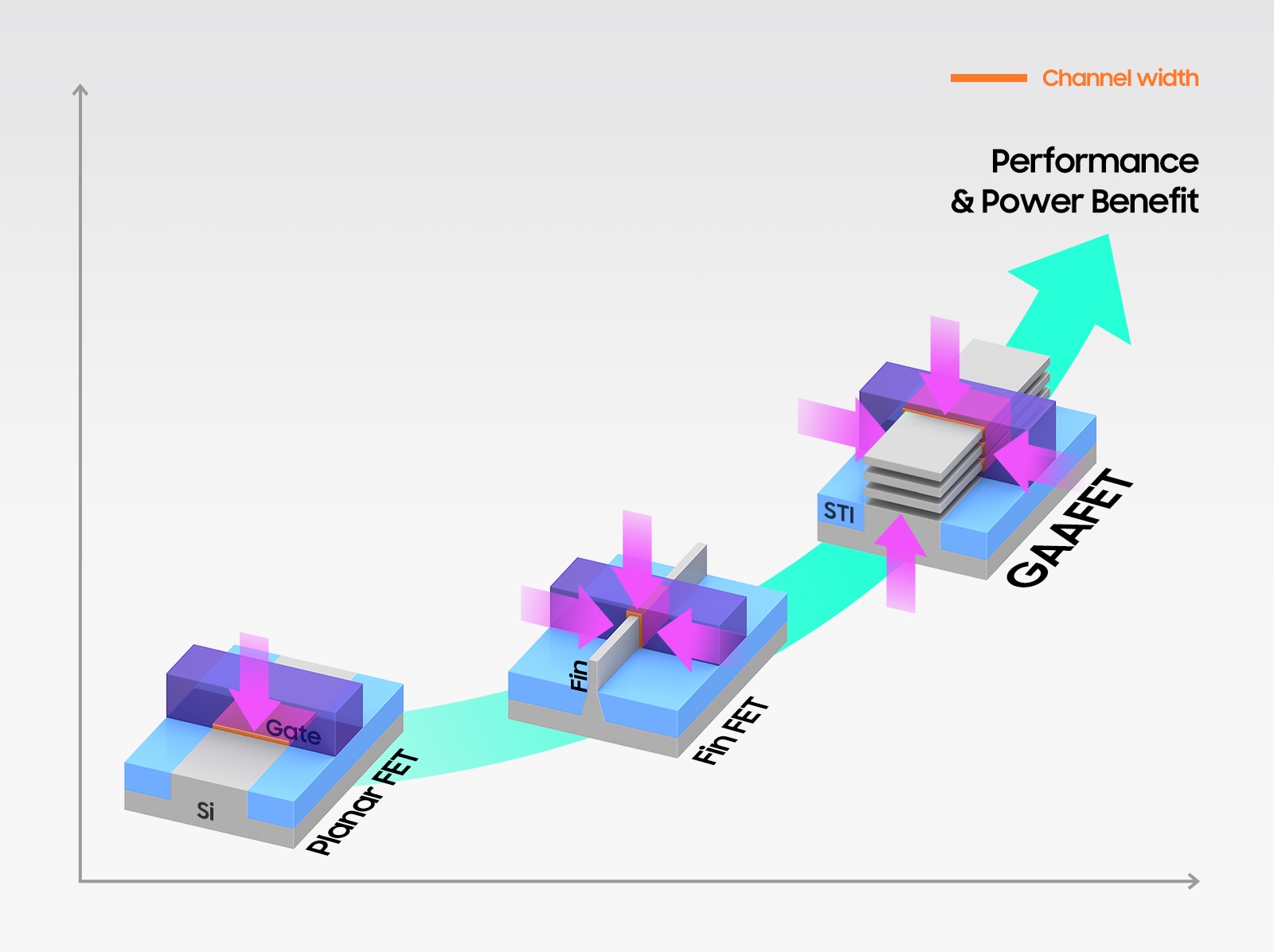

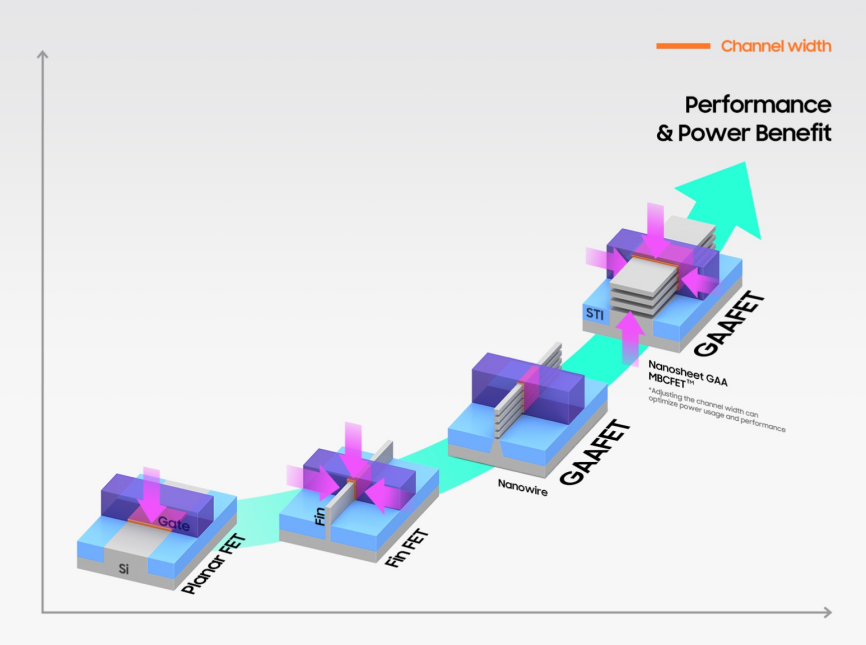

半导体芯片其实是众多晶体管(Transistor)的集合,而晶体管其实就是一个小的开关。一个晶体管就代表了一个0或者1,也就是所谓的一个位元。在20nm以上的制程中,使用的晶体管被称为金属氧化物半导体场效应管(MOSFET:Metal Oxide Semiconductor FET);20nm~3nm,采用的是鳍式场效应晶体管(Fin FET: Fin Field Effected Transistor);3nm以下,采用的则是全环绕栅极场效应晶体管(GAAFET:Gate All Around Field Effect Transistor)。

图:晶体管的结构发展(来源:三星)

为何会如此演进呢?主要是因为晶体管的工作原理,在晶体管内部,科学家定义了一个栅极长度(Gate Length)的概念,这是电子流通的方向,而其短边就是所谓的制程。

原理是在金属栅极上加一个电压来控制电子的导通和关闭。电子能够导通过去就代表1,如果关断则代表0。这个开关就是靠栅极施加电压来造成电场来控制的,可电场的主要影响在接触面上,如果栅极的长度越做越小,粉色的接触面积就会越来越小,当小到一个程度,要关住电子的时候,就会关不住。锁不住的电子就会偷偷溜过去。因此,先进制程中漏电流就会变大。

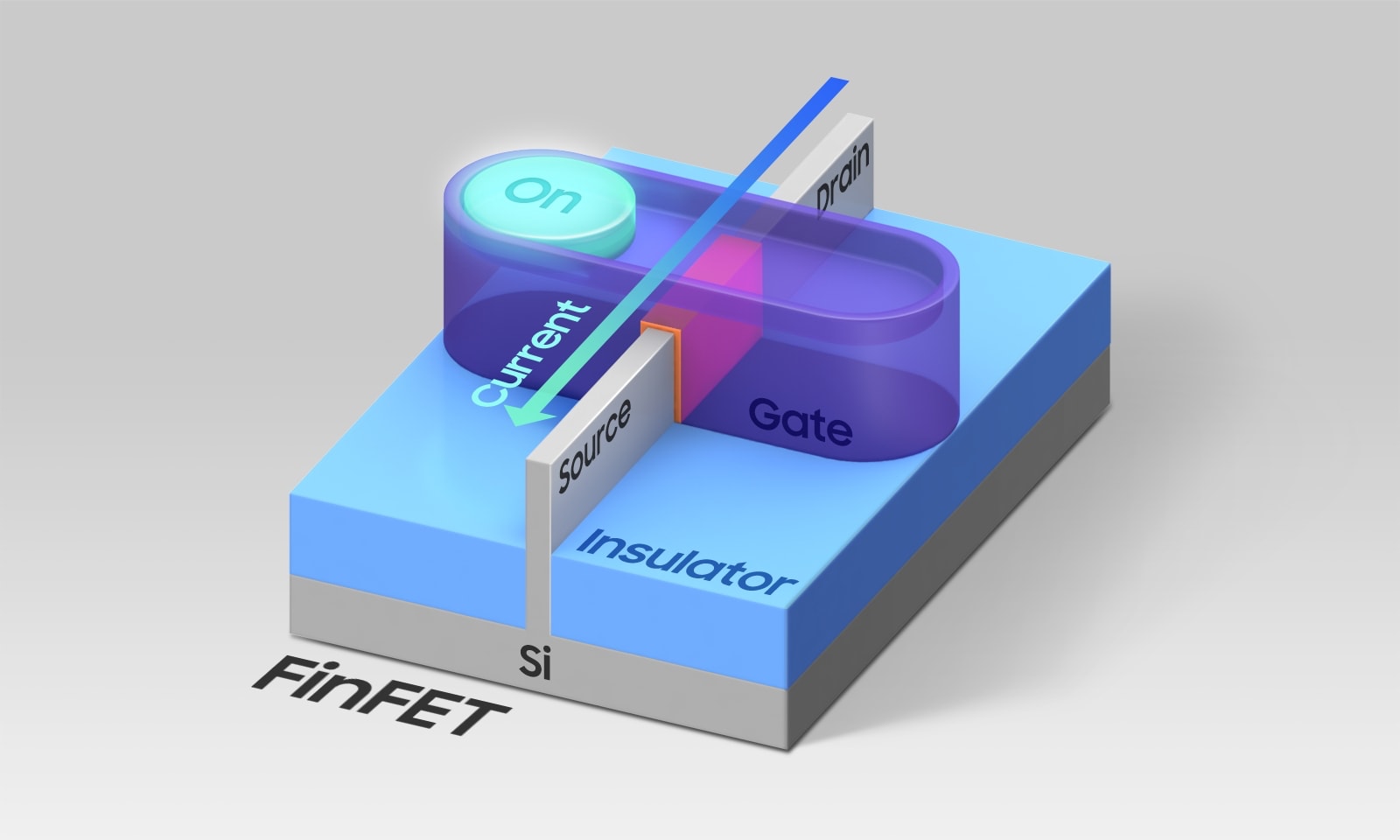

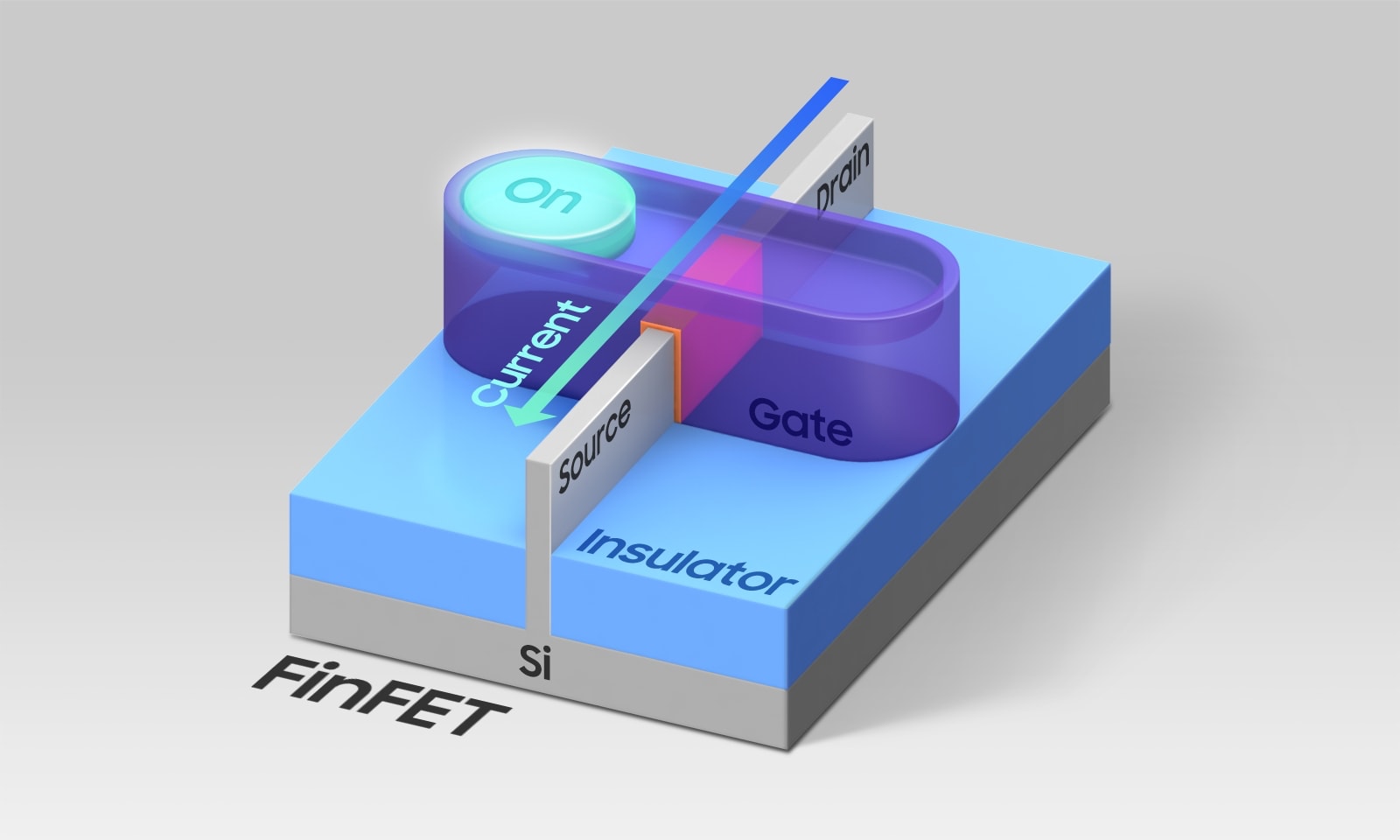

图:FinFET晶体管工作原理(来源:三星)

解决这个问题的办法就是增大栅极与电子通道的接触面积,接触面积越大,控制效果越好。所以到20nm以下就改用鳍式场效应晶体管,加电压的时候就变成粉色这部分面积就增加了,所以效果会比较好。电场的作用比较强,可以锁住电子不会漏电。

到了3nm以下,实在太小了,接触面积又不够了,怎么办呢?只好上下左右,统统把它包起来,用栅极把电子通道包起来,成为了GAAFET,这样的控制效果会比较好。

就目前来说,每一家晶圆代工厂大概都是用这样的方式去制作。

良率问题低迷该怎么办?

三星电子这次先于台积电推出3nm制程,但情况并没有好转,良率不足20%,这成本就有点高了。加上此前就由于在4nm和5nm制程良率无法得到改善,而让大客户高通和英伟达等大客户转单台积电了。此次要是还不能解决良率问题,可能大客户就此失去了。

为了能够更好地解决良率问题,三星电子此次找上了美国厂商Silicon Frontline Technology,让他们帮忙协助其提高3nm GAA结构的良率。

根据Silicon Frontline Technology官网信息,该公司位于加利福尼亚州圣何塞,主要提供半导体设计和验证解决方案。该公司为布局后验证提供有保证的准确和有保证的快速电阻、电容、ESD 和热分析,其产品已被70多家客户使用,其中包括全球前25家半导体供应商中的12家,得到领先代工厂的认可和使用,并已用于500多种设计中。而且,客户已经使用他们的技术解决了10nm、14nm、28nm、40nm、ADC、Serdes、敏感模拟电路、图像传感器、存储器、定制数字设计和电源设备的问题。

其主要的经验在于为晶圆厂提供静电放电(ESD)预防技术,而静电放电是晶圆生产过程中产生缺陷的主要原因,据悉也是三星3nm GAA技术的良率过低的重要原因之一。Silicon Frontline Technology公司已经藉由水质和静电放电(ESD)预防技术降低生产过程中的缺陷,以提高晶圆的生产良率。

虽然三星号称已经透过整合其合作伙伴使用的技术获得了积极成果,但实际成果还需要在未来几个月内持续观察。

据了解,目前市面上所做的失效分析中,90%以上的失效都是静电放电所造成的。根据电测结果,失效模式包含开路、短路或漏电、参数漂移、功能失效等。根据失效原因,失效模式可以分为电力过应、静电放电导致的失效、制造工艺不良导致的失效等。

静电放电是如何产生的呢?在芯片的制造过程中,半导体设备与芯片上的金属层之间,在制造过程中可能会发生静电放电。静电放电失效可以归结为两种情形,一是静电放电直接作用在了芯片上;二是静电放电干扰了生产的设备正常运行,或者是干扰了外部电路环境。

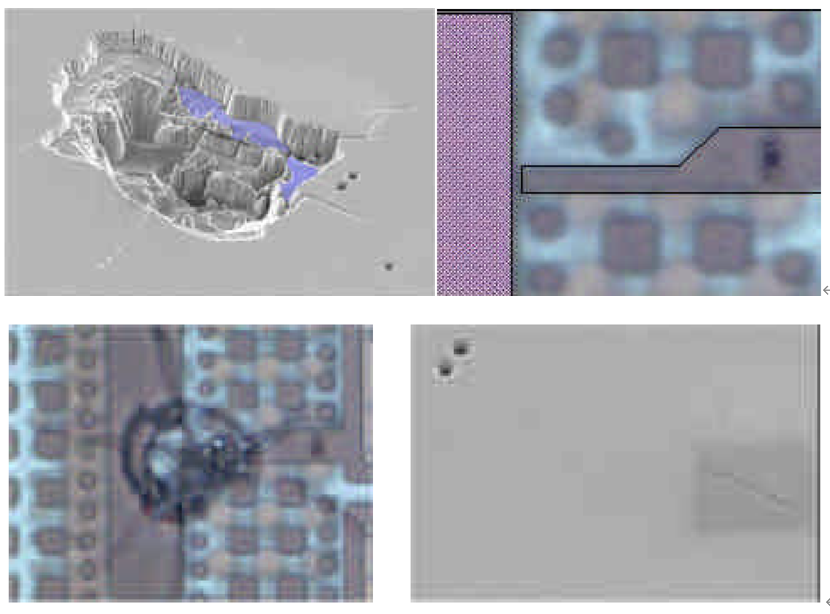

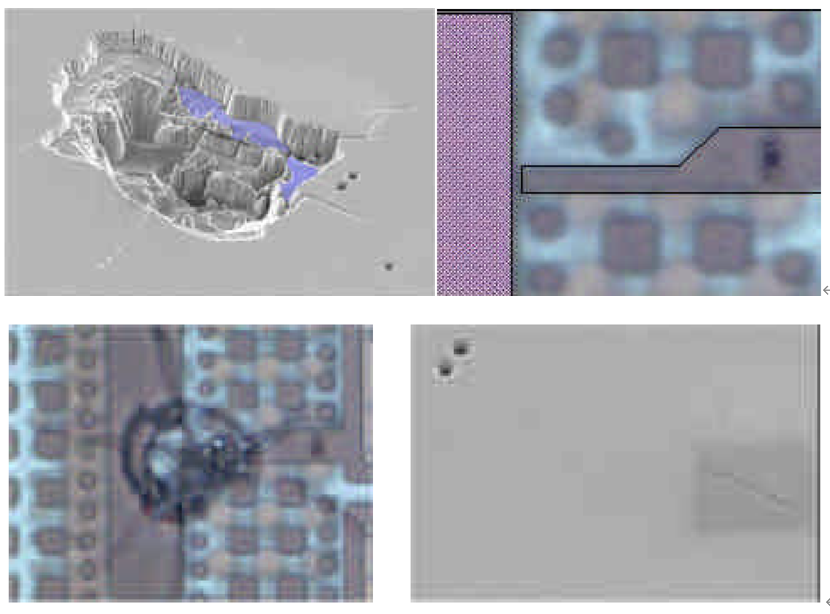

图:充电诱导损伤

上图就是所谓的充电诱导损伤(CID,Charging Induced Damage),就是当芯片在生产过程中,跟半导体设备接触或者接近,可能产生充电诱导损伤,这个图是晶圆表面被静电打坏的照片,仔细放大看,就会发现,实际上就是里面的某一个晶体管被损伤了,如果用显微镜仔细看,就会发现这颗IC基本上被打坏了。

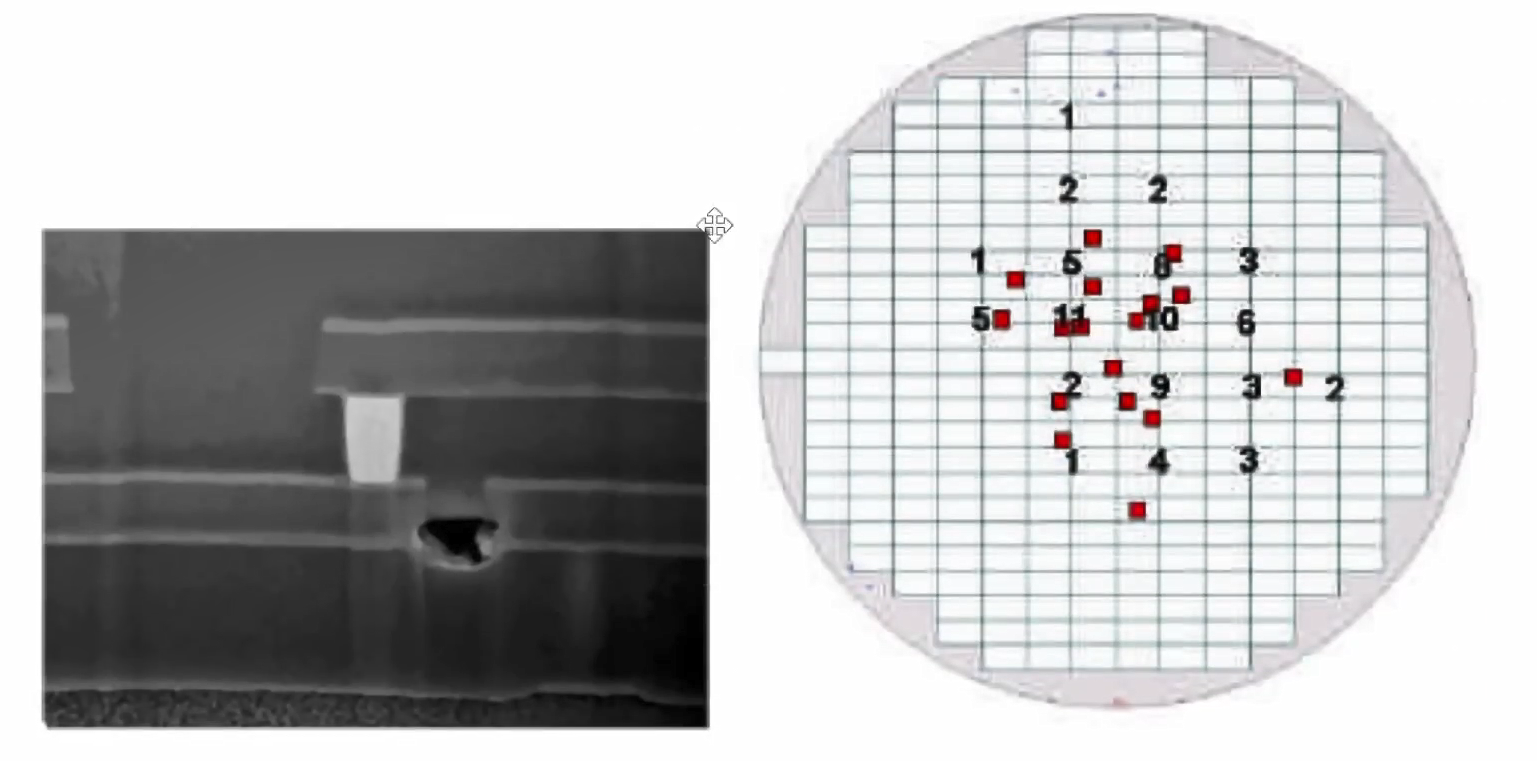

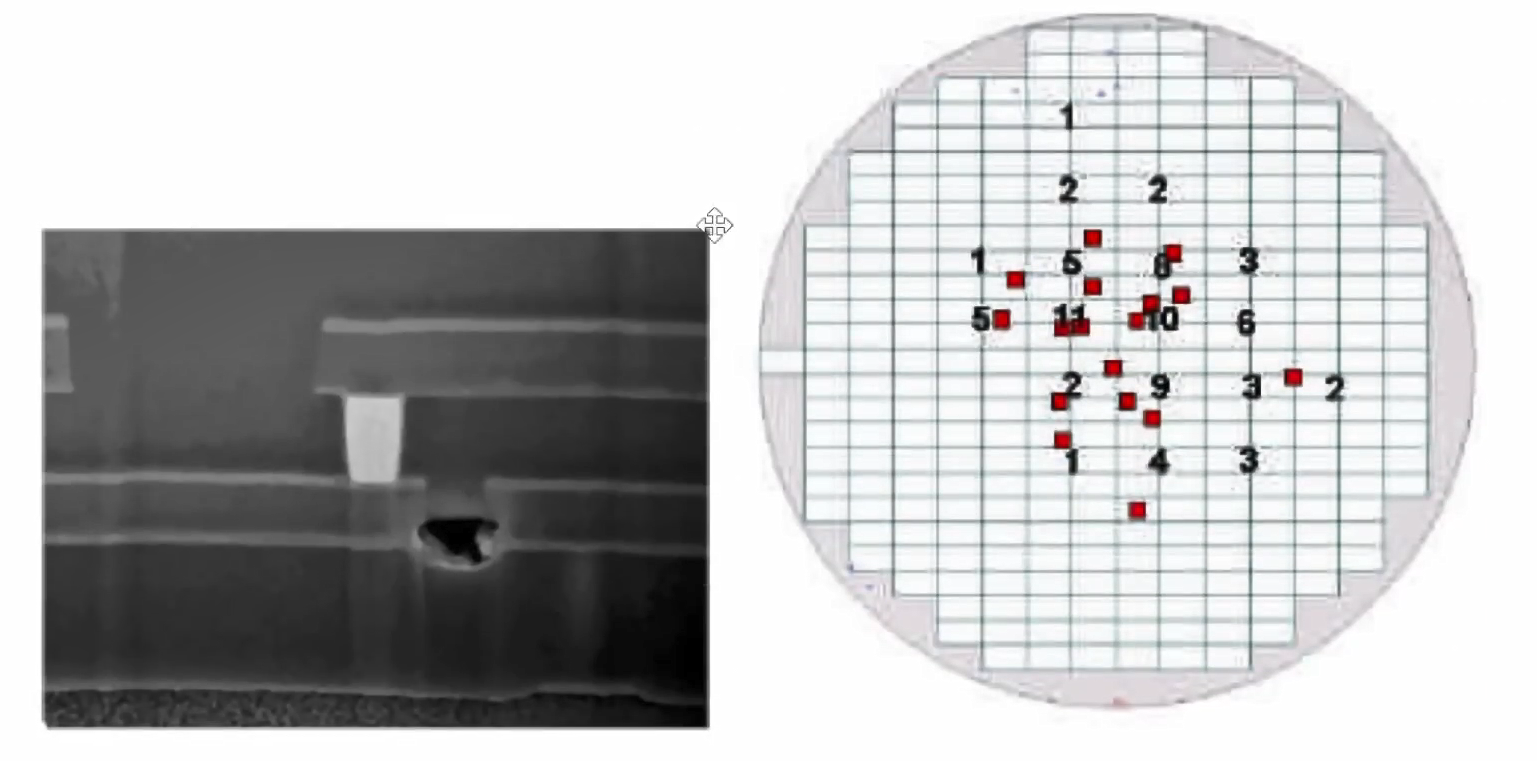

图:晶圆被静电打坏的剖面图

上图中左图表示的是一个被静电打坏的现象。从侧面看,你会发现,多层金属导线当发生静电打坏的现象,这个地方就会有缺陷,这时候,这颗芯片就坏掉了。通过分析可以发现在晶圆的某些位置,特别容易发生静电放电损坏芯片的现象。比入上图右图所示的红点,就是实验室中,科研人员测得的在某个条件下,某些位置容易打伤芯片。

结语

三星遇到的一直都是良率的问题,所以这次,他们想通过Silicon Frontline Technology提供的静电放电模拟软件协助其找到原因,进而解决良率的问题。如果此次他们能够成功解决良率问题,那么在未来的先进制程竞争中超越台积电。

毕竟台积电目前的3nm制程采用的仍然是FinFET技术,到2025年2nm时,他们才会采用GAAFET技术。而三星此次如果解决了良率问题,那么在2nm竞争时,将会比台积电多出3年的实践经验。因此,两家公司的决战点应该会在2025年之后。

其实,三星电子从2000年初就已经开始了对GAA晶体管结构的研究。自2017年开始,将其正式应用到3纳米工艺,并于今年6月宣布启动利用GAA技术的3纳米工艺的量产。是全球首家将GAA晶体管结构用于晶圆制造的代工企业。据悉,我国的一家矿机芯片企业PanSemi(磐矽半导体)是三星电子的第一家客户,目前也可能是其唯一的客户。

据报道,三星电子为了解决良率问题,找到了美国的Silicon Frontline Technology,向这家企业寻求帮助。据说目前进展情况还不错。

那么,三星电子在GAA上花的时间超过了20年,为何良率问题迟迟没有得到解决呢?问题究竟出在了哪里?我们先从芯片的最基础单元------晶体管结构的发展说起,然后看看有什么应对之策。

晶体管结构的发展历史

半导体芯片其实是众多晶体管(Transistor)的集合,而晶体管其实就是一个小的开关。一个晶体管就代表了一个0或者1,也就是所谓的一个位元。在20nm以上的制程中,使用的晶体管被称为金属氧化物半导体场效应管(MOSFET:Metal Oxide Semiconductor FET);20nm~3nm,采用的是鳍式场效应晶体管(Fin FET: Fin Field Effected Transistor);3nm以下,采用的则是全环绕栅极场效应晶体管(GAAFET:Gate All Around Field Effect Transistor)。

图:晶体管的结构发展(来源:三星)

为何会如此演进呢?主要是因为晶体管的工作原理,在晶体管内部,科学家定义了一个栅极长度(Gate Length)的概念,这是电子流通的方向,而其短边就是所谓的制程。

原理是在金属栅极上加一个电压来控制电子的导通和关闭。电子能够导通过去就代表1,如果关断则代表0。这个开关就是靠栅极施加电压来造成电场来控制的,可电场的主要影响在接触面上,如果栅极的长度越做越小,粉色的接触面积就会越来越小,当小到一个程度,要关住电子的时候,就会关不住。锁不住的电子就会偷偷溜过去。因此,先进制程中漏电流就会变大。

图:FinFET晶体管工作原理(来源:三星)

解决这个问题的办法就是增大栅极与电子通道的接触面积,接触面积越大,控制效果越好。所以到20nm以下就改用鳍式场效应晶体管,加电压的时候就变成粉色这部分面积就增加了,所以效果会比较好。电场的作用比较强,可以锁住电子不会漏电。

到了3nm以下,实在太小了,接触面积又不够了,怎么办呢?只好上下左右,统统把它包起来,用栅极把电子通道包起来,成为了GAAFET,这样的控制效果会比较好。

就目前来说,每一家晶圆代工厂大概都是用这样的方式去制作。

良率问题低迷该怎么办?

三星电子这次先于台积电推出3nm制程,但情况并没有好转,良率不足20%,这成本就有点高了。加上此前就由于在4nm和5nm制程良率无法得到改善,而让大客户高通和英伟达等大客户转单台积电了。此次要是还不能解决良率问题,可能大客户就此失去了。

为了能够更好地解决良率问题,三星电子此次找上了美国厂商Silicon Frontline Technology,让他们帮忙协助其提高3nm GAA结构的良率。

根据Silicon Frontline Technology官网信息,该公司位于加利福尼亚州圣何塞,主要提供半导体设计和验证解决方案。该公司为布局后验证提供有保证的准确和有保证的快速电阻、电容、ESD 和热分析,其产品已被70多家客户使用,其中包括全球前25家半导体供应商中的12家,得到领先代工厂的认可和使用,并已用于500多种设计中。而且,客户已经使用他们的技术解决了10nm、14nm、28nm、40nm、ADC、Serdes、敏感模拟电路、图像传感器、存储器、定制数字设计和电源设备的问题。

其主要的经验在于为晶圆厂提供静电放电(ESD)预防技术,而静电放电是晶圆生产过程中产生缺陷的主要原因,据悉也是三星3nm GAA技术的良率过低的重要原因之一。Silicon Frontline Technology公司已经藉由水质和静电放电(ESD)预防技术降低生产过程中的缺陷,以提高晶圆的生产良率。

虽然三星号称已经透过整合其合作伙伴使用的技术获得了积极成果,但实际成果还需要在未来几个月内持续观察。

据了解,目前市面上所做的失效分析中,90%以上的失效都是静电放电所造成的。根据电测结果,失效模式包含开路、短路或漏电、参数漂移、功能失效等。根据失效原因,失效模式可以分为电力过应、静电放电导致的失效、制造工艺不良导致的失效等。

静电放电是如何产生的呢?在芯片的制造过程中,半导体设备与芯片上的金属层之间,在制造过程中可能会发生静电放电。静电放电失效可以归结为两种情形,一是静电放电直接作用在了芯片上;二是静电放电干扰了生产的设备正常运行,或者是干扰了外部电路环境。

图:充电诱导损伤

上图就是所谓的充电诱导损伤(CID,Charging Induced Damage),就是当芯片在生产过程中,跟半导体设备接触或者接近,可能产生充电诱导损伤,这个图是晶圆表面被静电打坏的照片,仔细放大看,就会发现,实际上就是里面的某一个晶体管被损伤了,如果用显微镜仔细看,就会发现这颗IC基本上被打坏了。

图:晶圆被静电打坏的剖面图

上图中左图表示的是一个被静电打坏的现象。从侧面看,你会发现,多层金属导线当发生静电打坏的现象,这个地方就会有缺陷,这时候,这颗芯片就坏掉了。通过分析可以发现在晶圆的某些位置,特别容易发生静电放电损坏芯片的现象。比入上图右图所示的红点,就是实验室中,科研人员测得的在某个条件下,某些位置容易打伤芯片。

结语

三星遇到的一直都是良率的问题,所以这次,他们想通过Silicon Frontline Technology提供的静电放电模拟软件协助其找到原因,进而解决良率的问题。如果此次他们能够成功解决良率问题,那么在未来的先进制程竞争中超越台积电。

毕竟台积电目前的3nm制程采用的仍然是FinFET技术,到2025年2nm时,他们才会采用GAAFET技术。而三星此次如果解决了良率问题,那么在2nm竞争时,将会比台积电多出3年的实践经验。因此,两家公司的决战点应该会在2025年之后。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片制程

+关注

关注

0文章

51浏览量

4688

发布评论请先 登录

相关推荐

性能杀手锏!台积电3nm工艺迭代,新一代手机芯片交战

电子发烧友网报道(文/李弯弯)近日消息,联发科、高通新一波5G手机旗舰芯片将于第四季推出,两大厂新芯片都以台积电3nm制程生产,近期进入投片阶段。 在台积电

三星3nm良率仅20%,仍不放弃Exynos 2500处理器,欲打造“十核怪兽”

,导致Exynos 2500良率不佳的原因是,这颗SoC基于三星第二代3nm GAA制程工艺——SF3工艺,然而目前第二代SF

台积电产能爆棚:3nm与5nm工艺供不应求

台积电近期成为了高性能芯片代工领域的明星企业,其产能被各大科技巨头疯抢。据最新消息,台积电的3nm和5nm工艺产能利用率均达到了极高水平,其中3nm将达到100%,而5

联发科将发布安卓阵营首颗3nm芯片

联发科正式宣告,将于10月9日盛大揭幕其新一代MediaTek天玑旗舰芯片发布会,届时将震撼推出天玑9400移动平台。这款芯片不仅是联发科迄今为止最为强大的手机处理器,更标志着安卓阵营正式迈入3nm工艺时代,成为业界首颗采用台积

台积电3nm制程需求激增,全年营收预期上调

台积电近期迎来3nm制程技术的出货高潮,预示着其在半导体制造领域的领先地位进一步巩固。随着苹果iPhone 16系列新机发布,预计搭载的A18系列处理器将采用台积电3nm工艺,这一消息直接推动了台积电

消息称台积电3nm/5nm将涨价,终端产品或受影响

据业内手机晶片领域的资深人士透露,台积电计划在明年1月1日起对旗下的先进工艺制程进行价格调整,特别是针对3nm和5nm工艺制程,而其他工艺制程

三星3nm芯片良率低迷,量产前景不明

近期,三星电子在半导体制造领域遭遇挑战,其最新的Exynos 2500芯片在3nm工艺上的生产良率持续低迷,目前仍低于20%,远低于行业通常要求的60%量产标准。这一情况引发了业界对三

台积电3nm工艺稳坐钓鱼台,三星因良率问题遇冷

近日,全球芯片代工领域掀起了不小的波澜。据媒体报道,台积电在3nm制程的芯片代工价格上调5%之后,依然收获了供不应求的订单局面。而与此同时,韩国的三星电子在

英特尔3nm制程工艺“Intel 3”投入大批量生产

据外媒最新报道,全球知名的处理器大厂英特尔在周三宣布了一个重要的里程碑:其先进的3nm级制程工艺技术“Intel 3”已在两个工厂正式投入大批量生产。这一技术的突破,无疑将为英特尔在超

AMD计划采用三星3nm GAA制程量产下一代芯片

在近日于比利时微电子研究中心(imec)举办的2024年全球技术论坛(ITF World 2024)上,AMD首席执行官苏姿丰透露了公司的最新技术动向。她表示,AMD将采用先进的3nm GAA(Gate-All-Around)制程技术来量产其下一代

三星电子澄清:3nm芯片并非更名2nm,下半年将量产

李时荣声称,“客户对代工企业的产品竞争力与稳定供应有严格要求,而4nm工艺已步入成熟良率阶段。我们正积极筹备后半年第二代3nm工艺及明年2nm

三星电子3nm工艺良率低迷,始终在50%左右徘徊

据韩国媒体报道称,三星电子旗下的3纳米工艺良品比例仍是一个问题。报道中仅提及了“3nm”这一笼统概念,并没有明确指出具体的工艺类型。知情者透露,尽管有部分分析师认为其已经超过60%

三星3nm良率 0%!

来源:EETOP,谢谢 编辑:感知芯视界 Link 近期韩媒DealSite+报道,表示三星的3nm GAA生产工艺存在问题,在尝试生产适用于Galaxy S25 /S25+手机的Exynos

台积电3nm工艺预计2024年产量达80%

据悉,2024年台积电的第二代3nm工艺(称为N3E)有望得到更广泛运用。此前只有苹果有能力订购第一代N3B高端晶圆。经过解决工艺难题及提升产量后

芯片制程到3nm后如何突破良率难题?

芯片制程到3nm后如何突破良率难题?

评论