本文对如何在一个工程里例化和使用多个BSCANE2模块做一个简单说明。

BSCANE2模块是FPGA的一种特殊硬核模块,用于联通外部JTAG引脚和内部逻辑,构建FPGA内部的用户扫描链。关于BSCANE2的用法, 有一个基于7系列器件的参考设计:

https://support.xilinx.com/s/article/1181110?language=zh_CN

在UltraScale/UltraScale+器件上, BSCANE2的用法类似。

UG570里面提到,UltraScale/UltraScale+的BSCANE2模块多达4个,可以在设计中全部例化,并用JTAG_CHAIN属性加以区分。之后,就可以用使用JTAG的指令USER1到USER4来对应操作了。

本文对如何在一个工程里例化和使用多个BSCANE2模块做一个简单说明。工程基于Xilinx的KCU105开发板,同时例化两个BSCANE2模块,并使用ILA去观测两个模块的信号。由于ILA的实现同样需要借助一个BSCANE2,由Vivado在综合后自动插入设计,所以其实是使用了全部四个中的三个BSCANE2。

工程文件请点击阅读原文查看并下载。

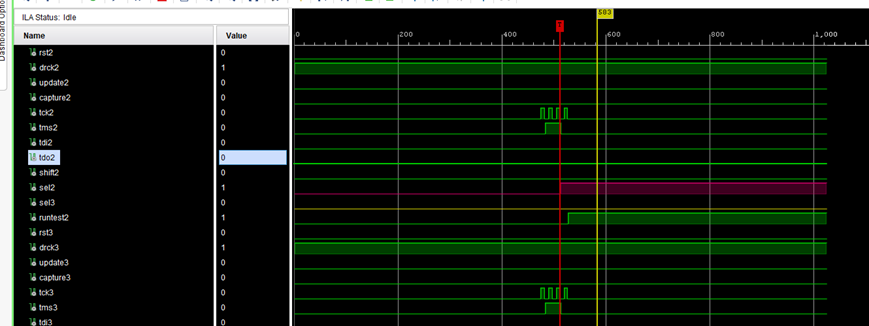

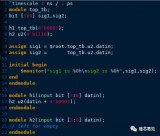

这个设计简单利用KCU105板上4盏User LED灯GPIO_LED_2/3/4/5来展示一个counter最低4位的结果。BSCANE2_inst2对应User Scan Chain 2, BSCANE3_inst3对应User Scan Chain3。通过JTAG指令发送USERx指令,可以观测到对应的sel信号会置高有效。当选中User chain 2时,sel2有效,counter收到工作信号0101, counter随时钟信号递增;当选中User Chain 3时,counter收到工作信号1010, counter值递减操作。

调试步骤:

1. 打开Vivado,按照常规流程下载好bit和ltx文件

2. 由于调试需要进入JTAG模式,先关闭上个步骤正常/自动打开的target, 但此时FPGA已经处于工作状态(不要掉电),Tcl console输入:close_hw_target

3. 以JTAG调试的方式重新打开链:

open_hw_target -jtag_mode 1

4. 运行:

refresh_hw_device [lindex [get_hw_devices xcku040_0] 0]

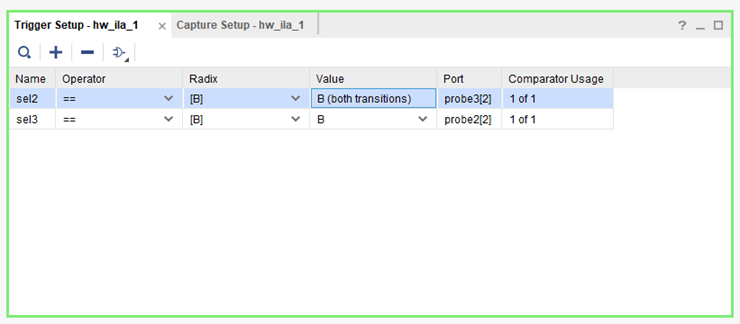

看到ILA的界面。我们主要是对比观测可以起到控制作用的sel2和sel3,在Trigger中,将其设为B (Both Transitions) 进行捕捉:

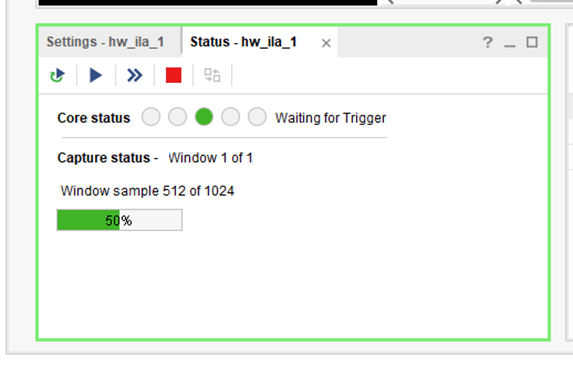

进入捕捉等候状态:

5. 从BSDL文件中,查询到KU040对应的USER指令:

"USER2 (000011)," & -- Not available until after configuration

"USER3 (100010)," & -- Not available until after configuration

6. 选择USER Chain 2和Chain 3的指令分别如下;依次输入,可以看到LED灯增减方向会有变化。

scan_ir_hw_jtag 6 -tdi 03

scan_ir_hw_jtag 6 -tdi 22

7. 对应查看ILA波形,可以看到第一条指令USER2执行时,捕捉到的sel2:

需要注意的是,两条chain对应的JTAG信号都会产生toggle动作,所以实际工程中,需要依靠不同的sel信号来区分并做对应的控制。

-

FPGA

+关注

关注

1635文章

21837浏览量

608318 -

模块

+关注

关注

7文章

2750浏览量

48154 -

Xilinx

+关注

关注

71文章

2173浏览量

122826

原文标题:开发者分享|如何在设计中例化和使用多个 BSCANE2 模块

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CMU通道例化与普通GXB例化的差异比较

例说FPGA连载62:电子点菜单之FIFO例化说明

如何在RTC程序中设置多个报警?

基于7系列的ISE版本的参考设计

如何在UltraScale+设计中使用UltraRAM模块

BSCANE2模块是FPGA中的一个特殊硬核模块

开发者分享 | 如何在设计里例化并使用BSCANE2模块 (一)

如何在设计中例化和使用多个BSCANE2模块

如何在设计中例化和使用多个BSCANE2模块

评论