作者:一博科技高速先生成员 刘春

随着信号速率的不断提高,对信号时序的要求也越来越严格。在PCB设计中,我们等长的最终目的都是为了等时,以满足信号的时序要求。因此,需要我们对信号在传输线上的时延有一定的了解,下面小编将会通过理论分析和利用SIGRITY软件进行仿真验证跟大家一起深入的了解信号在传输线上的时延情况。

时延

这里指的是传输线上的时延,即信号在通过整个传输线所用的时间。

信号的传输速度

从时延的描述上,不难发现必然还会存在两个不可或缺的量,哈哈,不用说相信大家已经知道了,那就是信号的传输速度和传输线的长度。长度这里自不必说,这里我们需要重点关注的是信号的传输速度。当信号在传输线上传输时,其速度就取决于信号传输线在其周围介电特性环境中电场和磁场建立的速度。可用如下关系式描述:

而真空中光速表示为:

因为几乎所有非铁磁性材料相对磁导率都为1,所以介质中信号的速度可简化为:

到这里,想必大家都发现了,我们常常听到的信号在传输线中的传输速度可以用6mil/ps来估算的原因了吧。因为大多数板材聚合物的介电常数都在4左右,通过上述简化后的关系式可轻松得出信号在传输线上的大致传输速度,约6mil/ps。

从上面的关系式,我们还可以知道板材的介电常数是决定信号传输速度的主要因素,介质的介电常数越大,信号的传输速度越慢,反之则越快。在知道了信号的传输速度之后,那我们传输线的时延自然也就知道了哈。时延计算可用如下关系式表示:

其中,TD表示信号在传输线上的时延,Len表示传输线的长度,v表示信号的传输速度。

通过上面的信息,相信大家对信号的传输都有了一定的了解了,下面我们利用Sigrity当中的Sigrity Topology Explorer套件来进行仿真验证,跟大家一起进一步加深对传输线时延的了解。

微带线与带状线

创建的微带线与带状线简易传输链路模型如下图所示:

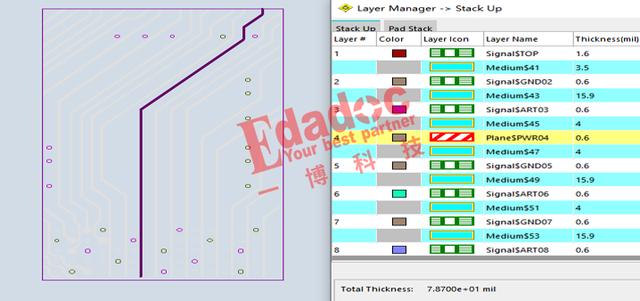

对微带线与带状线仿真参数进行设置,这里为了便于对比分析,将介质DK设为4,传输线线长设为1inch。

微带线参数设置:

带状线参数设置:

在设置完参数信息后,还可以查看生成的传输线信息,相信细心的朋友已经发现了,在生成的传输线信息中就包含了传输线单位长度的时延信息,那这里我们是不是可以验证一下软件的时延是不是与我们前面的公式计算相吻合呢?为了计算方便,这里我们以带状线为例,由上图可知带状线的时延为6671.28ps/m,换算后约169.45 ps/inch,公式计算结果169.49ps/inch,结果非常接近。完成模型及参数设置后得到的仿真结果如下图所示:

在上图微带线和带状线的仿真结果对比可以发现,两者到达接收器的时间相差了约12.5ps,可知微带线传输速度比带状线的传输速度要快,那是什么原因导致的呢?相信大家已经有了答案了。

根据前面传输速度公式可知介电常数是决定信号传输速度的主要因素,介质的介电常数越大,信号的传输速度越慢,反之则越快。微带线的一面有参考层一面没有参考层,在没有参考一面是绿油和空气,其中空气的介电常数接近似为1,导致微带线的周围环境整体的有效介电常数低于4,使得微带线的传输速度比带状线的传输速度更快。

前面已经对比过软件得出的时延与我们公式计算的时延结果相吻合,那这里也可以从生成传输线单位长度的时延信息去与我们的仿真结果做一个验证,看看两者的结果是否同样吻合。

从上面生成传输线单位长度的时延信息中我们知道了微带线的单位长度时延是6168.09ps/m,带状线的单位长度时延是6671.28ps/m,换算后微带线的单位长度时延是156.67 ps/inch,带状线的单位长度时延是169.45ps/inch,两者相差12.78ps,与仿真结果的12.5ps相吻合。

上述,我们通过理论和仿真的验证分析,知道了在线长相等的情况下微带线和带状线会存在时延差异以及导致差异的原因,那在布线设计中,对于一些速率较高,时序要求严格的信号,如DDR的数据信号,建议采用同组同层进行布线的原因之一正是如此。

审核编辑:汤梓红

-

电路板

+关注

关注

140文章

5344浏览量

108992 -

DDR

+关注

关注

11文章

761浏览量

69551 -

仿真

+关注

关注

55文章

4535浏览量

138659 -

PCB

+关注

关注

1文章

2352浏览量

13204

发布评论请先 登录

到底DDR走线能不能参考电源层啊?

PCB板双面布局的DDR表底走线居然不一样

信号在PCB走线中关于串扰 , 奇偶模式的传输时延

ADS PCB功能使用技巧系列之 - 如何走蛇形线?

PCB信号仿真之为什么DDR走线要同组同层?

关于DDR3信号扇出和走线问题解析

PCB绕等长之“同组同层”资料下载

PCB信号仿真之为什么DDR走线要同组同层?

PCB信号仿真之为什么DDR走线要同组同层?

评论