雷达作为20世纪人类在电子工程领域的一项重大发明,发展至今,其军事和民用用途非常广泛,而且范围几乎每天都在扩大。无论是用于导航、控制空中交通、跟踪天气模式、执行搜救任务、绘制地形图,还是无数其他功能,雷达技术都在不断进步。基于射频(RF)系统工作原理,雷达的能力取决于在保持信号强度的同时进行长距离感知和通信的能力。强大的射频信号能力扩展了关键任务的通信和态势感知,但加强射频输出的微电子技术,特别是高功率密度晶体管必须克服热限制,才能以更可靠和显著的高容量运行。

当前,射频系统的运行效能远低于电子容量的极限,仅仅是因为受到作为射频放大器基本构件的晶体管变得太热的限制。为此,美国防高级研究计划局(DARPA)在11月24日宣布推出“器件级电子散热技术”(THREADS),针对晶体管层面的热管理挑战,寻求利用新的材料和方法来扩散降低器件性能和任务寿命的热量。THREADS项目旨在克服一般内部电路操作固有的热限制,特别是关键的功率放大功能。

根据DARPA同期发布的广泛机构公告,THREADS项目的核心是在不降低器件性能或不增加晶体管所占面积的情况下,减少内部散热所涉及的热阻,这对提高雷达能力至关重要。为此,THREADS在克服热限制方面的工作可以帮助实现强大的、高功率密度的晶体管,这些晶体管在其基本电子极限附近工作,在放大射频输出功率方面达到新的水平。

据DARPA微系统技术办公室(MTO)负责THREADS的项目经理托马斯·卡齐尔(Thomas Kazior)介绍:“宽禁带晶体管,如氮化镓(GaN),是专门为提高功率放大器的输出密度而开发的。与上一代晶体管技术相比,GaN确实有超过5倍(性能指标)的改进。我们还知道,GaN的功率输出有可能进一步提高一个数量级,但由于废热过高,在当前无法实现持续运行。如果我们能够做好散热问题,我们就可以提高放大器的功率,增加雷达的威力范围。如果该项目成功,我们将把雷达的探测范围提高2到3倍。”

一、项目背景

雷达和通信系统在军事和商业应用中都是无处不在的。这些系统的性能取决于接收器上可实现的信噪比(S/N),它与发射器的射频输出功率成正比。在国防部(DoD)平台上,射频孔径的大小往往是有限的,因此,改善系统性能(如增加雷达或通信系统的范围)的唯一实用方法是增加发射器功率放大器(PA)的射频输出功率。后者与功率放大器晶体管的输出功率密度(即晶体管输出功率除以晶体管外围宽度)直接成正比。

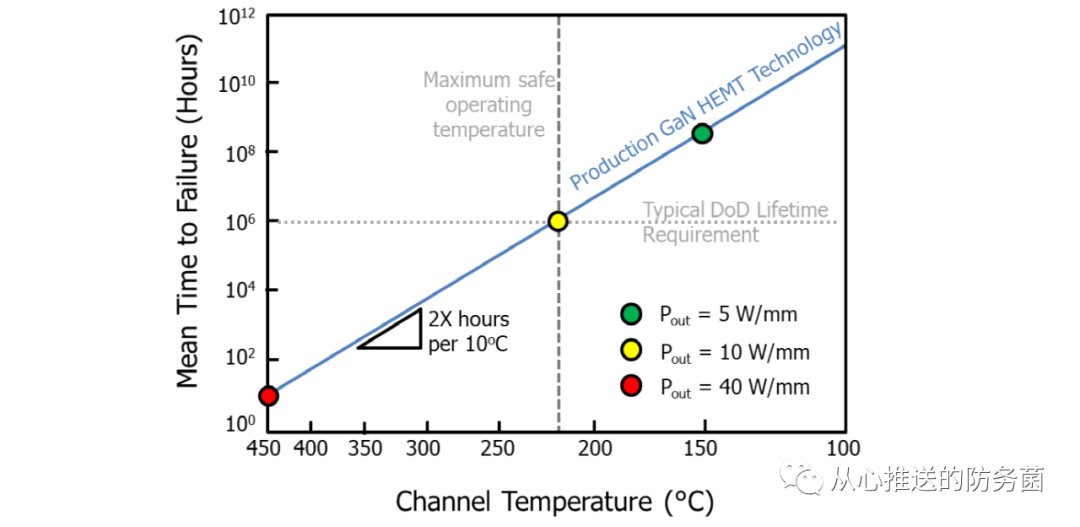

当前,在国防部射频发射器中实现的工作输出功率密度受到热限制,大大低于理论上的电子限制值。宽禁带(WBG)晶体管,如氮化镓(GaN),是专门为提高功率放大器的输出功率密度而开发的。事实上,与上一代晶体管技术砷化镓(GaAs)相比,GaN的射频功率输出(Pout)提高了5倍。但是,虽然众所周知GaN有可能进一步提高Pout的数量级,但由于晶体管通道层的废热过高,这在当前的持续运行中无法实现。由于GaN晶体管的直流-射频(DC-to-RF)转换效率低于1(例如,在X波段为60%),因此产生的废热导致通道温度升高(见图1),并导致晶体管的性能和寿命迅速下降(通道温度每升高10℃,器件寿命就减少一半)。如图1所示,GaN安全运行的最高通道温度为225℃。

图1. GaN晶体管技术的寿命限制

虽然GaN晶体管已被验证可以在脉冲模式下以高功率(Pout=40 W/mm)运行,但在PA中以实际波形(长脉宽、约30%的占空比)运行这些器件将导致不可接受的高通道温度(>450℃,相当于晶体管寿命减少五个数量级)。要实现接近GaN基本电子极限的晶体管输出功率,同时将通道温度保持在标称的最高温度(225℃)以下,需要大幅降低晶体管的热阻(以改善通道的散热),同时保持WBG半导体的优异电子特性。

通过投资先前的项目,如“动态范围增强电子和材料”(DREaM),DARPA已经成功地提高了晶体管的功率密度,并催生了业界对热耗散的更大关注。另一方面,“近结点热传输”(NJTT)和“片内/片间增强冷却”(ICECool)项目通过采用高导热基板(如钻石上的GaN)以及微流体冷却背板提供器件级冷却,以便在高功率密度下缓和通道温度。虽然很有希望,但NJTT仅仅使功率密度增加了3倍,而且没有改善GaN晶体管外延层堆叠的热阻,也没有改善与金刚石衬底之间的界面。

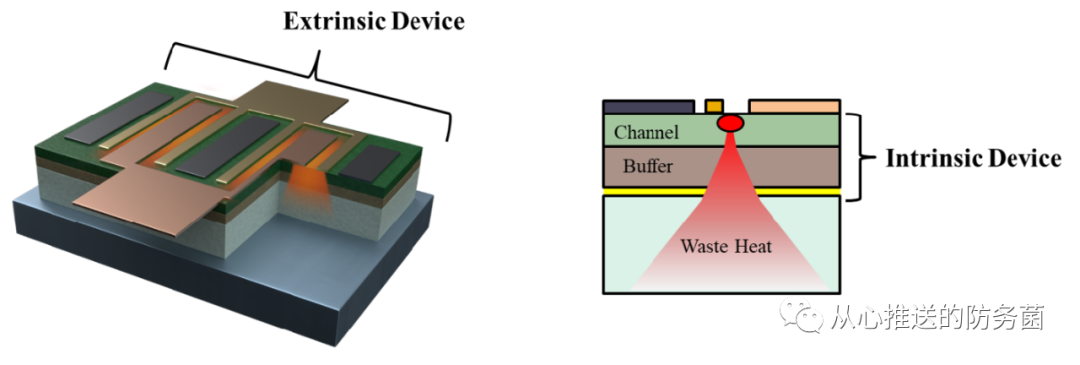

相比之下,THREADS将侧重于通过减少晶体管的热阻来实现高功率密度,包括内在设备内部和外部,如图2所示。在这个例子中,本征器件由外延层堆栈和单独的栅极指组成,而外征(即本征外部)器件由多指晶体管组成,包括栅极、漏极和源极指、垫子和总线。外在器件包括内在器件旁边的热扩散层或结构。器件的综合热阻被建模为内在(内部)和外在(外部)热阻的平行组合。

图2:(左)外部和(右)内部器件区域的示意布局和横截面。栅指上的红色区域表示产生废热的区域。

特别是,THREAD将解决以下两个关键技术挑战(TC)。

TC 1:减少器件内的热阻,同时保持良好的通道电流传输特性。

目前,晶体管外延层设计被优化以实现良好的通道电流传输特性(例如,GaN HEMT电子迁移率>1500 cm2/V-s),因为这是PA中高Pout和高效率的一个关键要求。最先进的(SoA)方法通过专注于减少通道缺陷密度的外延层设计来实现这种迁移率。特别是,GaN晶体管生长在SiC或其他异质衬底上,需要成核层和通道与衬底之间的厚缓冲层,以实现高电子迁移率。但是这些层本质上增加了热阻,这在很大程度上是由于层间的热边界电阻(TBR)抑制了不同材料间的热流。例如,GaN缓冲器和SiC衬底之间的大TBR已被证明可使通道峰值温度增加100℃以上。因此,一个典型的SOA硅基GaN晶体管的热阻比衬底的SiC衬底高3倍。

TC 2:在不降低射频性能的情况下,更有效地将热量从高功率晶体管上迁移开。散热是指将晶体管产生的废气从晶体管通道的“热点”处传导出去的方法。通常使用两种方法。

1.在多指晶体管单元中增加栅极间距,将废热扩散到更大的区域,减少热阻和热点温度。将栅极间距从20微米增加到60微米,可将热阻减少2倍,从20°C-mm/W减少到10°C-mm/W,但功率密度会相应降低。

2.热通孔提供了一条平行的路径,将废热从通道传播到背面的散热器,减少了20%的热阻,尽管由于热通孔不在晶体管热点附近而降低了热传导效率。

这两种方法都需要增加多指晶体管的占地面积,从而增加寄生电阻和电容,导致晶体管增益和效率下降。因此,有必要采取在不降低射频性能的情况下增加热扩散的方法。

二、项目描述

THREADS项目旨在开发克服晶体管热限制的技术,并实现强大的高功率密度器件,在其基本电子极限的无线电频率(RF)输出功率附近运行。具体来说,THREADS计划将验证:

-高效率、X波段(8-12GHz)晶体管和PA测试工具,其输出级晶体管的输出功率密度为81W/mm。

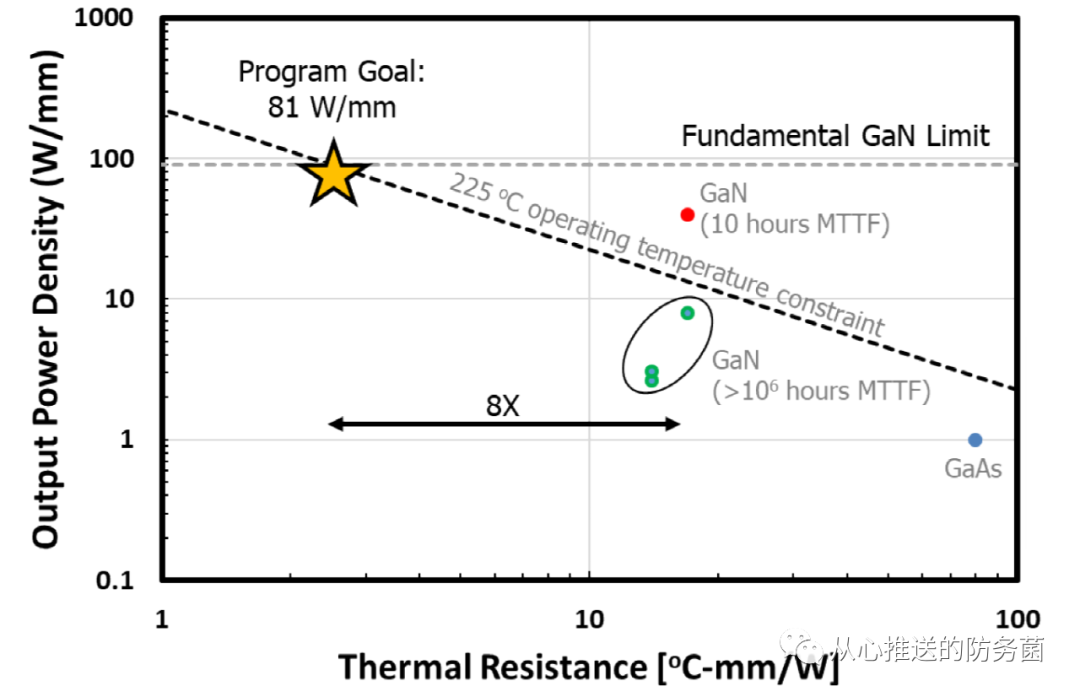

-晶体管热阻减少8倍(见下图3);

-可靠的操作,在225°C的通道温度下,预测的平均故障时间(MTTF)为106小时(与当前在约5 W/mm输出功率密度下操作的生产型GaN相当)。

如图3所示,SoA器件的热阻限制了宽禁带晶体管以高功率密度运行的能力。

图3. THREADS输出功率密度和热阻目标与典型的GaN和GaAs晶体管相比

DARPA最近在WBG和超宽带隙(UWBG)半导体材料、热界面工程和先进的三维热扩散方面取得了重大的进展。THREADS项目试图将这些最新的见解应用于现实的亚微米晶体管几何形状,以减少晶体管的热阻,并使其在高功率密度下工作,同时保持225°C的最大通道温度。通过结合材料热阻的改进、新的晶体管拓扑结构和热扩散层/结构,THREADS项目将验证晶体管热阻净减少8倍。

TC 1:在保持良好的通道电流传输特性的同时,降低器件内部的热阻。

THREADS旨在减少内在器件(外延层堆叠)的界面和薄膜热阻。方法可能包括但不限于:

-新型成核和缓冲层生长过程,以减少基材-外延层(如GaN-SiC)界面的缺陷密度,并能使用薄缓冲层;

-声子桥(例如,在异质界面的受控缺陷整合;异质界面的纳米结构技术;弹道热注入;应变增强的热边界传导);

-在外延生长过程中通过使用特定的同位素(如氮-15与氮-14)进行声子工程;

-梯度通道GaN HEMT,使电子在通道中均匀分布,以减少散射,降低电子温度,并提高饱和速度;

-数字化的AlN/GaN合金,以增加通道禁带,同时减少合金散射、通道/缓冲器热阻和界面散射,降低热边界电阻;

-结合降低界面热阻的方法,替代高导热基底(如金刚石,10 AlN)。

-替代的高导热缓冲层(如AlN);

-同源外延生长(如AlN/AlN)。

TC 2:在不降低射频性能的情况下,更有效地将热量从大功率晶体管上迁移开。

THREADS试图开发出分散废热和减少晶体管热阻的方法,以保持通道温度在225℃。方法可能包括但不限于:

-具有高导热性(如金刚石、AlN、c-BN)和低热边界电阻且不降低射频性能的顶部和/或嵌入式二维和三维冷却结构;

-新颖的栅极布局和多指晶体管拓扑结构,如分段栅极或环形HEMT,均匀、非均匀和蜂窝状的几何结构,结合三维热传导几何结构和异质材料集成,有效地传播热量,降低热点峰值温度。

DARPA预计THREADS提案可能会结合各种方法来解决TC1和TC2,从而使晶体管的热阻总体减少8倍。例如,表层和热界面的内在热阻的3倍改善(TC1)将需要额外减少由于设备热改进(TC2)而产生的外在热阻的5倍(即3倍减少与5倍减少并行)。改变表层堆栈中的材料,使内在热阻有更大的减少(如4倍),只需要使用设备改进,额外减少较小的(如4倍)外热阻。提出的材料和器件的方法和理由由提案人决定,但必须达到或超过每个阶段的晶体管热阻降低目标。

由于电和热性能之间的潜在权衡,提案者应结合电热协同设计、建模和模拟来指导器件优化。

除了减少晶体管热阻的方法外,还可以提出减少高功率密度晶体管散热量的方法(例如,通过提高晶体管效率,同时保持与基线器件相同的晶体管工作模式/类别,如AB类),只要提供明确的计算/模拟,表明提出的任何额外指标/目标与本BAA公布的指标/目标一致。然而,诸如外部封装解决方案(如微流控/喷射撞击冷却、倒装芯片等)和不成熟的半导体技术,如全钻石晶体管,不符合本BAA的目标。此外,DARPA鼓励提案者开发可能适用于未来材料系统(如超宽带半导体)的热管理方法。最后,虽然THREADS晶体管和功率放大器测试工具的指标设定在X波段频率,但所提供的热解决方案应适用于广泛的频率范围。DARPA鼓励提案者讨论他们的技术方法在多大程度上适用于在X波段以外的频率工作的晶体管和功率放大器。

三、项目技术领域

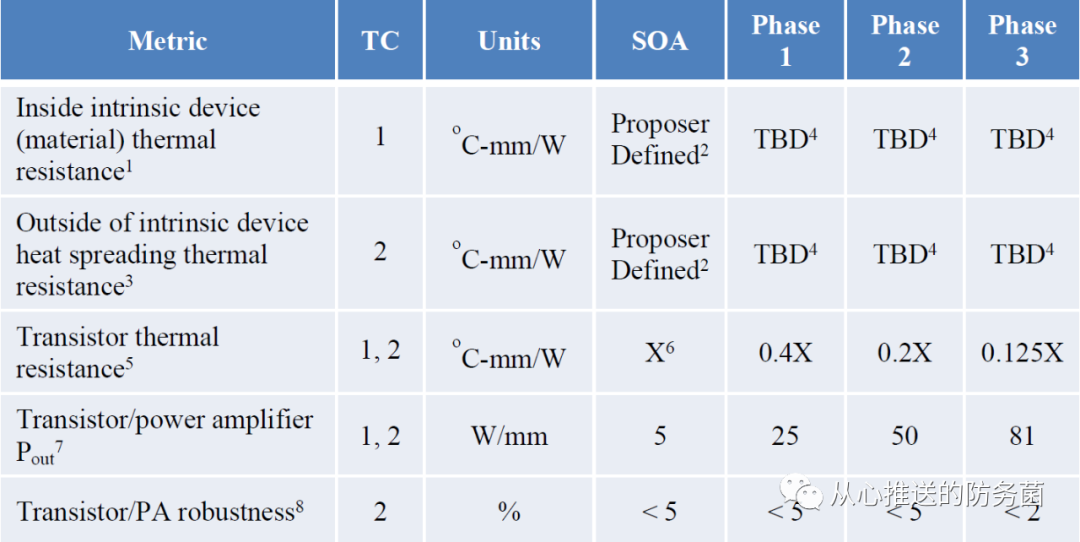

THREADS项目有一个技术领域(TA),将重点解决两个主要的技术挑战。研究团队必须在其提案中解决这两个技术挑战,说明如何同时满足所有的指标。性能指标在下方表1中规定。请注意,表1包括所需的提案者定义的内在设备热阻内部和外部的指标。

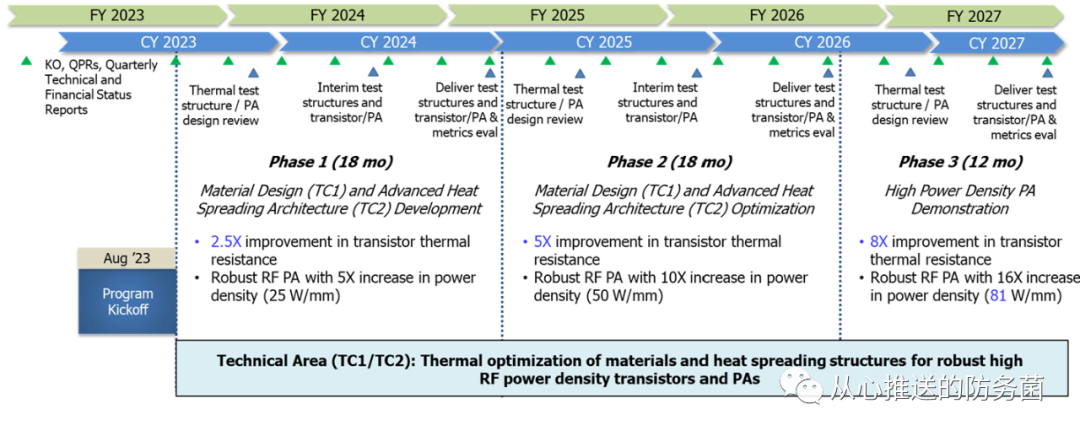

-第一阶段(18个月)的目标是在固有器件材料结构内(TC1)和固有器件热扩散结构外(TC2)进行开发,将晶体管热阻降低2.5倍,并演示验证一个可靠、高效的射频功率密度为25W/mm的功率放大器。

-第二阶段(18个月)的目标是在本征器件材料结构(TC1)内和本征器件热扩散结构(TC2)外进行优化,将晶体管热阻降低5倍,并演示验证一个可靠、高效的功率密度为50W/mm的功率放大器。

-第三阶段(12个月)的目标是扩大第二阶段的成果,演示验证强大的射频晶体管和功率放大器,热阻减少8倍,射频输出功率密度增加16倍(达到81瓦/毫米)。

DARPA希望将一个独立的、由政府资助的验证和确认(IV&V)团队纳入该项目。为了确保特征分析的一致性,研究团队应与该IV&V团队协调,并开发适当的热测试结构、多指晶体管单元和SEC。此外,研究团队还需要与IV&V团队合作,确定相关的热学和电学计量技术,以表征这些测试结构和设备。热计量技术可能包括拉曼光谱、栅极电阻测温、瞬时热反射、稳态热反射(SSTR)、时域热反射(TDTR)或频域热反射(FDTR)。表1的脚注7提供了一个多指晶体管单元和SEC设计和测量最低要求的例子。晶体管的稳健性将使用在多个SEC上测量的1000小时射频压力测试进行评估(表1的脚注8)。投标者应在其提案中提供详细信息,说明他们计划如何在本项目下开发和鉴定热测试结构、多指晶体管单元和SEC。

表1:THREADS项目指标

1.在提案者定义的材料热电阻率测试结构上进行测量,并采用提案者定义的测量方法【例如,时域热反射(TDTR),微拉曼光谱】。测试结构和测量方法应与政府的IV&V团队协调。热阻是指从通道层到衬底的测量,包括通道层、缓冲层、衬底和接口的热阻。通道迁移率>1000 cm2/V-s。

2.提案者根据其对成熟基线GaN器件定义的器件内部热阻指标。并要求达到THREADS晶体管热阻指标。

3.在提案者定义的内在器件热阻外测试结构上进行测量,并采用提案者定义的测量方法。测试结构和测量方法应与政府的IV&V团队协调。

4.根据提案者的方法,由提案者定义的内在设备热阻指标之外,需要实现THREADS晶体管热阻指标。

5.使用提案者定义的晶体管热阻测试结构和提案者定义的测量方法对多指晶体管进行测量。测试结构和测量方法应与政府IV&V团队协调。热阻测量从通道热点到衬底,包括内在器件(材料/epi堆栈)的热阻(TC1)和内在器件外部的热扩散热阻(TC2)。

6.提案者根据其对成熟基线GaN器件技术定义热阻值。

7.在多指晶体管单元和标准评估电路(SEC,如单级MMIC功率放大器测试工具)上测量的功率密度;最小总栅极周边=600米(如6×100米),最大栅极间距为50米;峰值PAE时的Pout密度;10GHz时PAE>60%,带宽20%;占空比30%;峰值通道温度:225°C;在至少20个晶体管单元和SEC上测量的平均功率密度跨越至少2块晶元。

8. 在SEC上测量了1000小时CW射频压力测试后Id、Pout的变化;SEC的Pout=25、50、81W/mm(分别为第1、2、3阶段)和10GHz下的最大PAE,带宽为20%,通道峰值温度:225°C;在至少2个晶圆上的至少20个SEC上测量的稳健性。

四、项目架构、时间表与里程碑

THREADS是一个为期48个月的三阶段项目,第一阶段18个月(基础),第二阶段18个月(可选),第三阶段12个月(可选),有一个技术领域。在第1阶段和第2阶段结束时,根据技术进展和资金供应情况,政府可自行决定行使期权。预计随着选择权的行使,研究团队的数量可能会减少,从而进入该项目的第二和第三阶段。

THREADS项目的架构如图4所示。THREADS预计在2023年8月开始。项目的启动和季度审查会议或技术交流会议是强制性的,是与政府就项目中的工作、技术方法的细节以及任何技术或计划中的关注项目进行交流的机会。

图4:THREADS项目架构

研究团队将构建一个研究计划,以达到或超过指标表中所列的所有指标。该计划应包括:

-项目启动会议,在弗吉尼亚州阿灵顿的项目开始时亲自举行;

-项目季度审查,可通过电话会议或由DARPA决定在研究团队所在地进行;

-通过电话会议对电气和热测试结构以及功率放大器(PA)测试工具/标准评估电路(SECs)进行设计审查,包括电气和热测试计划;

-在中期和末期交付适当的电气和热测试结构和功率放大器/标准评估电路,供政府独立验证和确认。

审核编辑:郭婷

-

晶体管

+关注

关注

77文章

9682浏览量

138079 -

雷达

+关注

关注

50文章

2930浏览量

117465 -

射频放大器

+关注

关注

3文章

321浏览量

18900

原文标题:【THREADS】DARPA通过“器件级电子散热技术”提升雷达能力

文章出处:【微信号:CloudBrain-TT,微信公众号:云脑智库】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DARPA微系统技术将雷达探测范围提高2到3倍

DARPA微系统技术将雷达探测范围提高2到3倍

评论