在过采样ADC中,一个很有效的提高SNR的方法为增大采样速率以提高过采样率。在其他器件都不改变的前提下,这样做需要积分器和运放具有更高的带宽,从而导致更高的功耗。

采用双采样技术,可以实现如下效果:

在保持原来OSR的基础上,可将时钟频率缩小为原来的一半,对运放建立要求的时间因此变为原来的两倍, 运放功耗因此降低 ;

在保持运放和采样频率不变的前提下, 有效采样频率变为原来的两倍, OSR翻倍 , 实现更好的噪声整形效果。

双采样积分器原理简介

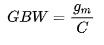

常用的运放增益带宽积GBW可以表示为式(1):

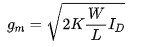

gm和电流的关系可以表示为 式(2):

对普通的开关电容积分器,假如运放输入对管的宽长比保持不变,提高一倍采样时钟频率需要将GBW翻倍,因此需要将工作电流提高为原来的四倍。

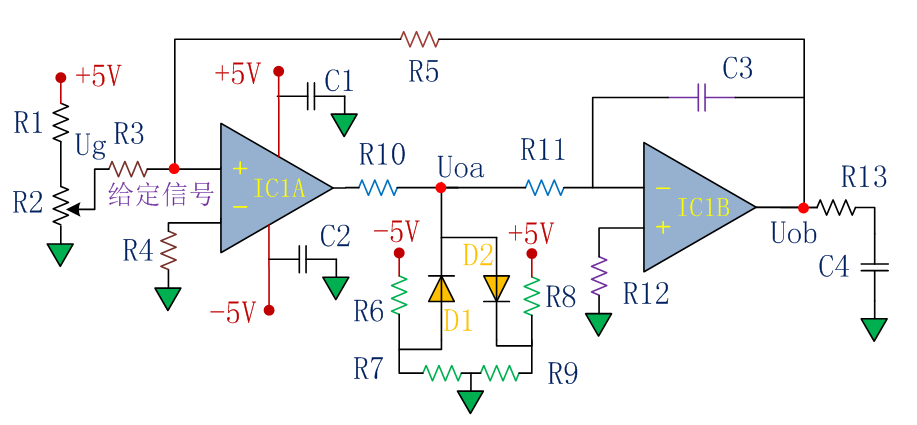

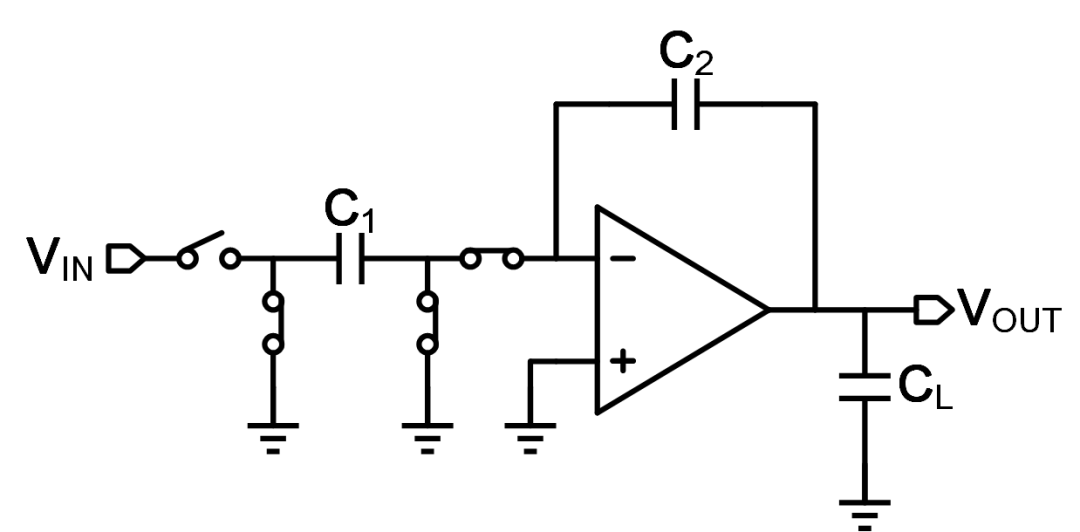

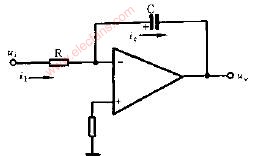

然而,对普通的开关电容积分器而言,当时钟处在输入采样相时,运放处于空闲状态。如果采用两个采样电容工作在交错的时钟下,便可以将运放更高效地使用,同时输入信号采样频率也加倍。这就是双采样的基本思想。

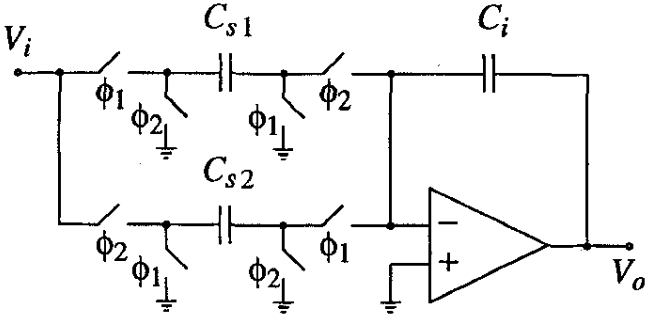

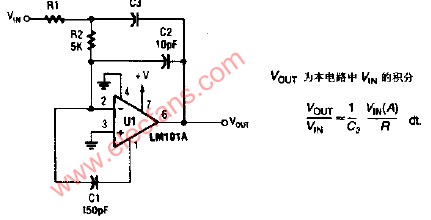

图1 双采样积分器单端实现

图1给出了双采样积分器的单端实现方式。在该电路中,通过两个不同的电容对输入信号采样,电容CS1在Φ1相采样,在Φ2相进行积分;电容CS2在Φ2相采样,在Φ1相进行积分,因此,在时钟的两个相位都同时存在采样和积分,有效采样频率因此变为原来的二倍。

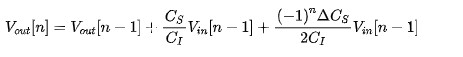

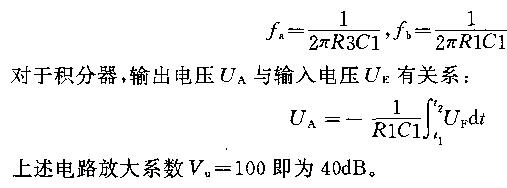

不考虑其他非理想因素,双采样积分器的传递函数可以表示为式(3):

其中:

n=0出现在Φ2为高时,同时需要注意的是:n代表第n个有效采样周期,而不是采样时钟周期!双采样使得每个采样时钟周期内有两个有效采样周期。

式(3)左边两项为一个理想的延迟积分器,但最后一项为输入信号与(-1)n之积,这表征的是频率为采样频率一半(fs/2,也就是时钟频率fc)的余弦信号被采样后,与输入信号调制得到的信号,该信号由两个采样电容之间的失配造成。

对输入信号采样而言,由于输入信号频率很低,上述调制信号不会出现在信号带内,因此不会影响输入信号。

然而,对调制器的反馈DAC而言,由于DAC的输出包含高频量化噪声,因此失配导致上述的信号调制现象会将量化噪声折回带内,因而恶化调制器的SNR。该现象为双采样Sigma-Delta调制器的主要缺点!

解决该问题目前常用的几个办法包含积分器电路结构设计抵消失配产生的额外电荷转移;NTF在fs/2处放置零点;DAC采用单电容实现等,感兴趣的读者可以查阅相关文献。

总结

本文简单地介绍了双采样技术的出发点与基本原理,并介绍了其目前存在的主要缺点。希望读者多多指正。

-

adc

+关注

关注

98文章

6495浏览量

544466 -

运放

+关注

关注

47文章

1163浏览量

53062 -

SNR

+关注

关注

3文章

195浏览量

24405 -

积分器

+关注

关注

4文章

100浏览量

28444

发布评论请先 登录

相关推荐

积分器:Integrator

罗氏线圈为什么要用积分器?

双采样积分器原理简介

双采样积分器原理简介

评论