1. TrustZone介绍

1.1 安全背景

在介绍 TrustZone 前有必要简单回顾下目前的一些安全手段。

CPU 通过内存映射手段给每个进程营造一个单独的地址空间来隔离多个进程的代码和数据,通过内核空间和用户空间不同的特权级来隔离操作系统和用户进程的代码和数据。但由于内存中的代码和数据都是明文,容易被同处于内存中的其它应用偷窥,因此出现了扩展的安全模块,应用将加密数据送往安全模块,由安全模块处理完后再返回结果给相应的应用。

很多消费电子设备都使用扩展的安全模块来确保数据安全,目前常见的方式有:

外部挂接硬件安全模块

数据的处理交由外部的安全模块实现,这些模块能够保护自己的资源和密钥等数据的安全,如 SIM 卡、各种智能卡或连接到外部的硬件加解密模块等,但其同主芯片的通信线路暴露在外部,容易被监听破解。另外,通信的速率比较低。

内部集成硬件安全模块

将外部安全模块的功能集成到芯片内,因此一个芯片上至少有两个核:一个普通核和一个安全核。优点是核与核之间的通信在芯片内部实现,不再暴露在外面。缺点是核之间的通信速度仍然较低,而且单独的安全核性能有限,还会会占用 SoC 面积,成本较高。

1.2 TrustZone 是个什么鬼?

TrustZone 是 ARM 针对消费电子设备设计的一种硬件架构,其目的是为消费电子产品构建一个安全框架来抵御各种可能的攻击。

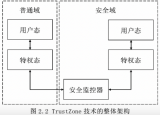

TrustZone 在概念上将 SoC 的硬件和软件资源划分为安全(Secure World)和非安全(Normal World)两个世界。

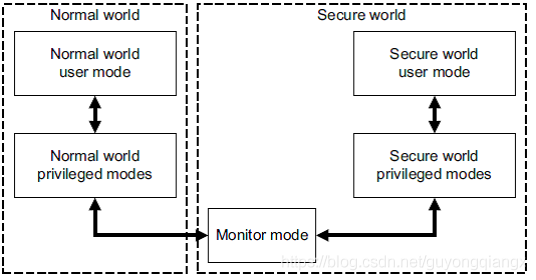

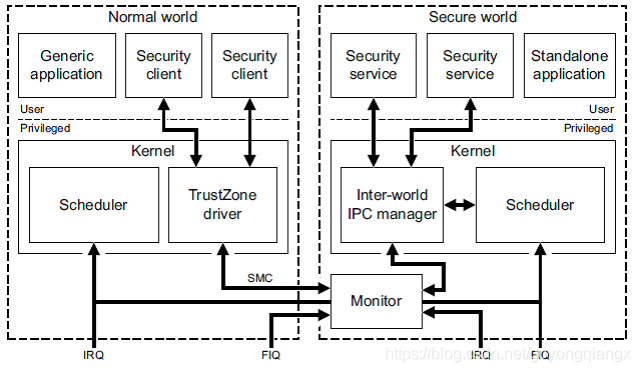

所有需要保密的操作在安全世界执行(如指纹识别、密码处理、数据加解密、安全认证等),其余操作在非安全世界执行(如用户操作系统、各种应用程序等),安全世界和非安全世界通过一个名为 Monitor Mode 的模式进行转换,如图1:

图1. ARM的安全世界和非安全世界

处理器架构上,TrustZone 将每个物理核虚拟为两个核,一个非安全核(Non-secure Core, NS Core),运行非安全世界的代码;和另一个安全核(Secure Core),运行安全世界的代码。

两个虚拟的核以基于时间片的方式运行,根据需要实时占用物理核,并通过 Monitor Mode 在安全世界和非安全世界之间切换,类似同一CPU下的多应用程序环境,不同的是多应用程序环境下操作系统实现的是进程间切换,而 Trustzone 下的 Monitor Mode 实现了同一 CPU 上两个操作系统间的切换。

AMBA3 AXI(AMBA3Advanced eXtensible Interface)系统总线作为 TrustZone 的基础架构设施,提供了安全世界和非安全世界的隔离机制,确保非安全核只能访问非安全世界的系统资源,而安全核能访问所有资源,因此安全世界的资源不会被非安全世界(或普通世界)所访问。

设计上,TrustZone 并不是采用一刀切的方式让每个芯片厂家都使用同样的实现。总体上以 AMBA3 AXI 总线为基础,针对不同的应用场景设计了各种安全组件,芯片厂商根据具体的安全需求,选择不同的安全组件来构建他们的 TrustZone 实现。

其中主要的组件有:

必选组件

AMBA3 AXI总线,安全机制的基础设施

虚拟化的ARM Core,虚拟安全和非安全核

TZPC (TrustZone Protection Controller),根据需要控制外设的安全特性

TZASC (TrustZone Address Space Controller),对内存进行安全和非安全区域划分和保护

可选组件

TZMA (TrustZone Memory Adapter),片上ROM或RAM安全区域和非安全区域的划分和保护

AXI-to-APB bridge,桥接 APB 总线,配合 TZPC 使 APB 总线外设支持 TrustZone 安全特性

除了以上列出的组件外,还有诸如 Level 2 Cache Controller, DMA Controller, Generic Interrupt Controller等。

逻辑上,安全世界中,安全系统的OS提供统一的服务,针对不同的安全需求加载不同的安全应用 TA(Trusted Application)。例如:针对某具体 DRM 的 TA,针对 DTCP-IP 的 TA,针对 HDCP 2.0验证的 TA 等。

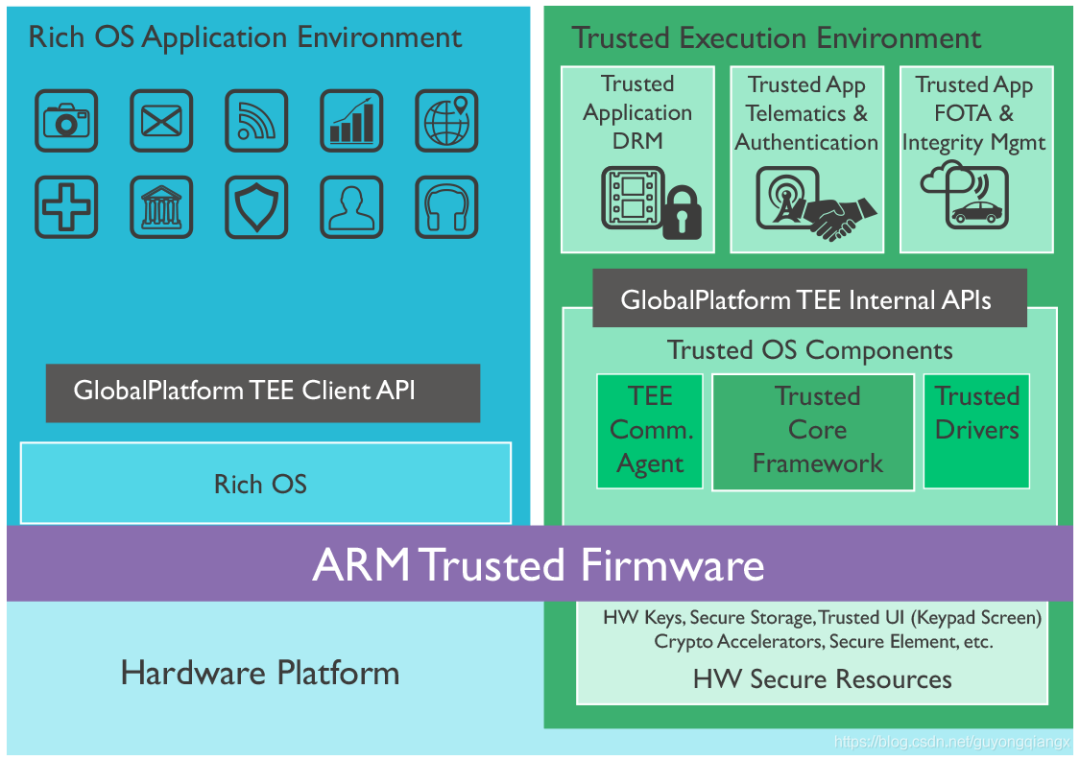

图2是一个 ARM 官网对 TrustZone 介绍的应用示意图:

基于TrustZone的应用

图2. 基于 TrustZone 的应用示意图

图中左边蓝色部分 Rich OS Application Environment(REE)表示用户操作环境,可以运行各种应用,例如电视或手机的用户操作系统,图中右边绿色部分 Trusted Execution Envrionment(TEE)表示系统的安全环境,运行 Trusted OS,在此基础上执行可信任应用,包括身份验证、授权管理、DRM认证等,这部分隐藏在用户界面背后,独立于用户操作环境,为用户操作环境提供安全服务。

可信执行环境(TEE, Trusted Execution Environment) 是 Global Platform(GP)提出的概念。对应于 TEE 还有一个 REE(Rich Execution Environment)概念,分别对应于安全世界(Secure World)和非安全世界(Non-secure World, Normal World)。

GlobalPlatform(GP) 是跨行业的国际标准组织,致力于开发、制定并发布安全芯片的技术标准,以促进多应用产业环境的管理 及其安全、可互操作的业务部署。目标是创建一个标准化的基础架构, 加快安全应用程序及其关联资源的部署,如数据和密钥,同时保护安全应用程序及其关联资源免受软件方面的攻击。

2. TrustZone 原理和设计

以下主要从 TrustZone 的总线设计,CPU 设计(包括处理器模型、内存模型和中断模型)和安全隔离机制来介绍 TrustZone 的设计和工作原理。

2.1 总线设计

总线

设计上,TrustZone 在系统总线上针对每一个信道的读写增加了一个额外的控制信号位,这个控制位叫做 Non-Secure 或者 NS 位,是 AMBA3 AXI 总线针对 TrustZone 作出的最重要、最核心的扩展设计。

这个控制信号针对读和写分别叫做 ARPORT[1] 和 AWPORT[1]:

ARPROT[1]: 用于读操作(Read transaction), 低表示 Secure, 高表示 Non-Secure

AWPROT[1]: 用于写操作(Write transaction), 低表示 Secure,高表示 Non-Secure

总线上的所有主设备(master)在发起新的操作(transaction)时会设置这些信号,总线或从设备(slave)上解析模块会对主设备发起的信号进行辨识,来确保主设备发起的操作在安全上没有违规。

例如:硬件设计上,所有非安全世界的主设备(Non-Secure masters)在操作时必须将信号的NS位置高,而NS位置高又使得其无法访问总线上安全世界的从设备(Secure Slaves),简单来说就是对非安全世界主设备发出的地址信号进行解码时在安全世界中找不到对应的从设备,从而导致操作失败。

NS控制信号在 AMBA3 AXI 总线规范中定义。可以将其看作为原有地址的扩展位,如果原有32位寻址,增加NS可以看成是33位寻址,其中一半的32位物理寻址位于安全世界,另一半32位物理寻址位于非安全世界。

当然,非安全世界的主设备尝试访问安全世界的从设备会引发访问错误,可能是 SLVERR(slave error)或者 DECERR(decode error),具体的错误依赖于其访问外设的设计或系统总线的配置。

外设

在 TrustZone 出现前,ARM 的外设基于 AMBA2 APB (Advanced Peripheral Bus)总线协议,但是 APB 总线上不存在类似 AXI 总线上的 NS 控制位。

为了兼容已经存在的 APB 总线设计,AMBA3 规范中包含了 AXI-to-APB bridge 组件,这样就确保基于 AMBA2 APB 的外设同 AMBA3 AXI的系统兼容。AXI-to-APB bridge 负责管理 APB 总线设备的安全事宜,其会拒绝不合理的安全请求,保证这些请求不会被转发到相应的外设。

例如:新一代的芯片可以通过增加 AXI-to-APB bridge 组件来沿用上一代芯片的设计来使其外围设备可以支持 TrustZone。

2.2 处理器设计

2.2.1 处理器模型

TrustZone 中,每个物理处理器核被虚拟为一个安全核(Secure)和一个非安全核(Non-Secure),安全核运行安全世界的代码,非安全核运行除安全世界外的其它代码。

由于安全世界和非安全世界的代码采用时间片机制轮流运行在同一个物理核上,相应的节省了一个物理处理器核。

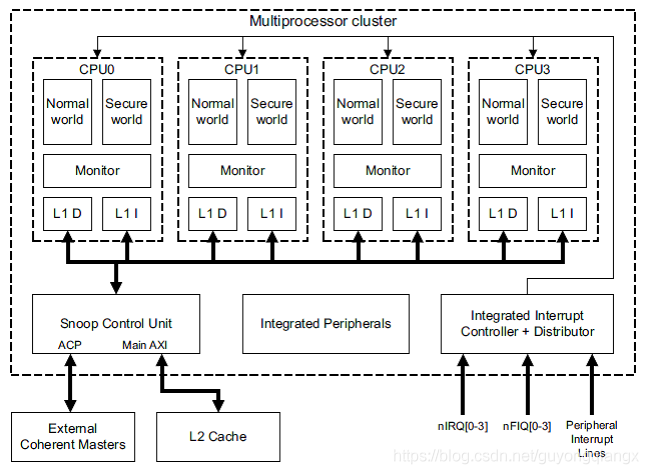

多核处理器上,也有建议说让将某一个或几个核指定为安全专用核,只运行安全系统代码来构建安全世界,其余核运行非安全代码,暂不清楚目前有哪些平台采用这个实现。

图3中,系统有4个物理核,每个又分为两个虚拟核(安全核和非安全核)的情况:

图3. 多核处理器上的安全核和非安全核

2.2.2 L1内存模型

MMU

MMU 是一种硬件电路,它包含两类部件,一类是分段部件,一类是分页部件,对应于内存管理的分段机制和分页机制。分段机制把一个逻辑地址转换为线性地址;接着,分页机制把一个线性地址转换为物理地址。

当 CPU 访问一个虚拟地址时,这个虚地址被送到MMU翻译,硬件首先把它和TLB中的所有条目同时(并行地)进行比较,如果它的虚页号在 TLB 中,并且访问没有违反保护位,它的页面会直接从 TLB 中取出而不去访问页表,从而提高地址转换的效率。

安全世界和非安全世界都有自己的虚拟 MMU,各自管理物理地址的映射。实际上只是两个世界都有一份 TTBR0、TTBR1、TTBCR 寄存器,因此就会对应两个MMU表。

尽管 MMU 有两套,但 TBL 缓存硬件上只有一套,因此 TBL 对于两个世界来说是共享的,其通过NS位来标志其每一项具体属于哪一个世界。这样在两个世界间进行切换时不再需要重新刷新 TLB,提高执行效率。

对于 TLB 共享并不是硬性规定的,部分芯片在两个世界间切换时可能通过硬件部分或全部刷新 TLB。

Cache

同 TLB 类似,硬件上两个世界共享一套 Cache,具体的 Cache 数据属于哪一个世界也由其 NS 位指定,在世界间切换也不需要刷新 Cache。

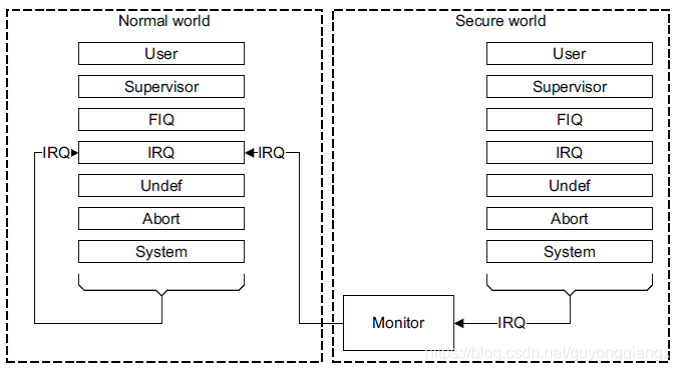

2.2.3 中断模型

基于 TrustZone 的处理器有三套异常向量表:

一套用于非安全世界

一套用于安全世界

还有一套用于 Monitor 模式

与之前非 TrustZone 的处理器不同的是,这三套中断向量表的基地址在运行时可以通过 CP15 的寄存器 VBAR(Vector Base Address Register)进行修改。

复位时,安全世界的中断向量表由处理器的输入信号 VINITHI 决定,没有设置时为 0x00000000,有设置时为 0xFFFF0000;非安全世界和 Monitor 模式的中断向量表默认没有设置,需要通过软件设置后才能使用。

默认情况下,IRQ 和 FIQ 异常发生后系统直接进入 Monitor 模式,由于 IRQ 是绝大多数环境下最常见的中断源,因此 ARM 建议配置 IRQ 作为非安全世界的中断源,FIQ 作为安全世界的中断源。这样配置有两个优点:

当处理器运行在非安全世界时,IRQ 直接进入非安全世界的处理函数;如果处理器运行在安全世界,当 IRQ 发生时,会先进入到 Monitor 模式,然后跳到非安全世界的 IRQ 处理函数执行

仅将 FIQ 配置为安全世界的中断源,而 IRQ 保持不变,现有代码仅需做少量修改就可以满足

将 IRQ 设置为非安全世界的中断源时系统 IRQ 的切换见图4:

图4. IRQ作为非安全世界的中断源

2.2.4 系统模式切换

基于 TrustZone 的系统有三种状态,安全世界、非安全世界和用于二者切换的 Monitor Mode。

协处理器 CP15 的寄存器 SCR(Secure Configuration Register)有一个 NS 位用于指示当前处理器位于哪一个世界,该寄存器在非安全世界是不能访问的。

当 CPU 处于 Monitor Mode 时,无论 NS 位是 0 还是 1,处理器都是在安全世界运行代码。

因此 Monitor Mode 下总是安全世界,但如果此时 NS 为 1,访问 CP15 的其它寄存器获取到的是其在非安全世界的值。

非安全世界到Monitor模式的切换

处理器从非安全世界进入 Monitor Mode 的操作由系统严格控制,而且所有这些操作在 Monitor Mode 看来都属于异常。从非安全世界到 Monitor Mode 的操作可通过以下方式触发:

软件执行 SMC (Secure Monitor Call)指令

硬件异常机制的一个子集(换而言之,并非所有硬件异常都可以触发进入 Monitor Mode),包括:

IRQ

FIQ

external Data Abort

external Prefetch Abort

Monitor Mode

Monitor Mode 内执行的代码依赖于具体的实现,其功能类似于进程切换,不同的是这里是不同模式间 CPU 状态切换。

软件在 Monitor Mode 下先保存当前世界的状态,然后恢复下一个世界的状态。操作完成后以从异常返回的方式开始运行下一个世界的代码。

为什么安全模式和非安全模式不能直接切换?

非安全世界无权访问 CP15 的 SCR 寄存器,所以无法通过设置NS来直接切换到安全世界,只能先转换到 Monitor Mode,再到安全世界。

如果软件运行在安全世界(非Monitor Mode)下,通过将 CP15 的 NS 位设置 1,安全世界可以直接跳转到非安全世界,由于此时 CPU 的流水线和寄存器还遗留了安全世界的数据和设置,非安全模式下的应用可以获取到这些数据,会有极大的安全风险。因此,只建议在 Monitor Mode 下通过设置 NS 位来切换到非安全模式。

综上,安全世界和非安全世界不存在直接的切换,所有切换操作都通过 Monitor Mode 来执行。

图5展现了安全世界和非安全世界之间的切换方式:

图5. 安全世界和非安全世界之间的切换

2.3 隔离机制

除了 CPU 执行时实行安全世界和非安全世界的隔离外,AMBA3 AXI 总线提供了外设隔离的基础。

2.3.1 内存隔离机制

这里的内存指外部的 DDR 和片上的 ROM 以及 SRAM,其隔离和保护通过总线组件 TZASC 和 TZMA 的设置来实现。

TZASC (TrustZone Address Space Controller)

TZASC 可以把外部 DDR 分成多个区域,每个区域可以单独配置为安全或非安全区域,非安全世界的代码和应用只能访问非安全区域。TZASC 只能用于内存设备,不适合用于配置块设备,如 Nand Flash。

TZMA (TrustZone Memory Adapter)

TZMA 可以把片上 ROM 和 SRAM 隔离出安全和非安全区域。TZMA 最大可以将片上存储的低 2MB 配置为安全区域,其余部分配置为非安全区域。大小划分上,片上安全区域可以在芯片出厂前设置为固定大小,或运行时通过 TZPC 动态配置。TZMA 使用上有些限制,其不适用于外部内存划分,而且也只能配置一个安全区域。

2.3.2 外设隔离机制

外设上,基于 APB 总线的设备不支持 AXI 总线的 NS 控制信号,所以 AXI 到 APB 总线需要 AXI-to-APB bridge 设备连接,除此之外,还需要TZPC (TrustZone Protection Controller) 来向 APB 总线上的设备提供类似 AXI 上的 NS 控制信号。

由于 TZPC 可以在运行时动态设置,这就决定了外设的安全特性是动态变化的,例如键盘平时可以作为非安全的输入设备,在输入密码时可以配置为安全设备,只允许安全世界访问。

2.3.3 隔离机制示意图

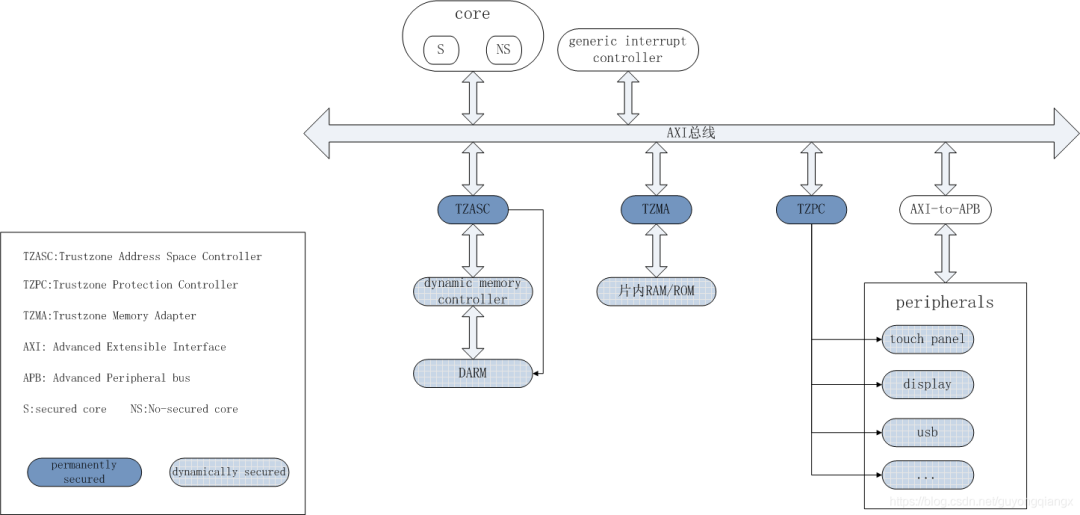

整个系统内存和外设隔离机制示意图见图6.

图6. 系统内存和外设隔离机制示意图

此图来源于网上,实际上 TZPC 还连接到片内的 ROM/RAM 设备上,用于配置片上存储的安全区域。

2.4 安全启动

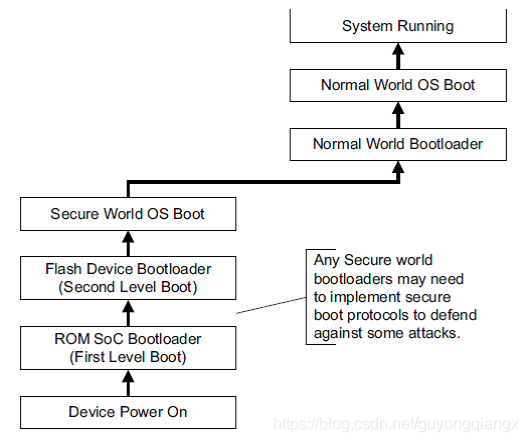

AMBA3 AXI 总线机制隔离出安全世界和非安全世界,但这是系统启动之后的事情。如何确保系统本身是安全的呢?这就涉及到系统启动的过程。

系统上电复位后,先从安全世界开始执行。安全世界会对非安全世界的 bootloader 进行验证,确保非安全世界执行的代码经过授权而没有被篡改过。然后非安全世界的 bootloader 会加载非安全世界的 OS,完成整个系统的启动。

在非安全系统的 bootloader 加载 OS 时,仍然需要安全世界对 OS 的代码进行验证,确保没有被篡改。

图7是典型的 TrustZone 芯片的启动流程:

图7. 典型的 TruestZone 芯片启动流程

整个启动流程跟目前博通平台的安全启动原理基本一致,上电后安全芯片先启动,然后校验主芯片的 bootloader,接下来 bootloader 提交系统的 OS 和文件系统给 BSP 进行校验,通过后加载主系统,确保主系统是安全的。

从上电复位开始的整个启动过程中,下一级的安全基于上一级的验证,最终依赖于芯片内置的 OTP 和安全硬件,逐级的验证构成了整个系统的信任链。信任链中的某一个环节被破坏,都会导致整个系统不安全。

3. 各家 TrustZone 实现

基于安全考虑,各家 TrustZone 都实行闭源,关于其实现细节的介绍都较少。

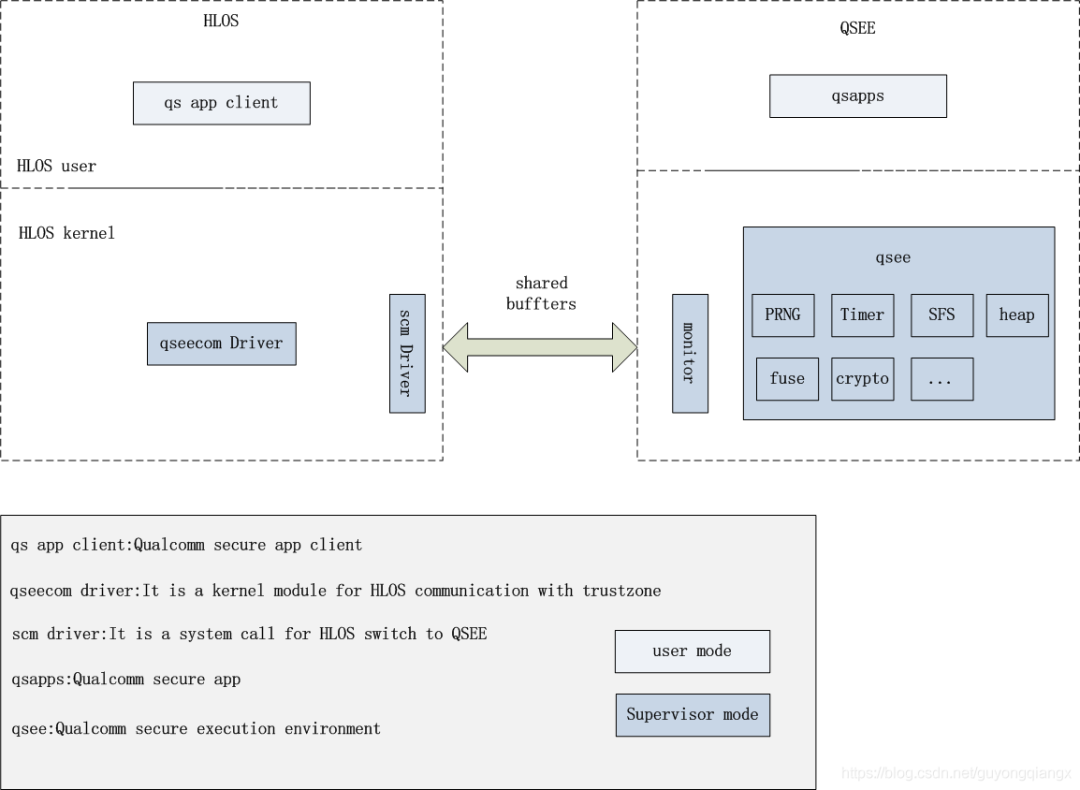

网上能找到少许关于高通方案上 TrustZone 的介绍:

安全世界 QSEE (Qualcomm Secure Execution Environment)

非安全世界 HLOS (High Level OS)

整个系统的架构如图8:

图8. 高通QSEE系统架构图

4. 其它

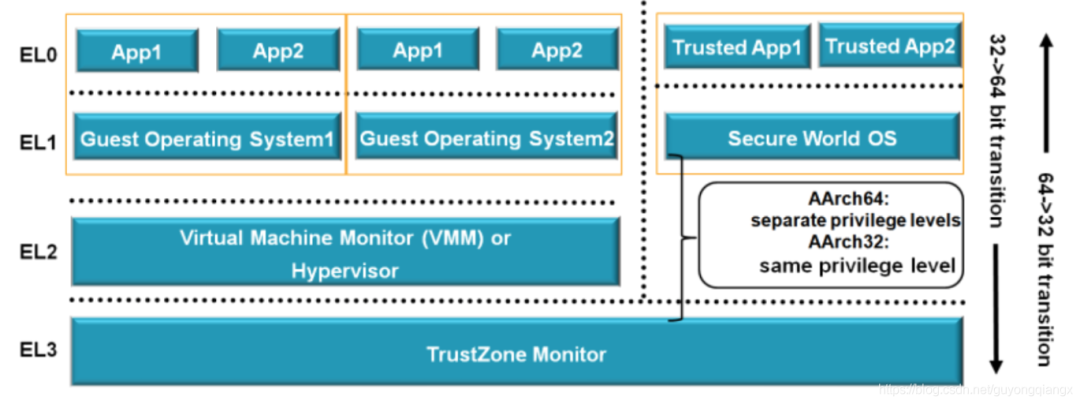

ARMv8-A 架构定义了四个异常等级,分别为 EL0到 EL3,其中数字越大代表特权(privilege)越大:

EL0: 无特权模式(unprivileged)

EL1: 操作系统内核模式(OS kernel mode)

EL2: 虚拟机监视器模式(Hypervisor mode)

EL3: TrustZone monitor mode

TrustZone 设计的相关方

ARM 公司,定义 TrustZone 并实现硬件设计,TEE,TZAPI等

芯片厂家,在具体芯片上实现 TrustZone 设计,包括三星、高通、MTK、TI、ST、华为等

应用提供方,如 DRM 厂家和安全应用开发商,实现 DRM、Playready、DTCP-IP 和一些其它安全应用开发和认证

Trust OS

TEE 环境下也要有一个操作系统,各家都有自己的 Trustzone 的操作系统。如 Trustonic、高通的 QSEE、国内的豆荚,还有开源的 OPTEE 和 Trusty 等。

在操作系统之上自然要有应用程序,在 Trustzone 里面我们一般叫 TrustApp,当然 TEE 里面每个 TrustApp 都在一个沙盒里,互相之间是隔离的。

比如说支付,就可以做成一个 App(需要注意的是,和 Normal Worl d里面的 App 是两个概念),这个 App 简单来说就负责用私钥把网上发来的 Challenge 签个名,而这个签名的动作是需要在 Secure World 里面做的,避免恶意程序窃取到私钥来伪造签名。

例如支付宝,其实支付宝也是只支持几个 Trust OS 的。同时,支付宝还定义了一系列标准,用来完成他的行为。

现在的 Trust OS 大都会遵循 GlobalPlatform 的规范,这个组织致力于制定统一的 Trust OS 的 API 的接口规范,这样一个 TrustApp 只要用 GP API,就可以方便移植到各个不同的 TEE 操作系统上了。

Intel 平台的 SGX

针对可信计算,类似 ARM 的 TrustZone,Intel 也针对 x86 平台提出了自己的安全架构 SGX:

Intel Software Guard Extensions (Intel SGX)

https://software.intel.com/zh-cn/sgx-sdk

SGX 全称 Intel Software Guard Extensions,顾名思义,其是对因特尔体系(IA)的一个扩展,用于增强软件的安全性。

这种方式并不是识别和隔离平台上的所有恶意软件,而是将合法软件的安全操作封装在一个 enclave 中,保护其不受恶意软件的攻击,特权或者非特权的软件都无法访问 enclave。

也就是说,一旦软件和数据位于 enclave 中,即便操作系统或者和 VMM(Hypervisor)也无法影响 enclave 里面的代码和数据。

Enclave 的安全边界只包含 CPU 和它自身。SGX 创建的 enclave 也可以理解为一个可信执行环境 TEE。不过其与 ARM TrustZone(TZ)还是有一点小区别的,TZ 中通过 CPU 划分为两个隔离环境(安全世界和正常世界),两者之间通过 SMC 指令通信;而 SGX 中一个 CPU 可以运行多个安全 enclaves,并发执行亦可。

简单来讲, Intel SGX 最关键的优势在于将程序以外的 software stack如 OS 和 BIOS 都排除在了 TCB(Trusted Computing Base)以外。换句话说,就是在容器 enclave 里的 code 只信任自己和 Intel 的 CPU。

网上有人是这样对比 TrustZone 和 SGX 的:

Trustzone 默认相信 SecureOS,安全世界。SGX 仅相信 CPU core,通过 SGX 指令构建 enclave容器。简单比喻,TEE 是个公用大保险柜,什么东西都装进去,有漏洞的 app 可能也进去了,而且保险柜钥匙在管理员手上,必须相信管理员。SGX 每个 app 有自己的保险柜,钥匙在自己手上

SGX 要进入工业界应用尚需时间,一个重要的问题是现在在 Intel 发行的服务器芯片上还没有 SGX,而 SGX 的重要应用就是在数据中心和云端的应用。

审核编辑:刘清

-

SIM卡

+关注

关注

6文章

293浏览量

30862 -

SoC芯片

+关注

关注

2文章

678浏览量

37313 -

trustzone

+关注

关注

0文章

23浏览量

13145

原文标题:一篇了解TrustZone

文章出处:【微信号:LinuxDev,微信公众号:Linux阅码场】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

embOS如何支持Arm TrustZone

TrustZone结构化消息是什么?

介绍Cortex-A和Cortex-M的TrustZone之间的差异

Arm架构中的TrustZone、CryptoCell以及Cryptoisland之间的区别是什么

了解体系结构-适用于AArch64的TrustZone介绍

ARM 架构中TrustZone 安全处理技术的研究

基于LPC55xxx CM33核的TrustZone原理与应用

RA6快速设计指南 [8] 使用TrustZone®

![RA6快速设计指南 [8] 使用<b class='flag-5'>TrustZone</b>®](https://file1.elecfans.com/web2/M00/8C/52/wKgZomSqLKiALgWMAAADbu4X9Ec624.gif)

Arm® TrustZone® 技术简介

如何实现TrustZone的可信执行环境来支持隐私计算呢?

什么是TrustZone?TrustZone是如何实现安全隔离的

什么是TrustZone?TrustZone是如何实现安全隔离的

评论