什么是当今吸引人们注意的流行先进技术?相信以下的专业用词都经常出现在周遭与新闻、文章之中,如人工智能(Artificial Intelligence)、深度学习(Deep Learning)、云端计算(Cloud Computing)、超级计算机(Supercomputer)、自动驾驶、智能语音识别等。

包括Google、Amazon、Intel、Nvidia或是AMD等,从这些世界级技术巨型企业的策略中可以发现,不约而同的都正积极投下巨额资金,来开发前述的这些软硬件技术和相关的应用。

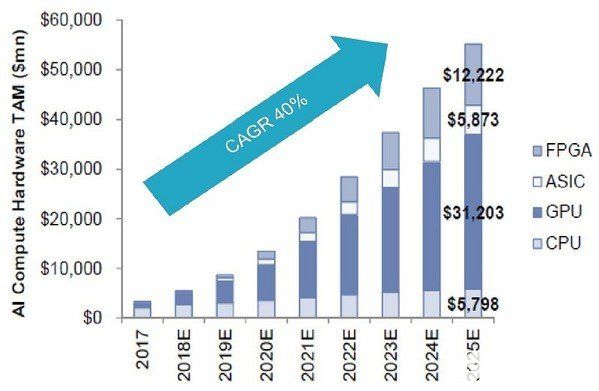

据九芯电子研究显示,组成人工智能机能应用所需要的硬件,例如特殊应用语音识别IC(Speech recognition IC)、绘图处理芯片(GPU)、中央处理器(CPU)、场域可程序化门阵列(FPGA)等组件,在未来数年间的全球市场规模,将会以40%年平均成长率急速扩大。

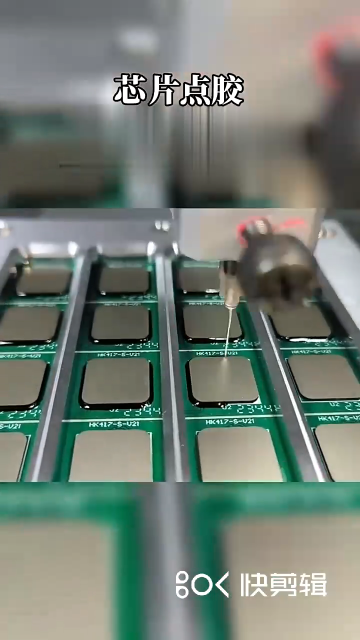

语音芯片封装高度整合的关键:异质整合技术

由于算法、大数据和高效能语音识别芯片的进步,是扮演推动这一新世代科技浪潮的大动力。因此随着终端电子产品快速发展,智慧家居、平板计算机与穿戴装置等产品不断朝轻薄短小、多功能、高效能、低成本、低功耗,及小面积等要求发展的情况下,需将把多种不同功能的ic芯片整合于单一语音模块中。因此,包括晶圆代工厂、IC设计公司等语音IC制造厂家,相继投入先进封装技术领域。根据Yole数据显示,2017~2021年全球先进封装规模从250亿美元增至310亿美元,年复合成长率约7%。

而这些先进技术的应用与能力,都在近几年内取得了令人惊讶的巨大进展,然而在这些看似不同领域技术或科学的背后,都有一个共同的特点,那就是都采用了异质整合(Heterogeneous Integration)的语音IC设计。

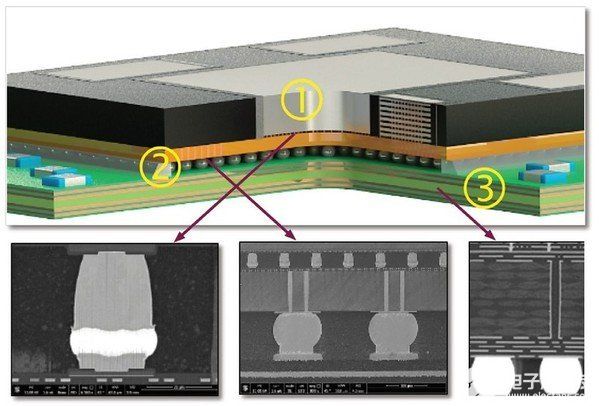

例如,近来出现了另一种称为「chiplet(小芯片)」的设计概念。所谓chiplet,就是具备特殊用途或单一功能的KGD(known good die)或IP区块;然后,在开发高效能系统时,透过搭配选用适当chiplet的堆栈累积,来达成所需的系统效能。目前的封装技术是以并排的方式朝2.5D技术发展,透过中介层(interposer)和重分布层(RDL)设计来进行整合。而3D封装则是把多颗芯片向上堆栈,除了底层芯片之外,所有芯片都需要透过TSV (硅穿孔)来传递讯号。

英特尔(Intel)在CES 2019主题演讲中,发表了采用3D芯片封装技术的处理器(Lakefield),引起众人的注目,也让3D异整合质封装正式迈入商品化的程度。Intel利用堆栈设计,整合各式芯片、I/O、结构等,进而提升IC芯片设计的灵活性,也大幅减少多核处理器所需的芯片空间,让体积缩小到仅有12mm×12mm。

透过新世代的封装技术突破摩尔定律

根据2018年所发表的IRDS Roadmap(International Roadmap for Devices and Systems),到2030年IC芯片制程技术将达到1.5 nm。但是在半导体前段制程中,根据摩尔定律应该在5nm左右就难以再突破了,但是随着技术进步到28nm之后,成本反而会逐渐下降。这似乎违背了产业中的基础常识。

例如台积电(TSMC)不断地将组件的制程持续缩小,从14 nm、10 nm、7 nm甚至于目前新开发的3nm,不仅仅提升CMOS组件的运作速度,同时也大幅度增加了逻辑闸数。虽然目前3nm制程技术仍在早期研发阶段,台积电也没有发表例如效能及功耗指标等等任何技术细节(如,和5nm制程相较能提升多少效能),只描述3nm将会是一个全新的制程技术,所以必然也会有新的架构、技术、材料等。而不是5nm制程的提升。

这相当于每经过18-24个月的时间,可以在同一空间中,让组件数增加一倍,除了加快ic芯片本身的运作速度外,还有两个因素变得越来越重要。

一个是采用高带宽储存(HBM;High Bandwidth Memory)的架构,不仅可提高计算能力之外,还可以降低系统总功耗和增加储存的带宽;另一个则为了达到高速数据收发的串行化或解串行化(serializer/deserializer),也就是SerDes。SerDes IO的模块可以整合到主芯片中,也可以作为单独的芯片生产制造。

而要如何将这些高速性能进行整合?其中一个关键点,就是让先进的2.5D异质整合结构芯片封装技术来扮演这个角色。但是为什么需要采用2.5D封装技术,以目前来说,2.5D封装是一种高阶的IC芯片封装技术,可实现各种IC芯片的高速整合。

审核编辑:汤梓红

-

封装

+关注

关注

127文章

7990浏览量

143353 -

语音芯片

+关注

关注

12文章

1773浏览量

36723 -

九芯电子

+关注

关注

0文章

108浏览量

1686

发布评论请先 登录

相关推荐

Flash语音芯片相比OTP语音芯片的优势

芯片知识:如何将语音精确烧录至语音芯片

NVC系列-语音提示芯片在智能台灯上的应用案例

异质整合推动语音芯片封装前往新境界

异质整合推动语音芯片封装前往新境界

评论