现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以45度角走线,并且会说走圆弧会比45度拐角更好。事实是不是这样?PCB走线角度该怎样设置,是走45度好还是走圆弧好?90度直角走线到底行不行?这是我经常看见广大 PCB Layout 拉线菌热议的话题。

大家开始纠结于pcb走线的拐角角度,也就是近十几二十年的事情。上世纪九十年代初,PC界的霸主Intel主导定制了PCI总线技术,似乎从PCI接口开始,我们开始进入了一个“高速”系统设计的时代,20世纪90年代以后,正是有了一帮类似老wu这样的玩家对3D性能的渴望,使得相应的电子设计和芯片制造技术能够按照摩尔定律往前发展,由于IC制程的工艺不断提高,IC的晶体管开关速度也越来越快,各种总线的时钟频率也越来越快,信号完整性问题也在不断的引起大家的研究和重视。比如现在人们对4K高清家庭影音视频的需求,HDMI2.0传输标准速率已经达到了 18Gbps !!!

HP3456A几乎是故意走的直角(某些地方本来一个斜角走完,它偏要连续走几个直角),绝大多数地方没有铺铜。

右上角,拐直角不止,线宽还变小了?

直角、搭桥、铺铜,模拟就真的不能铺铜吗?

直角,45度斜线,任意角度斜线,方焊盘,圆焊盘。

高速信号线拐一下90°真的不行吗?这里来跟大家探讨一下关于高频/高速信号的走线拐角角度问题。我们从锐角到直角、钝角、圆弧一直到任意角度走线,看看各种走线拐角角度的优缺点。

PCB能不能以锐角走线

PCB能不能以锐角走线,答案是否定的,先不管以锐角走线会不会对高速信号传输线造成负面影响,单从PCB DFM方面,就应该避免出现锐角走线的情形。

因为在PCB导线相交形成锐角处,会造成一种叫酸角“acid traps”的问题,在pcb制板过程中,在pcb线路蚀刻环节,在“acid traps”处会造成pcb线路腐蚀过度,带来pcb线路虚断的问题。虽然,我们可以借助CAM 350 进行DFF Audit自动检测出“acid traps”潜在问题,避免在PCB在制造产生时产生加工瓶颈,如果PCB板厂工艺人员检测到有酸角(acid trap)存在,他们将简单地贴一块铜到这个缝隙中,很多板厂的工程人员他们其实并不懂layout的,他们只是从PCB工程加工的角度进行了修复酸角(acid trap)的问题,但这种修复会不会带来进一步的信号完整性问题便不得而知了,所以我们在layout是就应该从源头去尽量避免产生酸角(acid trap)。

怎样避免拉线时出现锐角,造成acid trap DFM 问题?现代的EDA设计软件(如Cadence Allegro、Altium Designer等)都带有了完善的Layout走线选项,我们在layout走线是,灵活运用这些辅助选项,可以极大的避免我们在layout时产生产生“acid trap”现象。

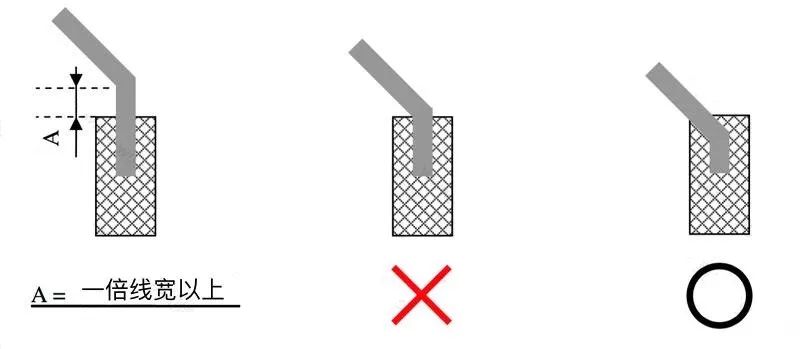

焊盘的出线角度设置 避免导线与焊盘形成锐角角度的夹角。

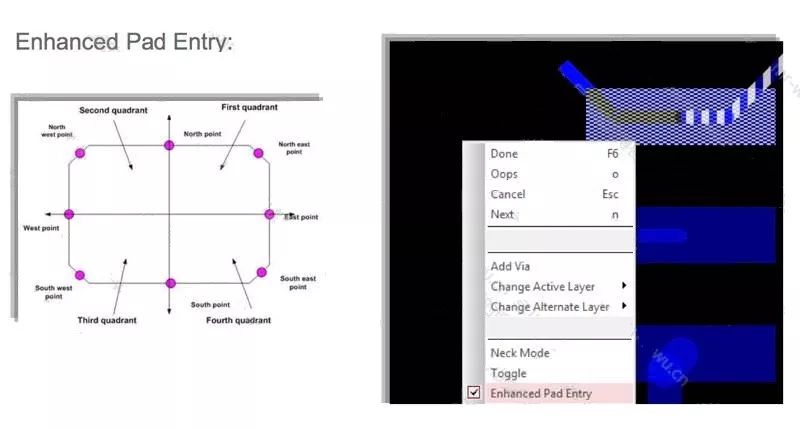

利用 Cadence Allegro 的 Enhanced Pad Entry 功能能够让我们在layout时尽可能的避免导线与焊盘在出线时形成夹角,避免造成“acid traps”DFM问题。

避免两条导线交叉形成锐角夹角。

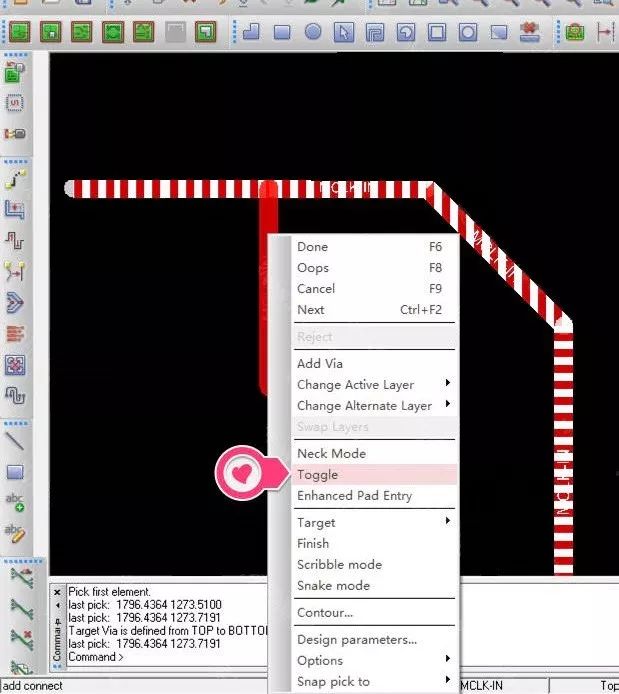

灵活应用 Cadence Allegro 布线时切换 ” toggle “ 选项,可以避免导线拉出T型分支时形成锐角夹角,避免造成“acid traps”DFM问题。

pcb layout能不能以90°走线

高频高速信号传输线应避免以90°的拐角走线,是各种PCB Design Guide中极力要求的,因为高频高速信号传输线需要保持特性阻抗一致,而采用90°拐角走线,在传输线拐角处,会改变线宽,90°拐角处线宽约为正常线宽的 1.414倍,由于线宽改变了,就会造成信号的反射,同时,拐角处的额外寄生电容也会对信号的传输造成时延影响。

当然,当信号沿着均匀互连线传播时,不会产生反射和传输信号的失真,如果均匀互连线上有一个90°拐角会,则会在拐角处造成pcb传输线宽的变化,根据相关电磁理论计算得出,这肯定会带来信号的反射影响。

理论上是这样,但理论终究是理论,实际情况90°拐角对高速信号传输线造成的影响是否是举足轻重的呢?

所以,90°拐角对高速信号传输线会有负面影响,理论上是一定的,但是这种影响是不是致命的?90°拐角对于高速数字信号和高频微波信号传输线的影响是不是一样的?

根据 这篇论文《right angle corners on printed circuit board traces,time and frequency domain analysis》和 Howard Johnson 的这篇文章《Who’s Afraid of the Big Bad Bend?》及 Eric Bogatin 的著作 《信号完整性与电源完整性分析(第二版) 》第八章的内容,我们可以得出以下结论:

对于高速数字信号来说,90°拐角对高速信号传输线会造成一定的影响,对于我们现在高密高速pcb来说,一般走线宽度为4-5mil,一个90°拐角的电容量大约为10fF,经测算,此电容引起的时延累加大约为0.25ps,所以,5mil线宽的导线上的90°拐角并不会对现在的高速数字信号(100-psec上升沿时间)造成很大影响。

而对于高频信号传输线来说,为了避免集肤效应(Skin effect)造成的信号损坏,通常会采用宽一点的信号传输线,例如50Ω阻抗,100mil线宽,这90°拐角处的线宽约为141mil,寄生电容造成的信号延时大约为25ps,此时,90°拐角将会造成非常严重的影响。同时,微波传输线总是希望能尽量降低信号的损耗,90°拐角处的阻抗不连续和而外的寄生电容会引起高频信号的相位和振幅误差、输入与输出的失配,以及可能存在的寄生耦合,进而导致电路性能的恶化,影响 PCB 电路信号的传输特性。

关于90°信号走线,尽量避免以90°走线,单个90°拐角对高速数字传输线所带来的信号质量影响,相对于导线与参考平面高度的偏差,导线自身蚀刻过程中线宽线距均匀性的变化偏差,板材介电常数对频率信号的变化,甚至过孔寄生参数所带来的影响都要比90°拐角所带来的问题大得多。但是如今的高速数字电路传输线总避免不了要绕等长的,十几二十个拐角叠加起来,这90°拐角所累计叠加起来的影响造成的信号上升延时将变得不可忽略。高速信号总是沿着阻抗最小的路径传输,以90°拐角绕等长,最终的实际信号传输路径会比原来的要略短一些。

而且现在的高速数字信号传输速率正在变得越来越高,目前的HDMI2.0标准,传输带宽速率已经达到了18Gbps,90°拐角走线将不再符合要求,而且现在都21世纪了,现在的EDA软件即便是那些免费使用的,对45°走线都已经支持的很好了。

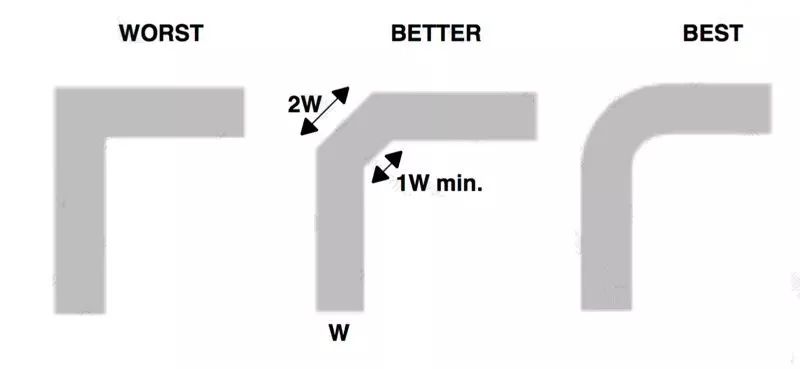

同时,以90°拐角走线,以工程美学来说,也不太符合人们的审美观。所以,对于现在的layout来说,不论你是不是走的高频/高速信号线,我们都要尽量避免以90°拐角进行走线,除非有特殊的要求。对于大电流走线,有时我们会以铺铜铜皮替换走线的方式布线,在铺铜的拐角处,也需要以两个45°拐角替换90°拐角,这样不仅美观,而且不会存在EMI隐患。

以45°走线

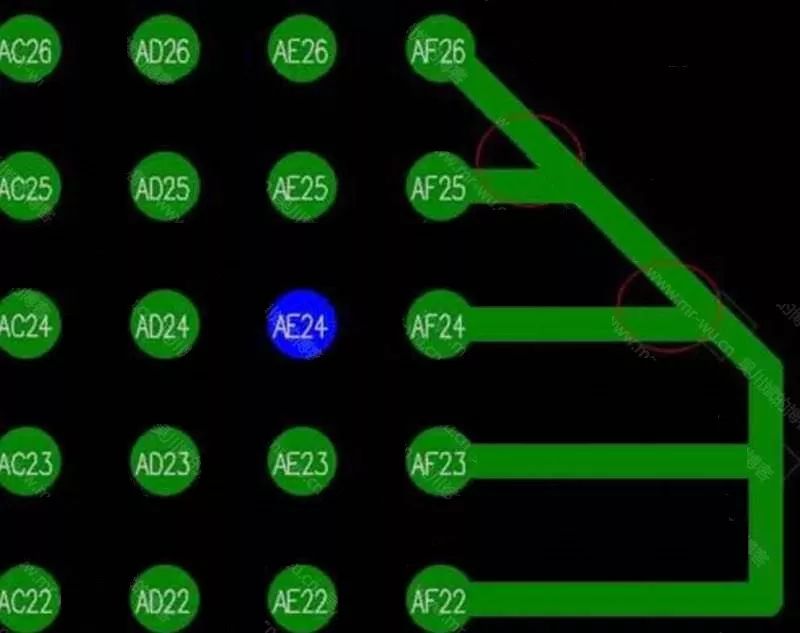

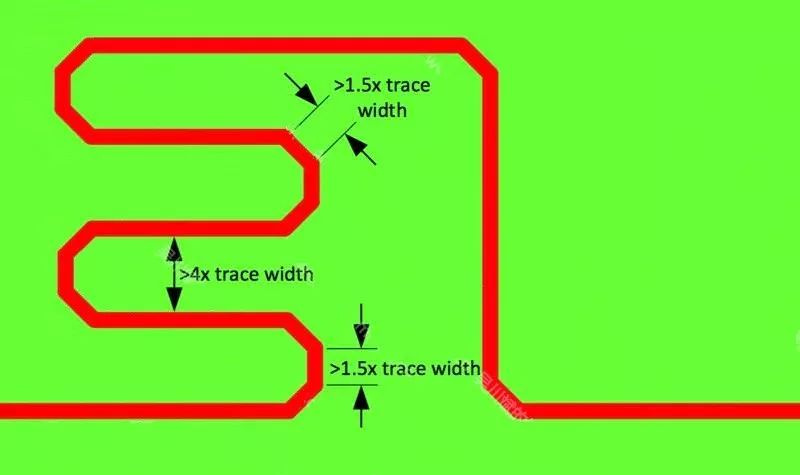

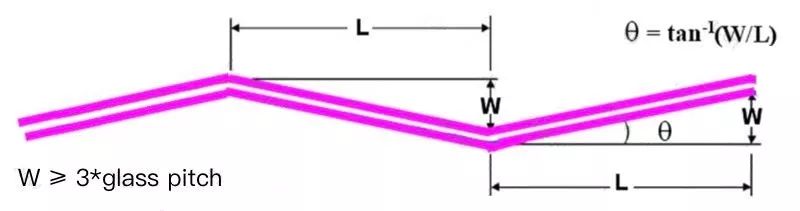

除了射频信号和其他有特殊要求的信号,我们PCB上的走线应该优选以45°走线。要注意一点的是,45°角走线绕等长时,拐角处的走线长度要至少为1.5倍线宽,绕等长的线与线之间的间距要至少4倍线宽的距离。由于高速信号线总是沿着阻抗最低的路径传输,如果绕等长的线间距太近,由于线间的寄生电容,高速信号走了捷径,就会出现等长不准的情况。现代的EDA软件的绕线规则都可以很方便的设置相关的绕线规则。

以arc弧形走线

如果不是技术规范明确要求要以弧形走线,或者是rf微波传输线,老wu个人觉得,没有必要去走弧形线,因为高速高密度pcb的layout,大量的弧形线后期修线非常麻烦,而且大量的弧形走线也比较费空间。

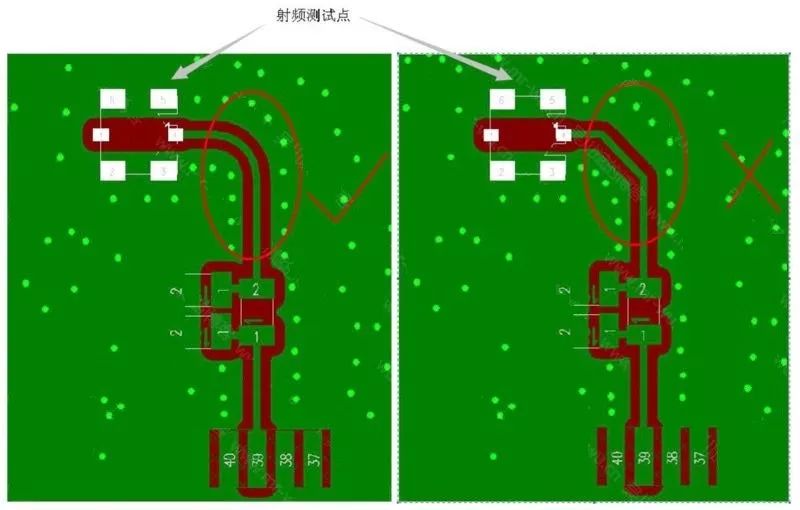

当然,对于RF微波信号传输线,还是优先走圆弧线,甚至是要走“采用 45° 外斜切”线走线。

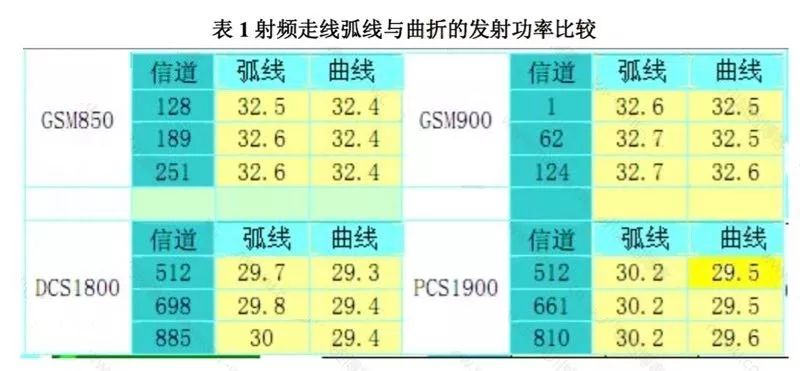

下图为射频信号传输线圆弧走线与45度角走线发射功率实测的对比结果,狮屎可以证明,高频信号圆弧走线的确由于45°角走线。

以任意角度走线

随着4G/5G无线通讯技术的发展和电子产品的不断升级换代,目前PCB数据接口传输速率已高达10Gbps或25Gbps以上,且信号传输速率还在不断的朝着高速化方向发展。随着信号传输的高速化、高频化发展,对PCB阻抗控制和信号完整性提出了更高的要求。对于PCB板上传输的数字信号来说,电子工业界应用的包括FR4在内的许多电介质材料,在低速低频传输时一直被认为是均匀的。但当系统总线上电子信号速率达到Gbps级别时,这种均匀性假设不再成立,此时交织在环氧树脂基材中的玻璃纤维束之间的间隙引起的介质层相对介电常数的局部变化将不可忽视,介电常数的局部扰动将使线路的时延和特征阻抗与空间相关,从而影响高速信号的传输。基于FR4测试基板的测试数据表明,由于微带线与玻纤束相对位置差异,导致测量所得的传输线有效介电常数波动较大,最大、最小值之差最大可以达到△εr=0.4。尽管这些空间扰动看上去较小,它会严重影响数据速度为5-10Gbps的差分传输线。

在一些高速设计项目中,为了应对玻纤效应对高速信号的影响,我们可以采用zig-zag routing布线技术以减缓玻纤效应的影响。

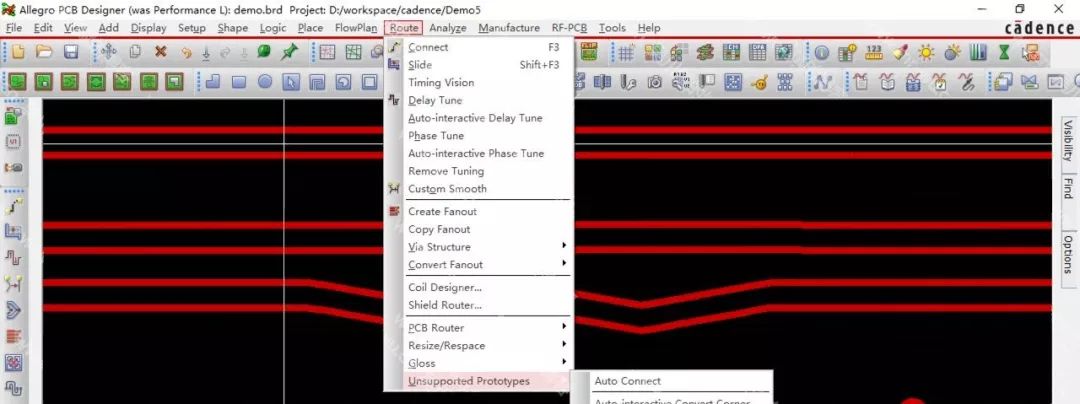

Cadence Allegro PCB Editor 16.6-2015 及后续版本带来了对zig-zag布线模式的支持。

在 Cadence Allegro PCB Editor 16.6-2015 菜单中选择”Route -> Unsupported Prototype -> Fiber Weave Effect” 打开zig-zag routing功能。

正如二十年前我们pcb layout不用关注是否要走弧形线,不用担心pcb板材玻璃纤维对高速信号的影响一样。

所以,不存在一成不变的pcb layout规则,随着pcb制造工艺的提升和数据传输速率的提高,有可能现在正确的规则在将来将变得不再适用。所以最为一枚合格的拉线菌,一定要与时俱进,掌握产业技术方向的发展,才能不被大浪淘沙所淘汰。

审核编辑:郭婷

-

pcb

+关注

关注

4319文章

23099浏览量

397916 -

soc

+关注

关注

38文章

4165浏览量

218272 -

eda

+关注

关注

71文章

2759浏览量

173275

原文标题:PCB走线角度选择不该90°? — PCB Layout 跳坑指南

文章出处:【微信号:zfdzszy,微信公众号:张飞电子实战营】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请问pcb板上信号线可以从lm324下面打孔穿过吗?

请问利用SPICE模型能不能进行PCB的SI仿真?

UTB定位技术能不能精准定位

探索电路板pcb螺旋走线的特点

同VLAN不同的网段能不能互通?

为什么晶振下方不能走信号线?

UPS电源是什么?UPS能不能带感性负载?

pcb走线的规则设置方法介绍

高速PCB信号走线的九大规则

PCB能不能以锐角走线,怎样避免拉线时出现锐角

PCB能不能以锐角走线,怎样避免拉线时出现锐角

评论