我们已经置身于大数据时代,相信大家对此不会有什么异议。根据国际数据公司(IDC)的预测,到2025年,全球被创建、采集或复制形成的数据集合规模将达到175ZB,这个数值接近2018年32ZB的5.5倍!而且这些数据的来源大大超出了传统IT行业的范畴,涵盖了工业制造、医疗保健、金融服务、媒体娱乐等实体经济的方方面面。将数据比作驱动未来智能世界运转的“石油”,一点也不为过。

而就像我们将埋藏在地下的原油转化为可以利用的能源和原材料,需要一个完整的采掘、转化系统一样,想要挖掘出海量数据的价值,也需要相应的基础设施的支撑,数据中心就是这其中关键的基石,它为大数据的处理提供了充沛的算力。

有研究数据显示,2020年全球经数据中心处理的数据流量高达15.3ZB,占全球总流量的99.35%。尽管随着边缘计算的兴起,在网络边缘端处理数据的占比在增加,分担了一部分计算任务,但是边缘的智能化也反过来在推动作为云计算“大脑”的数据中心的进一步演进,因此对其算力的需求仍会不断攀升。

根据中国信通院的《数据中心白皮书2022》,2021年全球数据中心市场规模超过679亿美元,较2020年增长9.8%;预计2022年市场收入将达到746亿美元,总体保持着强劲而平稳的增势。

数据中心算力的提升,显然不是简单的规模叠加,而是要通过不间断的技术进步去满足快速增长的应用需求。归纳起来,数据算力的硬件支柱主要来自三个方面:

#1

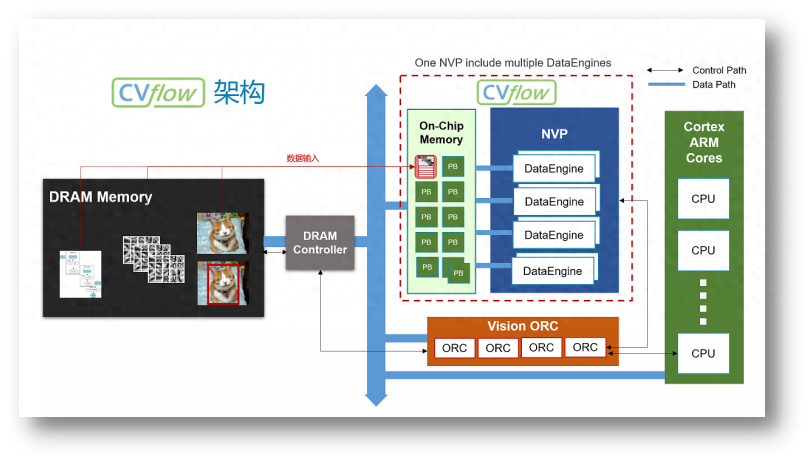

计算:高性能的处理器是其核心。除了x86、Arm等架构的处理器,近年来随着机器学习等技术的发展,基于GPU、FPGA等计算架构的AI加速设备在计算中心中也是屡见不鲜,以尽可能地提高计算的性能。

存储:存储设备也是关键的算力设备之一。从机械硬盘到固态硬盘,更大的存储密度、更快的读写速度、更高的可靠性,是存储技术永远的追求。

#2

#3

互连:支持数据在算力设备内部不同组件之间、在各个算力设备之间,以及在算力设备与外设之间快速、可靠地传输,是大数据处理不可或缺的一环。高速IO连接器和线缆等硬件互连组件是确保这一数据传输通道畅通无阻的关键。

特别需要指出的是,在算力提升的过程中,上述三个支柱技术一定要确保同步升级,任何一个方面的滞后,就会成为整个系统的“短板”。“计算”和“存储”两方面,很大程度上依赖于半导体技术的进步,摩尔定律确保了其技术发展的速度;而对于“互连”技术来讲,则需要提前布局和规划,定义好高速IO的传输协议和物理接口标准,以跟上前两种技术升级的脚步。

再具体到高速IO互连解决方案的开发上,在同步技术升级节拍的同时,连接器厂商还要根据实际的客户需求,做出差异化优势的产品,这样才能抢占先机,尽享大数据时代的红利。

在高速IO互连领域,Molex的表现一直非常抢眼。从连接器到线缆组件,以及完整的加速器卡,Molex都有相应的产品布局,而且在产品的设计上总是能够直击用户的“痛点”。

之所以能够做到这一点,主要得益于Molex牢牢把握住了大数据时代高速IO互连的“关键词”——这些关键词究竟有哪些?今天我们就从三款高速IO产品入手,一起来探究一下。

关键词一:高速

“高速”无疑是算力设备IO互连首要的追求。因为只有通过高速传输进一步提升数据吞吐量,才能够与性能越来越高的处理器、容量越来越大的存储设备相匹配。为此,人们定义了各类高速IO标准。

由小型封装(SFF)委员会创建的多源协议(MSA),为设备或组件之间的光模块互连确立了一个接口标准。经过多年的发展,这一标准已经从仅有一个通道、数据传输速率100Mbps至4Gbps的SFP接口,发展至最新的可以堆叠8个通道、每个通道数据速率为56Gbps(采用PAM4信号格式)、总带宽高达400Gbps的QSFP-DD接口。

Molex的QSFP-DD互连系统和电缆组件,就是遵循QSFP-DD这一最新规范设计的高速IO产品,以满足新一代数据中心发展的要求。

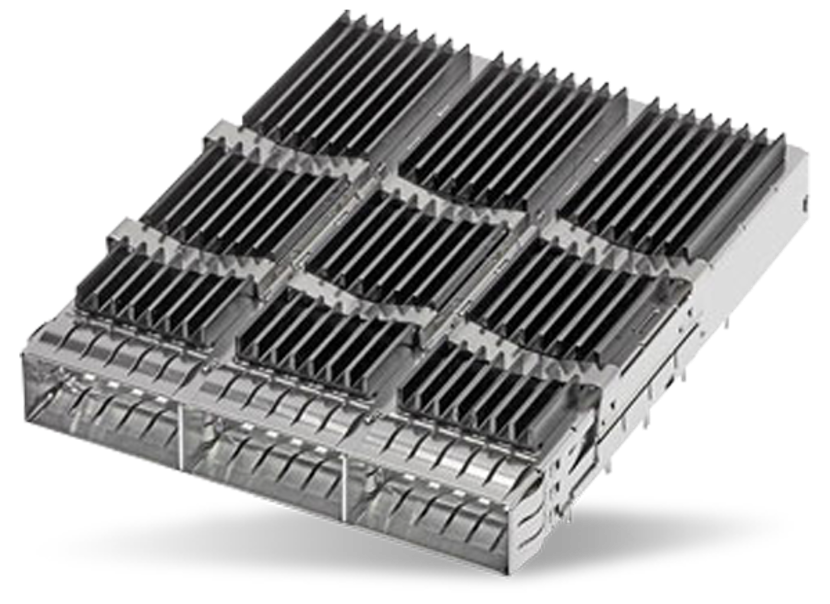

图1:QSFP-DD互连系统和电缆组件

(图源:Molex)

Molex的QSFP-DD互连方案的优势特性包括:

-

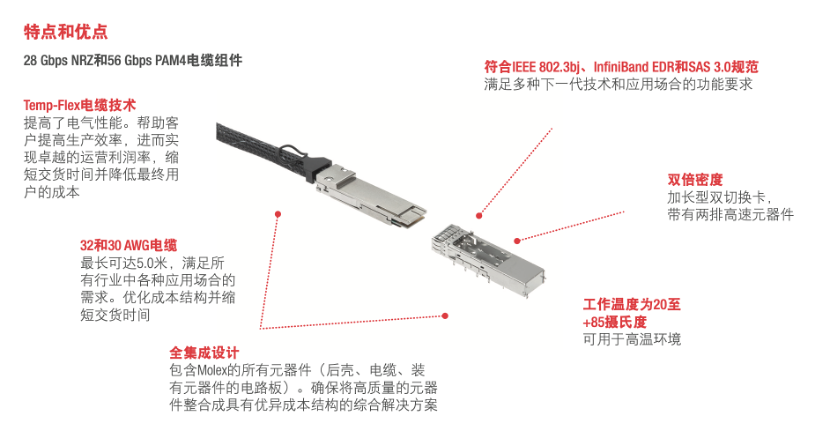

更高的数据传输速率:八通道电气接口,单通道数据传输速率高28Gbps NRZ或56Gbps PAM-4,总数据速率高达200Gbps或400Gbps。

- 双密度:支持双排高速环境的加长型双切换卡。

- 向后兼容:与前代QSFP互连系统具有相同占位,可确保向后兼容性,方便用户的系统升级。

- 应用广泛:符合IEEE 802.3bj、InfiniBand EDR和SAS 3.0规范,适用于各种前沿性的技术和应用。

- 独特的电缆技术:采用Temp-Flex电缆技术,有效提升互连系统的电气性能。

- 工作温度范围宽:-20°C至85°C的工作温度,可以适应数据中心等计算密集型应用的环境要求。

-

出色的可扩展性:提供不锈钢EMI笼罩、二合一堆叠式集成连接器和笼罩、表面贴装设计等不同配置的产品,支持长度范围500mm至2.5m的电缆组件,可满足不同应用设计的要求。

图2:QSFP-DD互连系统和电缆组件特点

(图源:Molex)

总之,Molex的QSFP-DD互连系统和电缆组件在传输速度方面,代表了高速IO的前沿水平,同时整合了Molex的优势资源,是一款优秀的产品。

关键词二:小型化

如果说“高速”代表着IO连接器在数据传输性能上的极致追求,那么“小型化”则是另一个关键的竞争赛道。这很好理解——今天的数据传输在确保“快”的同时,还需要在更小的空间内实现更高的连接密度,只有这样才能有力地支持数据中心实现更高的计算密度。

Molex的Nano-Pitch I/O互连系统就是为了满足这一技术趋势而开发的小型化、高密度、高速IO连接器。

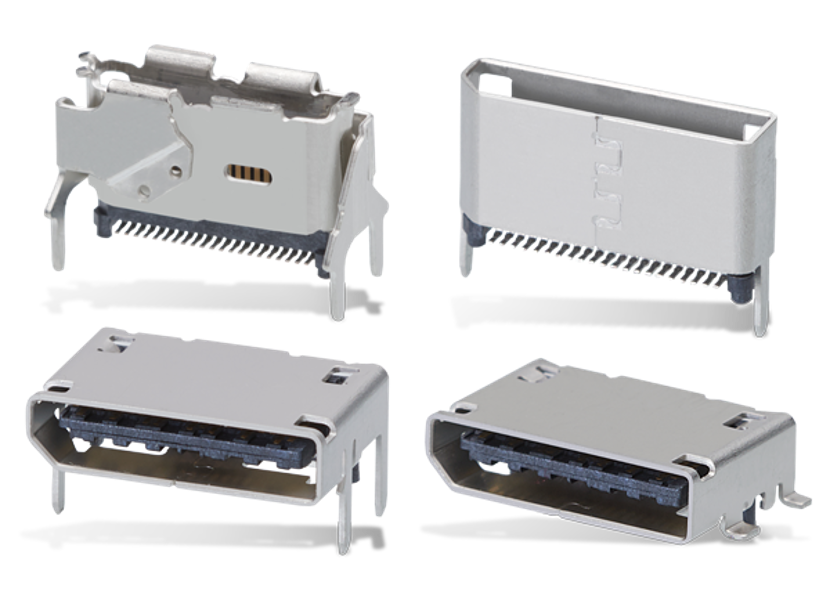

图3:Nano-Pitch I/O互连系统

(图源:Molex)

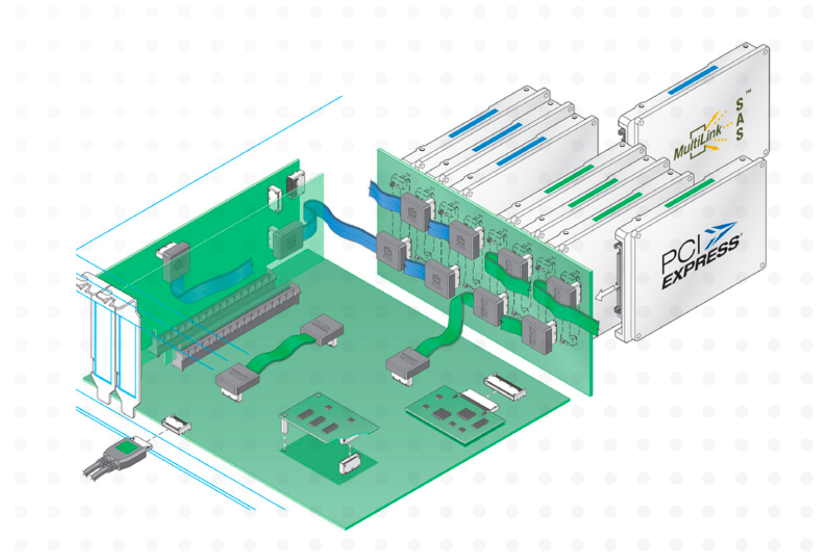

Nano-Pitch I/O互联系统采用为高速应用而优化的连续的接地-信号-信号-接地概念,可以实现每通道24Gbps的数据传输速率,并且能够尽可能地增加单位空间内高速通道的数量。而且该外形紧凑的连接器还具有多协议支持的特性,可兼容PCIe、SAS和SATA等主流的协议,包括PCIe Gen 4 (16GT/s) 和 SAS 4 (25Gbps)。

Nano-Pitch I/O互联系统的特性包括:

-

针对高速应用进行了优化,灵活引出线概念(连续的接地-信号-信号-接地)能够尽可能地增加互连密度。

- 多协议解决方案,符合各种主流行业标准,包括PCIe、SAS和SATA等。

- 具有小巧的外形(5.0 x 15.0 x 9.0mm)和较低的12.0mm连接器至电缆装配高度。

- 交错、可靠、一致的双排触点配置,支持热插拔,有利于减少PCB空间占用。

- 多功能金属外壳,支持低插接高度,可提供电缆侧被动或主动锁闩选项。

-

提供垂直和直角PCB安装选项,以及夹层和并联解决方案,支持更高的系统设计灵活性。

图4:Nano-Pitch I/O互连系统应用示意

(图源:Molex)

可以说,Nano-Pitch I/O系统很好地解决了高速IO设计中空间和性能之间平衡的问题,凭借出色的端口密度、多协议支持和更强的信号完整性,为下一代服务器和存储等算力设备互连提供了一个小型化、高性价比的解决方案。

关键词三:可扩展

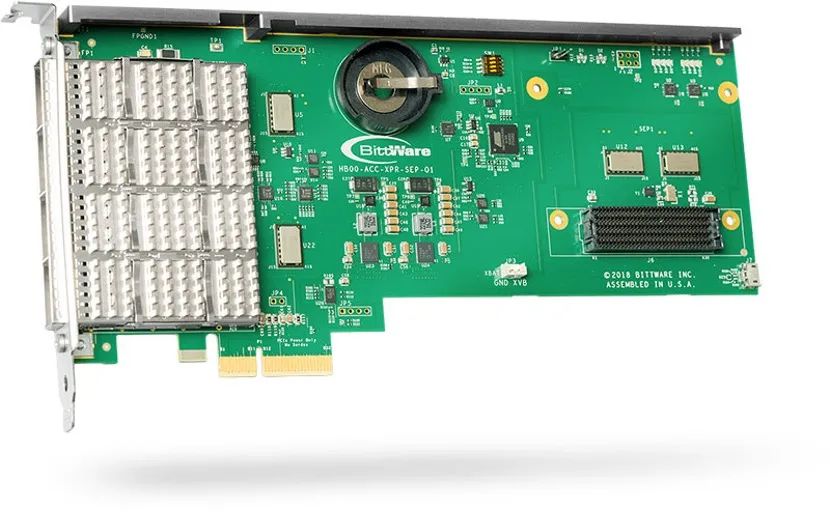

前文提到,面对高算力的挑战,如今的数据中心越来越多地用到FPGA等硬件资源去进行计算加速,FGPA加速器卡也就应运而生了。Molex通过收购BittWare公司,也进入到了FPGA加速器卡这个方兴未艾的领域,以期为客户提供更全面的数据中心解决方案。

BittWare XUP-P3RFPGA加速器卡是其中一款代表性的产品。在计算性能方面,该加速器卡基于Xilinx的Virtex UltraScale+ FPGA,支持高达512GB的内存,为需要大量数据流和数据包处理的系统提供高性能、高带宽和低延迟的特性。在接口方面,XUP-P3R配置了四个前面板QSFP笼罩和连接器,每个QSFP接口可支持高达100Gbps的数据带宽。而且,XUP-P3R还集成了一个板卡管理控制器(BMC)用于系统监控,这大大简化了QSFP平台的集成和管理。所有这些特性综合起来,使得XUP-P3R成为了数据中心算力提升的理想选择。

图5:XUP-P3RFPGA加速器卡

(图源:BittWare)

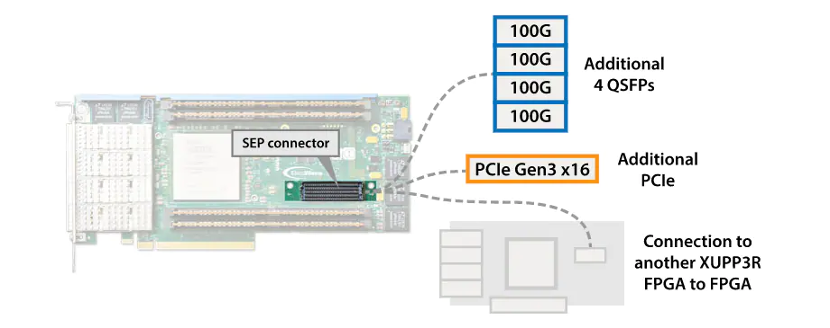

不过, 在这里我们想重点介绍的,是XUP-P3R FPGA加速器卡在高速IO方面一个出色的设计,那就是SEP(串行扩展端口)模块。顾名思义,SEP的目的就是为方便FPGA加速器卡扩展出更多的新功能,能够将FPGA澎湃的算力充分释放出来,支持更多的应用场景。这种“可扩展性”对于快速迭代的数据中心应用来说,无疑是一个非常关键的特性。

图6:XUP-P3R FPGA加速器卡中的SEP模块

(图源:BittWare)

具体来讲,SEP模块的“扩展”方式有三种:

01

第一种方式是提供额外的PCIe Gen3 x16接口。因为许多FPGA所需的PCIe连接仅通过主卡边缘的那个“手指”形插口是不够的,这时通过SEP这个额外的插槽就可以提供第二个PCIe Gen3 x16接口。

图7:SEP模块扩展的PCIe Gen3 x16接口

(图源:BittWare)

02

第二种方式是提供额外的4x QSFP28接口。对于一些客户来说,增加专有接口是一个关键的设计需求,通过SEP可以连接BittWare专门设计的子卡,为客户的FPGA扩展出总共8个QSFP28高速IO接口。

图8:SEP模块扩展的4x QSFP28接口

(图源:BittWare)

03

第三种应用是和其他的附加卡或者另一个XUP-P3R加速器卡互连,实现特定的扩展功能。比如下图这个附加卡就是为SDI SFP视频模块而设计的,通过SEP连接后可以方便客户快速建立一个概念验证设备,用于捕获视频并将数据传输给FPGA进行处理。

图9:SEP模块扩展到8x 12G-SDI视频模块(图源:BittWare)

FPGA提供出色的高算力,SEP模块又带来高度的可扩展能力,在这两大特性的加持下,XUP-P3R加速器卡也就确立了自己的竞争优势。

本文小结

根据IDC发布的《2022年全球大数据支出指南》,全球大数据市场的IT总投资规模在2021年为2176.1亿美元,到2026年将增至4491.1亿美元,年复合增长率高达15.6%。想要抓住机会参与这场市场盛宴,高算力是一块关键的“敲门砖”。

我们同时也看到,算力的提升除了要在处理器、存储设备上不断挖潜,以高速IO为代表的新一代互连技术同样不容忽视。而在打造高速IO互连产品时,参透了高速、小型化、可扩展这些核心关键词,你也就把握住了成功的关键。从本文介绍的这几款Molex高速IO产品和方案,你是否也体会到了其中的深意呢?

Molex高速IO解决方案

Molex QSFP-DD互连系统和电缆组件,了解详情>>

Molex Nano-Pitch I/O互连系统,了解详情>>

BittWare XUP-P3R FPGA加速器卡,了解详情>>

该发布文章为独家原创文章,转载请注明来源。对于未经许可的复制和不符合要求的转载我们将保留依法追究法律责任的权利。

关于贸泽电子贸泽电子(Mouser Electronics)是一家全球授权半导体和电子元器件授权分销商,服务全球广大电子设计群体。贸泽电子原厂授权分销近1,200家知名品牌,可订购数百万种在线产品,为客户提供一站式采购平台,欢迎关注我们,获取第一手的设计与产业资讯信息!

更多精彩

原文标题:“算力为王”的大数据时代,高速IO互连的三个关键词

文章出处:【微信公众号:贸泽电子】欢迎添加关注!文章转载请注明出处。

-

贸泽电子

+关注

关注

16文章

1122浏览量

96707

原文标题:“算力为王”的大数据时代,高速IO互连的三个关键词

文章出处:【微信号:贸泽电子,微信公众号:贸泽电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

气密性检测干货!150个核心关键词,一文看懂

浅析三大算力之异同

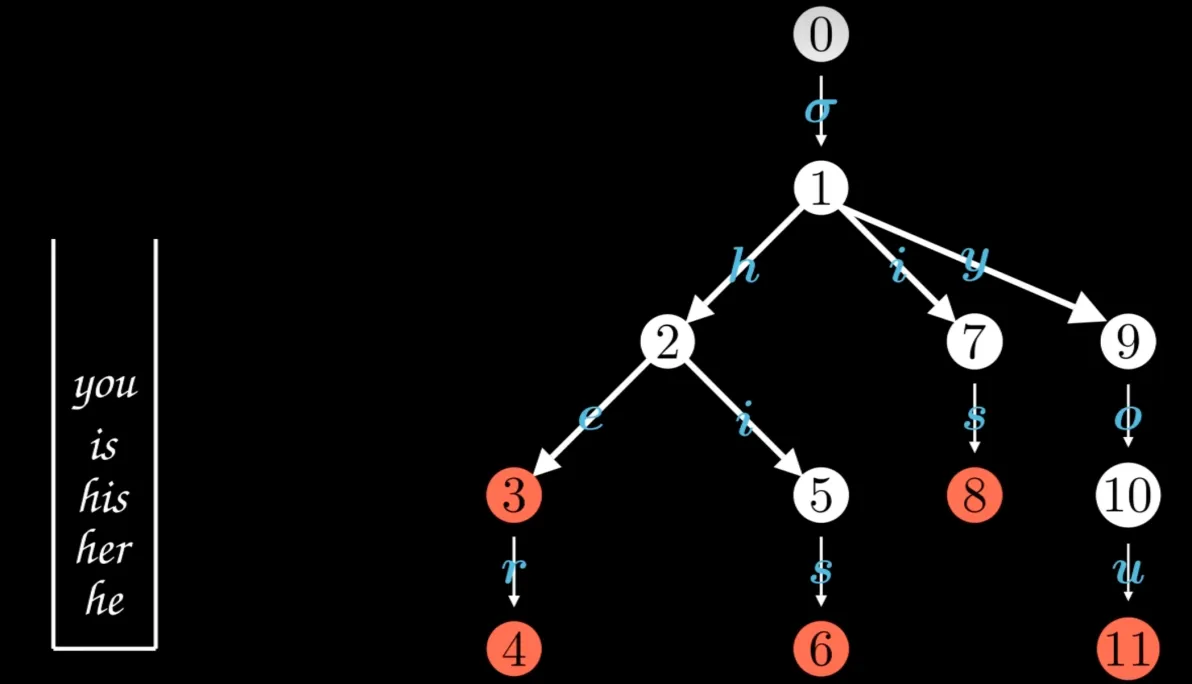

探索AC自动机:多关键词搜索的原理与应用案例

大模型时代的算力需求

中国信通院发布“2024云计算十大关键词”

芯耀辉科技解读高速互连对于AI和大算力芯片而言意味着什么?

深开鸿用三个关键词,为你解读《2023 OpenHarmony 年度运营报告》

“算力为王”的大数据时代,高速IO互连的三个关键词

“算力为王”的大数据时代,高速IO互连的三个关键词

评论