传统观点认为,如果您非常关心延迟,那么尝试将系统内存连接到 PCI-Express 总线并不是一个好主意。因为内存离 CPU 越远,延迟就越高,这就是内存 DIMM 通常尽可能靠近插槽的原因。

从逻辑上讲,PCI-Express 是千里之外的。随着每一代 PCI-Express 带宽翻倍,如果没有重定时器的帮助也会增加延迟,它可以传输的距离也会缩短。对于我们习惯于连接到 PCI-Express 的大多数类型的内存来说,这不是什么大问题。闪存存储的延迟以几十微秒为单位的情况并不少见,这使得互连产生的额外几百纳秒成为一个有争议的问题。然而,我们对DDR 和其他形式的易失性存储器就没有那么宽容了。

以前的内存扩展尝试都陷入了妥协,特别是在延迟方面。例如,GigaIO 表示其FabreX 架构已经可以使用 DMA 在 PCI-Express 上进行内存池化,但这样做需要应用程序能够容忍 500 纳秒到 1.5 微秒的延迟。

同样,根据 Blocks and Files 的说法,在英特尔今年夏天毫不客气地削减其 Optane 持久内存业务之前,部署该技术意味着会产生大约350 纳秒的延迟。虽然可用,尤其是在分层内存配置中,但它比直接连接 CPU 的 DDR 内存预期的低于 100 纳秒的往返延迟要长得多。

进入 CXL 内存生态系统

这为我们带来了使用 Compute Express Link 协议或 CXL 的第一代内存扩展模块。基于 AMD 的Epyc 9004“Genoa”处理器的系统是首批系统之一,拥有 64 条 CXL 连接通道——不同于其 128 至 160 条整体 PCI-Express 通道——最多可分为四到十六个设备。至于英特尔将如何在其“Sapphire Rapids”Xeon SP 处理器上实施 CXL,我们将不得不等到它们明年初问世。

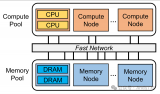

与这些服务器相得益彰的是我们确信的第一个是许多 CXL 内存扩展模块。虽然 CXL 最终将允许完全分解的系统,在这些系统中,资源可以通过高速结构在整个机架上共享,但距离那一天还有几年的时间。

对于首次涉足数据中心,CXL 直接专注于内存扩展、分层内存和一些早期的内存池应用程序。目前,我们只关注内存扩展,因为在这个早期阶段,它可以说是最简单和最实用的,尤其是在以可用延迟附加内存时。

三星和Astera Labs已经展示了 CXL 内存模块,他们说只需将它们插入兼容的 PCI-Express 5.0 插槽,即可为系统添加数 TB 的内存。从系统的角度来看,它们的外观和行为就像通过内存总线连接到相邻插槽的常规 DDR DRAM 内存。

在最长的时间里,一旦达到 CPU 内存控制器的限制,添加更多内存的唯一方法就是添加更多插槽。如果工作负载可以利用额外的线程,那就更好了,但如果不能,这将成为一种非常昂贵的添加内存的方式。实际上,额外的插槽只是一个内存控制器,上面附有一堆昂贵的、不需要的内核。

内存扩展模块的行为方式大致相同,但它不是使用专有的插槽到插槽互连,如英特尔的 UPI 或 AMD 的 xGMI 链接,而是 CXL。这意味着您可以拥有这些设备的整个生态系统,事实上,我们已经看到一个相当充满活力,有时甚至是令人向往的设备围绕 CXL 展开。

CXL 总裁 Siamak Tavallaei在 SC22上告诉 The Next Platform ,CXL 实际上包含三种协议,但并非所有协议都是延迟的灵丹妙药。“CXL.io 仍然具有您预期的相同类型的延迟(来自 PCI-Express),但其他两个协议——CXL.cache 和 CXL.mem——通过协议采用更快的路径,并且它们减少了延迟。”

CXL 内存延迟到底有多糟糕?

如果 Astera 值得信任,延迟并不像您想象的那么糟糕。该公司的Leo CXL 内存控制器旨在接受高达 5600 MT/秒的标准 DDR5 内存 DIMM。他们声称客户可以预期延迟与访问第二个 CPU 上的内存大致相当,一个 NUMA 跃点。这使得它在 170 纳秒到 250 纳秒附近。事实上,就系统而言,这正是这些内存模块向操作系统显示的方式。

Tavallaei 解释说,大多数 CXL 内存控制器会增加大约 200 纳秒的延迟,额外的重定时器会增加或花费几十纳秒,具体取决于设备与 CPU 的距离。这与其他 CXL 早期采用者所看到的一致。GigaIO 首席执行官 Alan Benjamin 告诉The Next Platform,它所见过的大多数 CXL 内存扩展模块的延迟都接近 250 纳秒,而不是 170 纳秒。

然而,正如 Tavallaei 指出的那样,这仍然是对四插槽或八插槽系统的改进,在这些系统中,应用程序可能仅仅因为需要内存而不得不应对多个 NUMA 跃点。(不过,公平地说,IBM 和英特尔在 CPU 之间添加了更多更快的链接,以减少跳数和每跳延迟。)

话虽如此,许多芯片制造商很快指出,CXL 生态系统现在才刚刚起步。在 CXL 董事会任职的 AMD 的 Kurtis Bowman 告诉The Next Platform,许多早期的 CXL 概念验证和产品都使用尚未针对延迟进行优化的 FPGA 或第一代 ASIC。随着时间的推移,他预计延迟会大大改善。

如果 CXL 供应商能够像他们声称的那样,在展厅演示之外实现与多插槽系统同等的延迟,那么它应该在很大程度上消除利用它们所需的应用程序或操作系统特定定制的需要。好吧,至少就内存扩展而言。正如我们在 Optane 中看到的那样,CXL 内存分层几乎肯定需要某种操作系统或应用程序支持。

随着插槽变得越来越大并且在板上安装更多 DIMM 变得越来越难,这再合适不过了。放置它们的地方更少了。有可容纳 32 个 DIMM 的双插槽系统,但随着芯片制造商增加更多通道以满足更高核心数的带宽需求,这是不可扩展的。

我们已经在某种程度上在 AMD 的 Genoa 芯片上看到了这一点,尽管该芯片将内存通道数量增加到 12 个,但在发布时每个通道仅支持一个 DIMM,将双插槽配置中的 DIMM 数量限制为 24 个。即使您可以为每个通道连接两个 DIMM,我们被告知将 48 个 DIMM 安装到标准机箱中是不切实际的。

当我们希望在更远的距离(例如跨机架)连接内存时,事情会变得更加复杂,因为电或光互连产生的延迟必须计入方程式。但对于机箱内 CXL 内存扩展,延迟似乎并不像许多人担心的那么令人头疼。

审核编辑 :李倩

-

amd

+关注

关注

25文章

5479浏览量

134311 -

内存

+关注

关注

8文章

3037浏览量

74151 -

生态系统

+关注

关注

0文章

703浏览量

20746

原文标题:CXL,面临严峻的延迟问题

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

内存扩展CXL加速发展,繁荣AI存储

24位或者说高分辨率的AD到底有什么用呢?

差分输入和和单端输入在本质上到底有什么区别?

高铁站网约车数智出行到底有多智能

研华科技推出SQRAM CXL 2.0 Type 3内存模块SQR-CX5N

业界首创512GB CXL AIC内存扩展卡,江波龙革新AI与高性能计算领域内存技术

FORESEE CXL 2.0内存拓展模块

利用CXL技术重构基于RDMA的内存解耦合

CXL内存延迟到底有多糟糕?

CXL内存延迟到底有多糟糕?

评论