最近ChatGPT大火,成功破圈,到底是什么?怎么使用?

简单说,它是一个模型,一个语言模型!

它是以对话方式与人进行交互的AI语言模型!

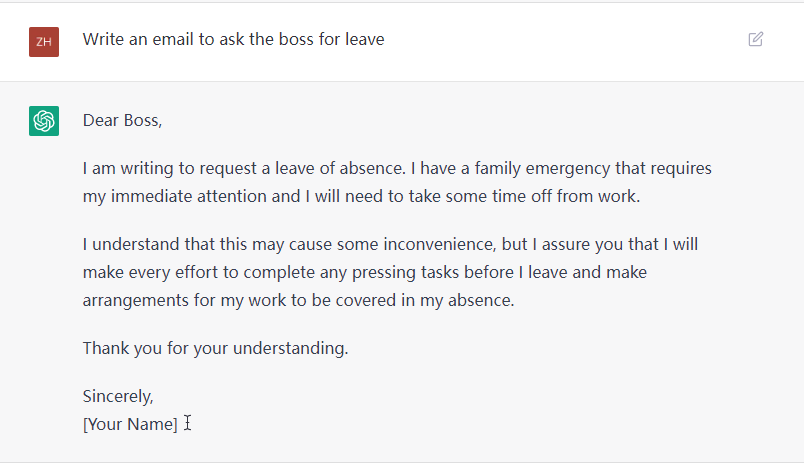

但它能做的事情太多了,可以用它来写一封请假邮件:

image-20221208210153673

image-20221208210153673还有人用它来学英语、向它提各种问题,甚至可以用它来写程序,很多软件工程师都尝试过用它来写Python、Java等编程语言,这里我们就不再尝试了。

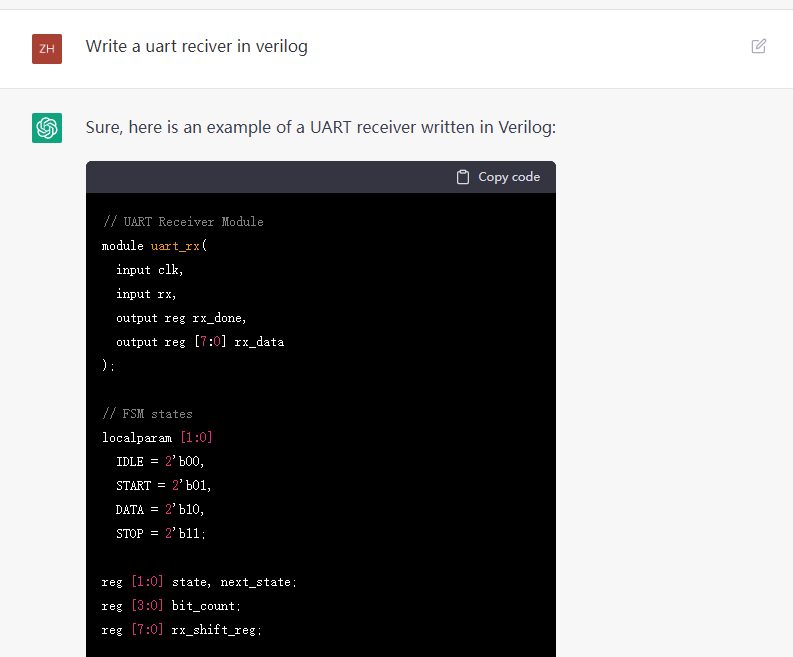

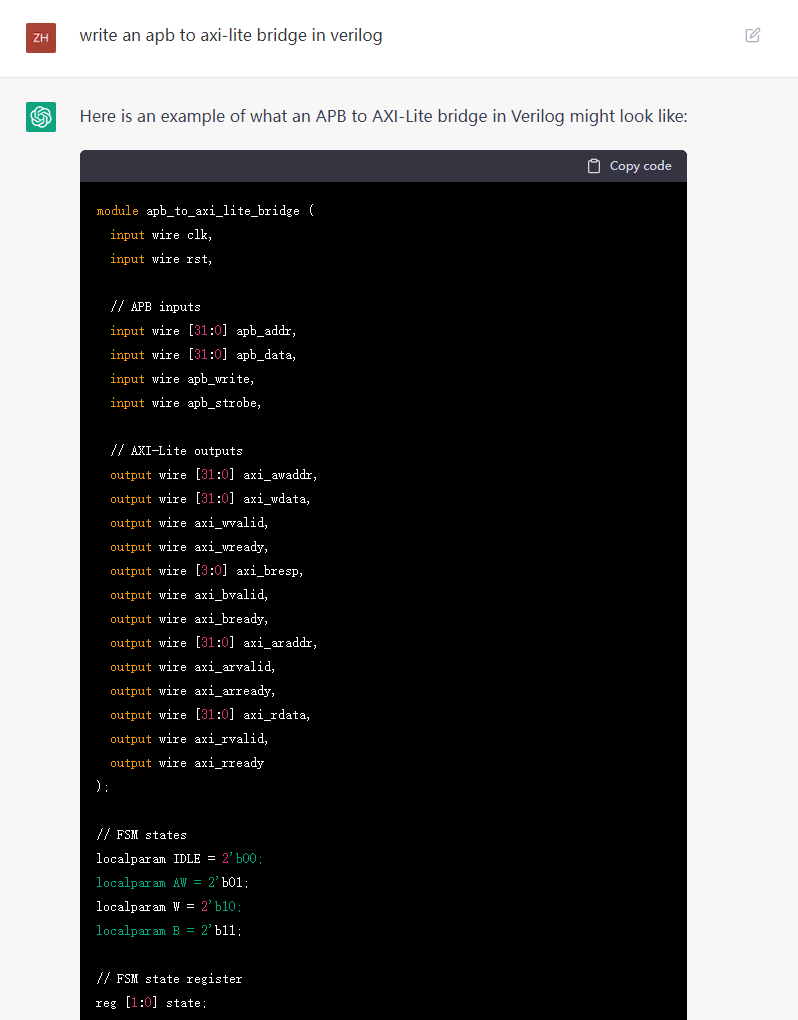

作为FPGA工程师,我们肯定想让它帮我们写Verilog!看看效果怎么样?

image-20221208210533770

image-20221208210533770在代码后面甚至还有解释:

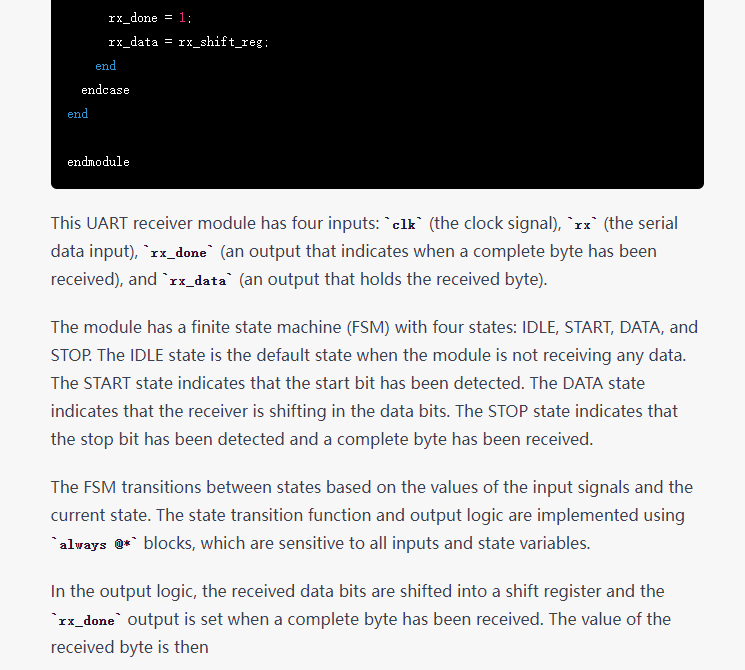

image-20221208210631379

image-20221208210631379完整代码如下:

//UARTReceiverModule

moduleuart_rx(

inputclk,

inputrx,

outputregrx_done,

outputreg[7:0]rx_data

);

//FSMstates

localparam[1:0]

IDLE=2'b00,

START=2'b01,

DATA=2'b10,

STOP=2'b11;

reg[1:0]state,next_state;

reg[3:0]bit_count;

reg[7:0]rx_shift_reg;

//Initializeoutputs

always@*begin

rx_done=0;

rx_data=0;

end

//Statetransitionlogic

always@(posedgeclk)begin

state<= next_state;

end

//Statetransitionfunction

always@*begin

case(state)

IDLE:begin

if(rx)next_state=START;

elsenext_state=IDLE;

end

START:begin

if(rx)next_state=DATA;

elsenext_state=IDLE;

end

DATA:begin

if(bit_count==0)next_state=STOP;

elseif(rx)next_state=DATA;

elsenext_state=IDLE;

end

STOP:begin

if(rx)next_state=IDLE;

elsenext_state=STOP;

end

endcase

end

//Outputlogic

always@*begin

case(state)

IDLE:begin

bit_count=4;

rx_shift_reg=0;

end

START:begin

bit_count=3;

end

DATA:begin

bit_count=bit_count-1;

rx_shift_reg={rx_shift_reg[6:0],rx};

end

STOP:begin

rx_done=1;

rx_data=rx_shift_reg;

end

endcase

end

endmodule

虽然没有验证这个功能是否正确,但这个代码的逻辑看起来应该是没有错的。

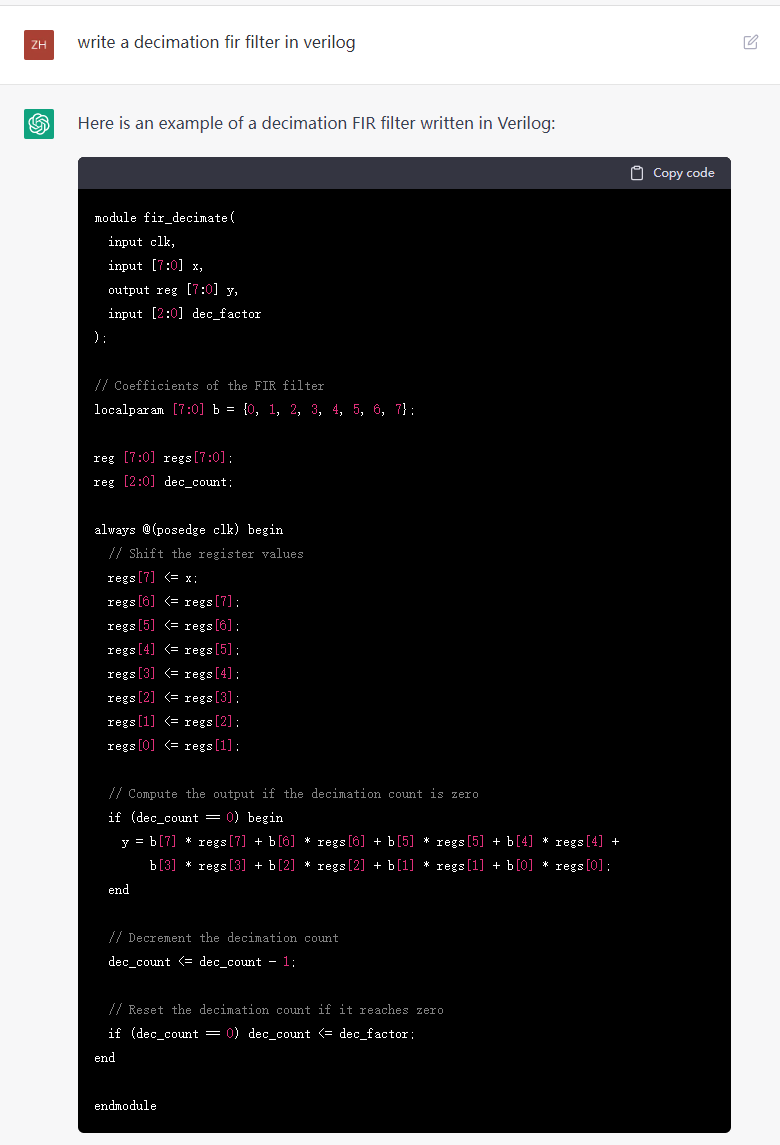

再写个稍微复杂一点但仍然是标准的协议:apb转axi-lite的bridge。

完整代码很长,我也并没有验过,但大概看下来,功能基本都有。

对于过于复杂的,就无能为力了,比如:以太网协议栈。

但有个更有意思的现象,当我第一次让它写以太网协议栈时,它提示太难了,写不出来。

把对话复位后,再让它写,它就会写一个大概的module,里面只有些接口,后面又复位对话后再重新让它写了,写出来的程序就更多了。

说明它的学习能力一直在增长。

可能现在它的功能还并不是很完善,但作为工程师,看到这么强大的功能,不禁有些感慨,我们的核心竞争力是什么?如果真的有一天,AI可以帮我们写代码了,我们该去做什么?

(抖个机灵:是不是到时候只需要验证工程师了?)

最后补充一点,这个网站的注册是需要一个国外的手机号,可能很多人弄不到,所以,如果你有什么有趣的功能想尝试,可以跟我联系,我来帮你试。

审核编辑 :李倩

-

Verilog

+关注

关注

31文章

1374浏览量

114725 -

AI

+关注

关注

91文章

41156浏览量

302619 -

语言模型

+关注

关注

0文章

575浏览量

11343

原文标题:如何用AI来写Verilog代码?

文章出处:【微信号:傅里叶的猫,微信公众号:傅里叶的猫】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Vibe Coding AI全栈开发实战

Token烧了几十亿,代码还是一团乱!AI原生开发该怎么管理?

嵌入式AI开发必看:杜绝幻觉,才是工业级IDE的核心底气

AI辅助编程设计之道:从Spec到Code工程实践

还在手动拼接 AI 代码?你的 IDE 早就该升级了

Transformer 入门:从零理解 AI 大模型的核心原理

TI DMD代码

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片的需求和挑战

代码如何重塑硬件设计,AI如何加速创新?

AI的未来,属于那些既能写代码,又能焊电路的“双栖人才”

HarmonyOS AI辅助编程工具(CodeGenie)代码智能解读

HarmonyOS AI辅助编程工具(CodeGenie)代码续写

如何用 C# 代码对 FX3/CX3 的 EEPROM 进行编程?

如何用FastMCP快速开发自己的MCP Server?

如何用AI来写Verilog代码?

如何用AI来写Verilog代码?

评论