本文作者:杜燕燕

Cadence公司 Pegasus Product Engineering Team

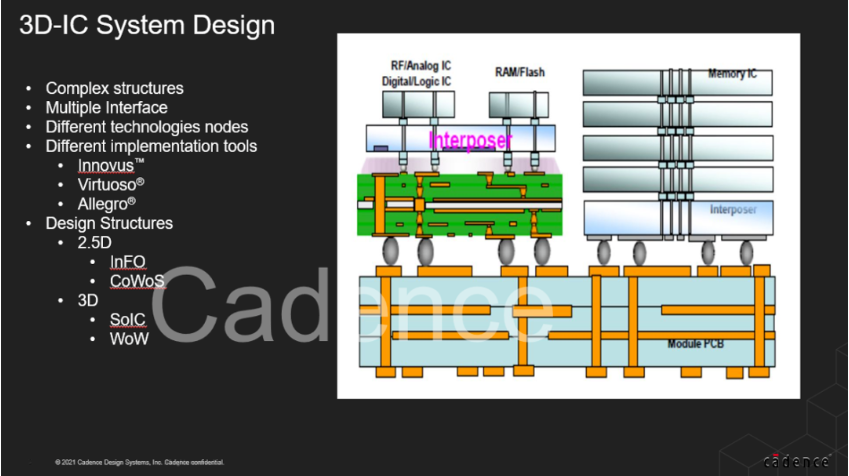

随着芯片工艺尺寸的缩小趋于饱和或停滞,设计师们现在专注于通过 3D-IC 异构封装,在芯片所在平面之外的三维空间中构建系统。3D-IC 异构封装结构可能包括多个芯片,它们被放置在一个通用的中介层上,或者通过芯片内部的高级互连来集成内存单元、处理器和其他功能模块。

3D-IC 异构封装中集成了功能不同的芯片,这些芯片可以采用不同的工艺节点,也可以通过不同的 3D 结构来堆叠,而且芯片、中介层、封装之间会形成多个接触面,系统级的物理验证变得很复杂,将面临很多不同方面的挑战:

013D-IC 设计中不同模块的数据来自于不同的设计工具,设计师面临着合并来自于不同平台的物理数据然后去完成系统性的物理验证和分析的挑战。

02不同的芯片可能来自于不同的 Foundry,采用不同的工艺,有着不同的物理验证规则,如何统一出一个系统级物理验证规则?

03不同的 3D 结构中芯片和中介层的堆叠方式不同,设计师需要根据每个客户的设计去定制不同的 LVS / ERC / DRC 验证规则。

04每个不同的堆叠层和堆叠层间的接触面都需要单独的进行 LVS / ERC / DRC 检查。

05每个接触面都需要分别的进行 GDS 合并去做 LVS / ERC / DRC,如何能够无缝连接的合并不同设计平台的数据并且在验证中将数据可视化?

06当芯片个数增加时,验证的复杂度和工作量都会大大增加。

如何解决这些挑战,让我们先来看一下

3D-IC物理验证的要求

对于 3D-IC 物理验证,我们并不是指单颗 die 的物理验证,而是指不同的堆叠层接触形成电气连接所需要进行的:

电气规则检查(ERC)

设计规则检查(DRC)

版图原理图一致性检查(LVS)

电气规则检查 ERC / 物理规则检查 DRC

(Electrical Rule Checking / Design Rule Checking)

2.5D IC 采用 Micro Bump 在不同接触面之间实现电气连接和应力缓冲,Bump 是一种金属凸点,常见的形状有球状和柱状,随着工艺技术发展,Bump 直径最早可达 200um,目前先进工艺中都是采用 Micro Bump,它以更小的间距和更好的导热性实现更多的 IO。

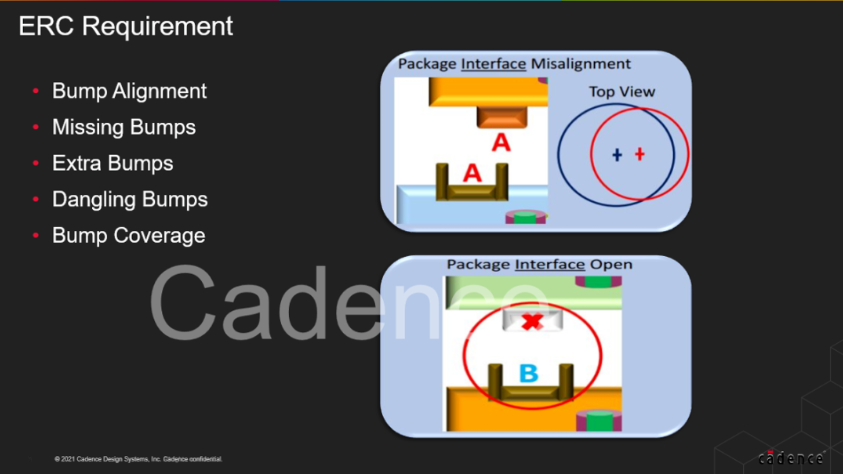

接触面 ERC 需要检查的项目主要包括:

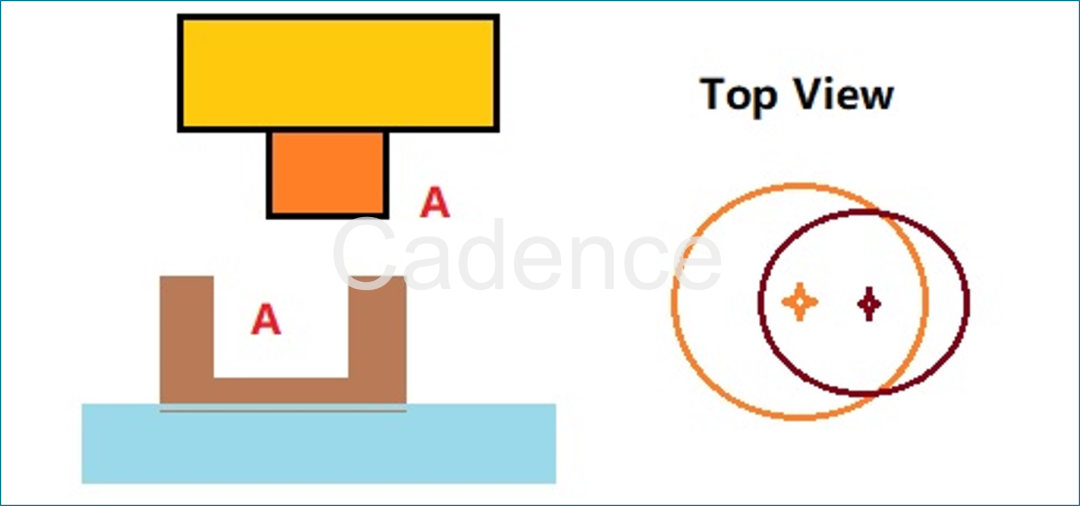

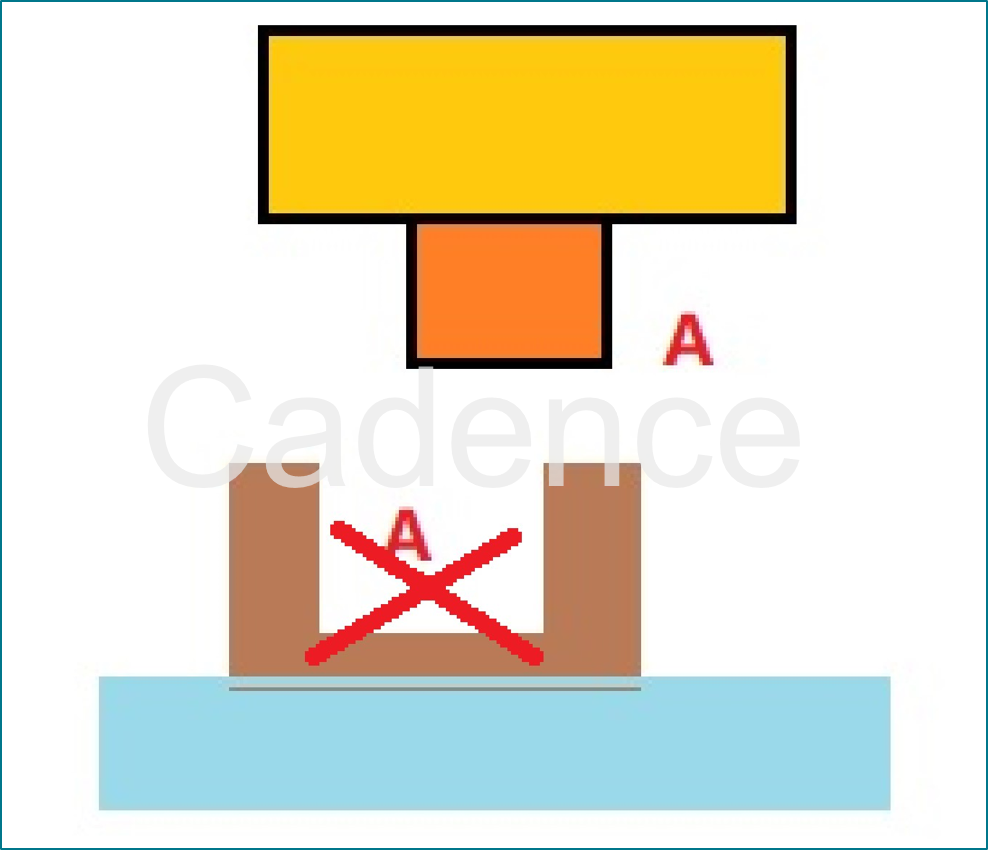

1Bump 对齐

检查 Bump 有没有放在正确的位置

2Bump 覆盖率

有些工艺不要求 Bump 完全对齐,两个 Bump 的形状大小也不同,这时可能要求两个 Bump 重合的区域占比达到一定的数值,80% 或者 90% 等。

3Bump 丢失 / 多余

检查是否有 Dangling 的 Bump。如下图所示,上面的 Bump 没有连接到其它任何 Bump 上,那么它就是一个 Dangling Bump,产生的原因有可能是上面的 Bump 多余或者下面丢失对应连接的 Bump。

版图原理图一致性检查 LVS

3D-IC 的 LVS 验证是多层次、系统性的,需要检查的项目主要包括:

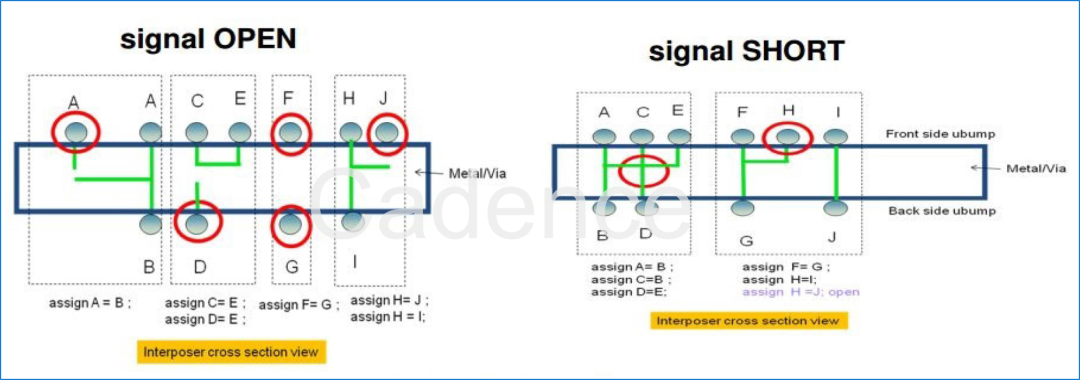

1接触面的连接性

包括 Bump 开路和 Bump 短路。

2中介层的连接性

2.5D 是将芯片集成在使用 Bump 作为表面连接的中介层上,中介层可以进行重布线和插入 TSV,提高互联密度。LVS 检查 Interposer 上表面的 Bump 信号和下表面 Bump 信号连接的正确性与否,包括信号的开路和信号的短路。

3封装基板的连接性

封装基板上表面 pin 到封装下表面 pin 之间的连接性也需要检查。

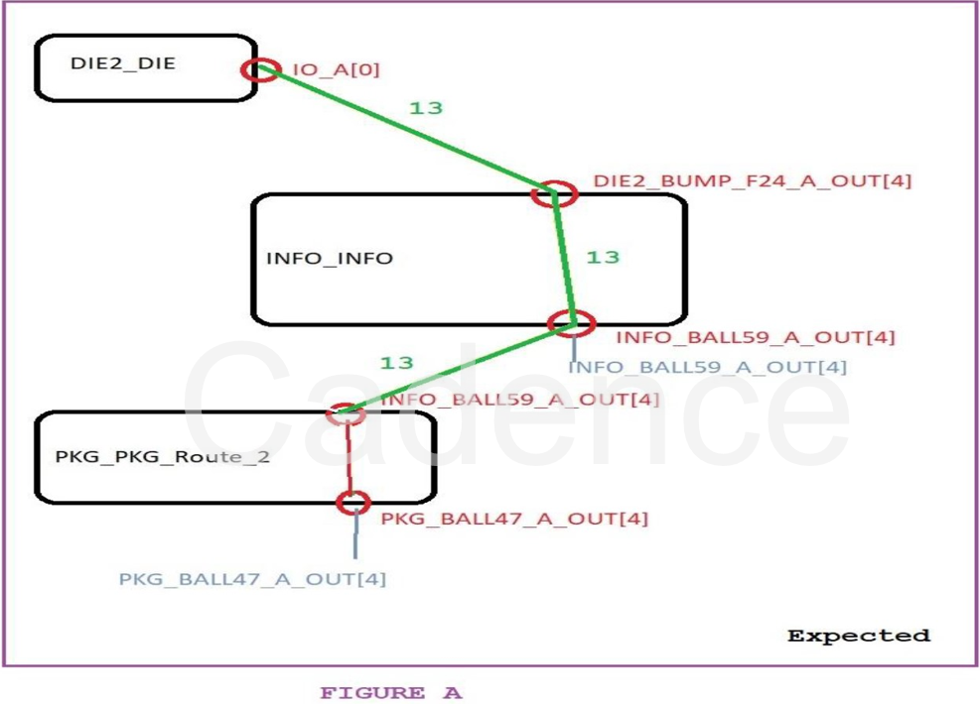

4系统层面的连接性

在系统层面,每个特定功能的芯片的端口的连接不仅要保证逻辑的正确性,并且在物理层面也应该有正确的连接性。

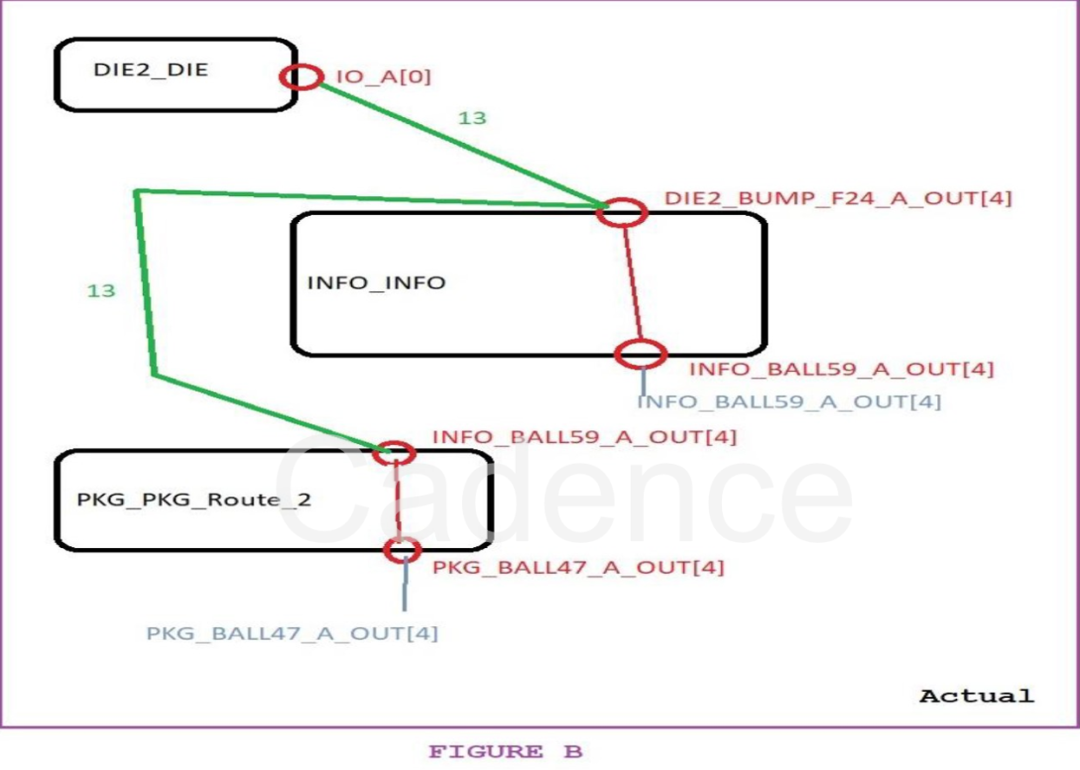

DIE2 的信号端口 IO_A[O] 连接:

IO_A[O] -> DIE2_BUMPF2_F24_A_OUT[4] -> INFO_BALLS9_A_OUT[4](INFO下面端口) -> INFO_BALLS9_A_OUT[4] (封装上面端口) -> PKG_BALL47_A_OUT[4]

这是正确的物理连接,也是期望的物理连接。

如果发生了这样的情况:

IO_A[O] -> DIE2_BUMPF2_F24_A_OUT[4] -> INFO_BALLS9_A_OUT[4] (封装上面端口) -> PKG_BALL47_A_OUT[4]

虽然逻辑上 IO_A[O] 最终连接到了PKG_BALL47_A_OUT[4],但是这并不是期望的物理连接,这种情况下LVS会报告连接性丢失。

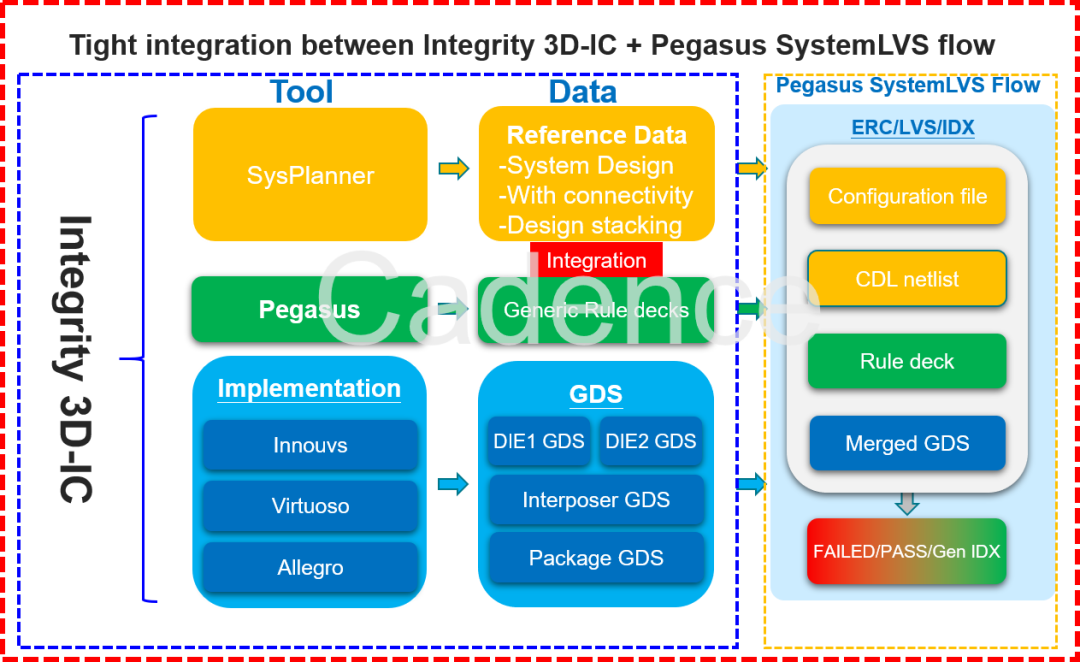

了解了物理验证的这些需求,让我们来看看 Integrity 3D-IC 平台 + Pegasus System-LVS 的解决方案如何应对 3D-IC 物理验证所面临的这些挑战:

Integrity 3D-IC 平台 + Pegasus System-LVS

解决方案

Cadence 的物理验证工具 Pegasus System-LVS 紧密集成在 Integrity 3D-IC 平台中:

01可以将不同设计工具的物理数据合并生成一个系统层面的 GDS,进行系统性的 LVS / ERC / DRC 检查。

02Pegasus System-LVS 不依赖 Foundry 的物理验证规则,也不需要根据不同 die 的工艺节点,不同的 3D 结构手动定制化物理验证规则,只要输入工艺相关的 GDS Layer Map 和 Connection 文件,就可以自动生成物理验证规则,完成 LVS / ERC / DRC 检查。

03可以根据用户的选择单独或者同时对某个堆叠层接触面或者堆叠层进行LVS / ERC / DRC 检查,也可以生成 IDX(Inter-Die-Xtalk Extraction)数据,可供 RC 抽取使用。

让我们来看下 Pegasus System-LVS 设计实例:

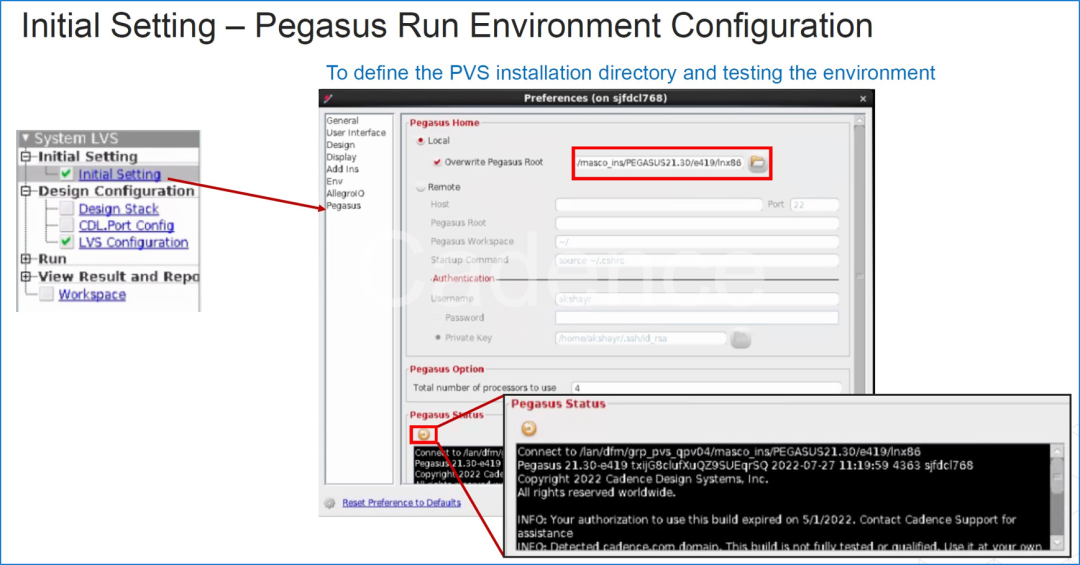

在 Integrity 3D-IC 平台中启动 Pegasus System-LVS 完成物理验证的操作步骤:

Step1

进行环境初始化时,在 Integrity 3D-IC 平台可直接启动 Pegasus 并查看安装路径,检测环境是否正确:

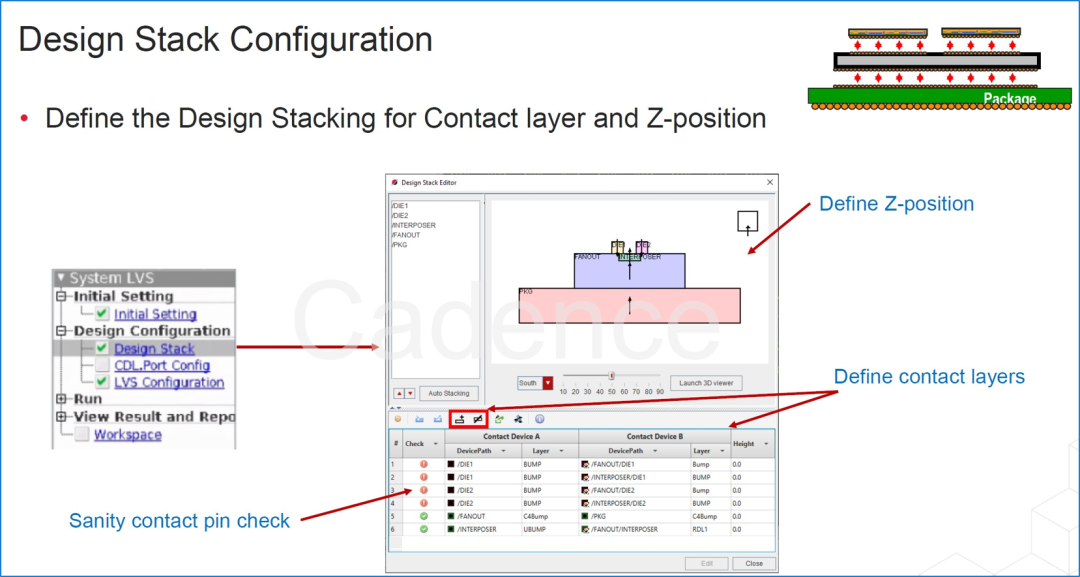

Step2

在 Integrity 3D-IC 平台中,3D-IC 设计的堆叠结构一目了然。在物理验证之前,可定义堆叠面的接触金属层和堆叠层的位置和朝向:

Step3

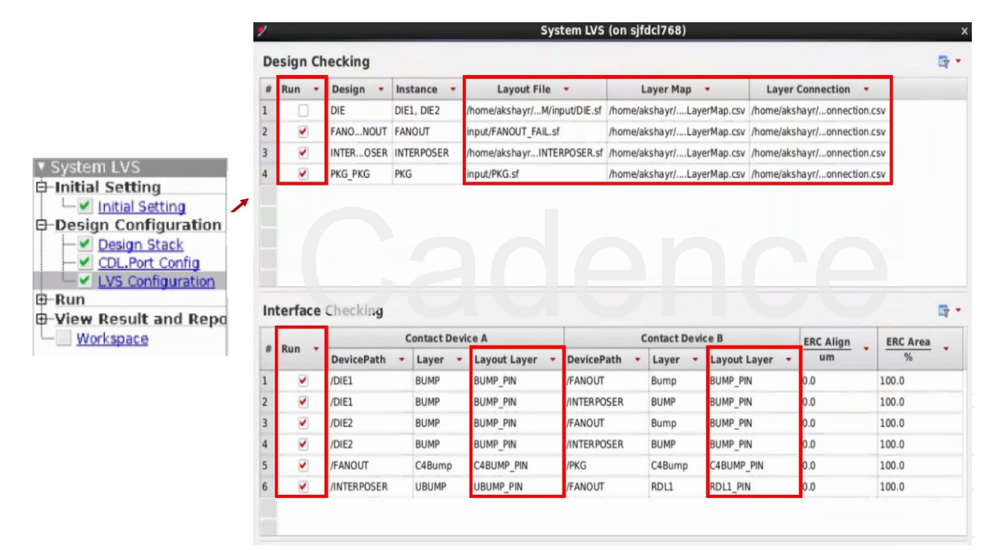

对 Pegasus System-LVS 的配置文件进行设置:

定义 GDS 文件路径

定义 Layermap / Layerconnect 文件

定义 GDS 的接触层

选择其中某个设计模块或者接触面进行检查

Step4

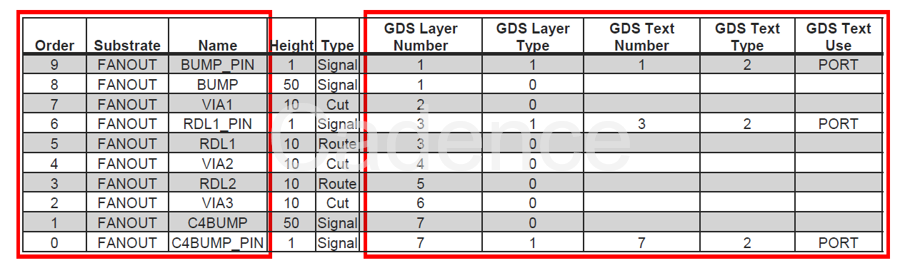

GDS layer 映射文件和连接性文件

Layer 映射文件:

- 定义了设计文件 GDS 中包含的 Layer 名字和 GDS Number 的映射关系。

- 下面红色圈出的部分需要手工输入。例如下图所示:

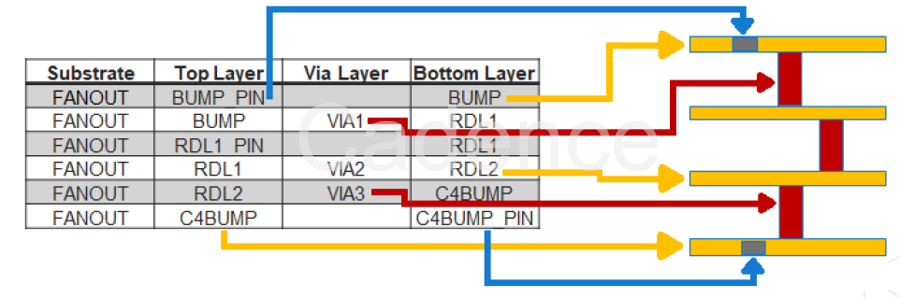

Layer 连接性文件:

- 指定了每个设计中 Layer 之间的连接关系,这些 Layer 需要在 Layer Mapping 文件中有过定义。

- 下图是一个连接性文件的例子以及实际的物理连接图:

Step5

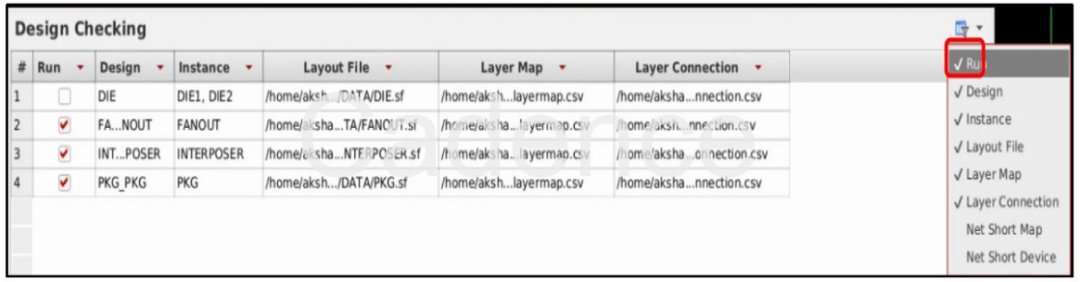

设计检查和接触面检查

设计检查:

- 在设计检查部分,用户可以选择检查某个设计模块或者只检查 Bump 的连接性。

- 此外,在设计检查部分除了可以手动输入例如 Layout File、Layer Map and Layer Connection 之外,还可以通过右上角的过滤按钮加入其他的输入文件,比如 Net Short Map 文件等。

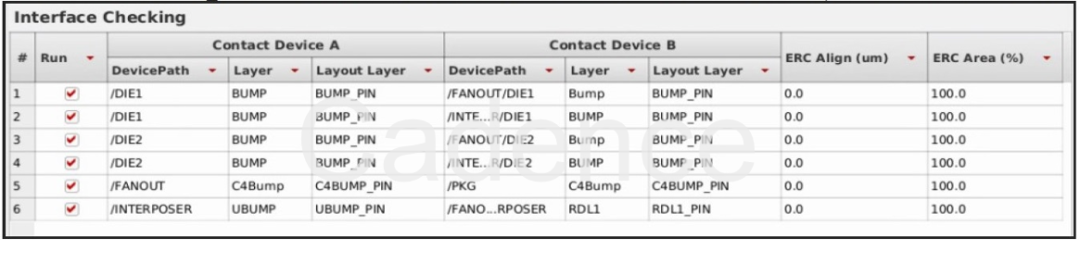

接触面检查:

- 在接触面检查部分,用户可以根据设计需要选择性地检查某个或者多个接触面。

- 此外用户可以控制 ERC 检查

ERC Align

1. 用户设置ERC Align的值, 正数表示需要对准的Bump中心间距的最大值。

2. ERC Align的值为负数表示不启动ERC Align 检查。

3. 误差值的单位是微米。

ERC Area

1. 用户设置ERC Area的值,表示需要对准的Bump面积重合的最小比值。

2. ERC Align的值为0或者大于100表示不启动ERC Area检查。

3. 误差值是面积的比值。

(注意:接触面检查部分也有过滤按钮可以加入或者过滤某些选项。)

Step6

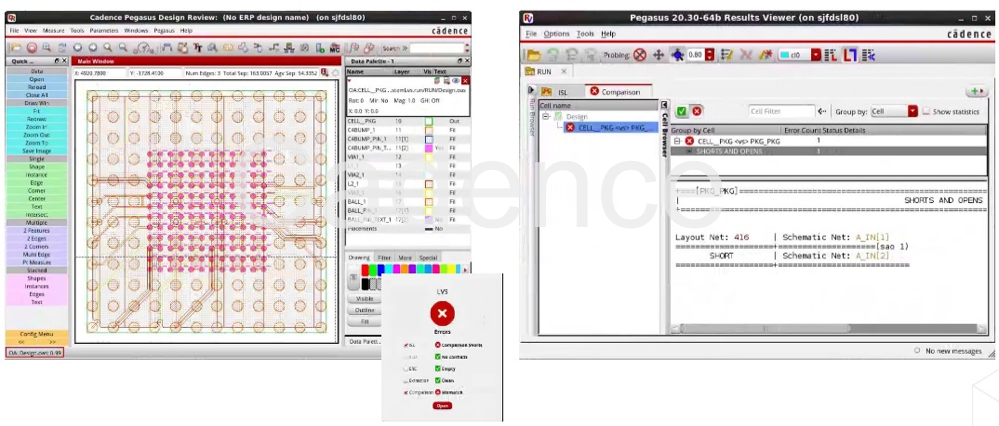

Results Viewer(RV)

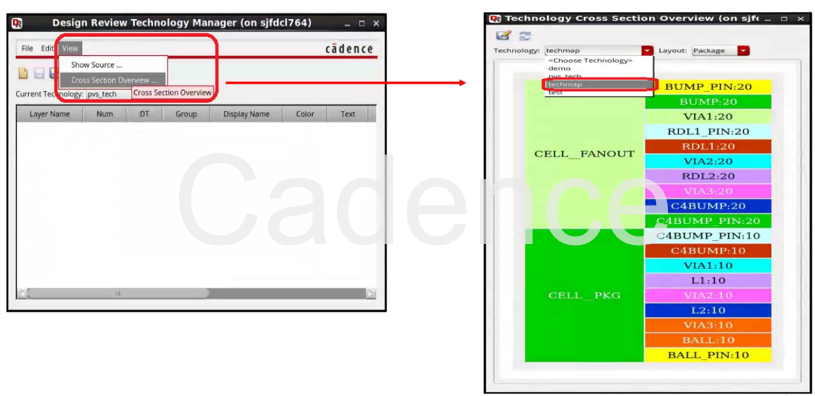

System-LVS 运行完之后 Sysplanner 会自动启动 Design Review 和 Results Viewer,用户可以很方便的进行 Probe 和 Debug。

下面左图是 Design Review,右图是 LVS Results Viewer:

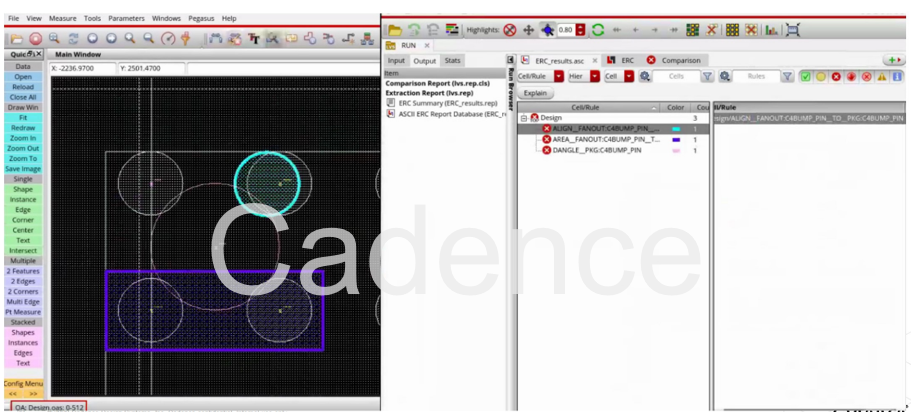

ERC / DRC Results

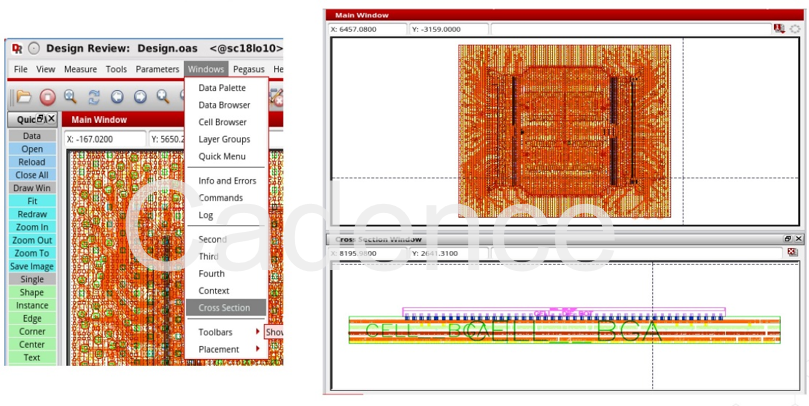

Cross-Section view

System-Stacking view

最后,让我们总结下 Pegasus System-LVS flow 的优势:

Pegasus System-LVS 紧密集成在 Integrity 3D-IC 平台中,用户可以很方便的对不同设计平台的数据进行合并和物理验证。

Pegasus System-LVS 是独立于 Foundry 的、自动化的系统级物理验证工具。它不依赖Foundry 的物理验证规则,也不需要根据不同 die 的工艺定制化物理验证规则,只需要输入相应的 GDS Layer Map 和 GDS Connection File 就可以自动生成物理验证规则完成 LVS / ERC / DRC 验证。

Pegasus System-LVS 可以生成 IDX 数据供 RC 抽取使用。

用户可以对多个堆叠层接触面或者堆叠层同时进行 LVS / ERC / DRC 验证。

用户也可以根据不同设计阶段的需要,选择性的检查某些项目,比如只检查某两个堆叠层接触面的 Pin 连接性,或者整个设计的 LVS / ERC / DRC。

Pegasus System-LVS 也支持输入晶圆厂的物理验证规则进行 LVS / ERC / DRC 验证。

希望 Integrity 3D-IC 平台能够方便越来越多工程师的系统设计,加速优秀的芯片产品落地,推动后摩尔时代的发展。

注册成功且通过 Cadence 审核的用户可获得完整版 PPT 资料。审核通过后 Cadence 会将 PPT 发送至您的邮箱,提供您的公司邮箱地址通过审核的几率更大哦!

Integrity 3D-IC 资料包:

- Cadence Integrity3D-IC 平台 产品手册

- Cadence Pegasus 3D-IC LVS / ERC / DRC PPT 介绍

Integrity 3D-IC 介绍:

Cadence Integrity 3D-IC 平台提供了一个高效的解决方案,用于部署 3D 设计和分析流程,以实现强大的硅堆叠设计。该平台是 Cadence 数字和签核产品组合的一部分,支持 Cadence 公司的智能系统设计战略(Intelligent System Design),旨在实现系统驱动的卓越 SoC 芯片设计。

关于 Cadence

Cadence 在计算软件领域拥有超过 30 年的专业经验,是电子系统设计产业的关键领导者。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计从概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续八年名列美国财富杂志评选的 100 家最适合工作的公司。

审核编辑:汤梓红

-

原理图

+关注

关注

1297文章

6339浏览量

233852 -

IC

+关注

关注

36文章

5945浏览量

175513 -

3D

+关注

关注

9文章

2875浏览量

107492 -

IC设计

+关注

关注

38文章

1295浏览量

103924 -

Cadence

+关注

关注

65文章

921浏览量

142091

原文标题:3D-IC 设计之系统级版图原理图一致性检查

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

对申请CCC认证的产品进行一致性检查时检查什么?

MIPI一致性测试

Cadence 凭借突破性的 Integrity 3D-IC 平台加速系统创新

模拟版图设计流程相关资料分享

顺序一致性和TSO一致性分别是什么?SC和TSO到底哪个好?

一致性规划研究

汽车产品认证中的一致性检查

RFID协议一致性测试系统设计(二)

加速器一致性接口

DSA系统的全局一致性需求分析

哈希图一致性算法已被验证为异步拜占庭容错

自主驾驶系统将使用缓存一致性互连IP和非一致性互连IP

RTL与网表的一致性检查

DDR一致性测试的操作步骤

深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别

3D-IC设计之系统级版图原理图一致性检查

3D-IC设计之系统级版图原理图一致性检查

评论