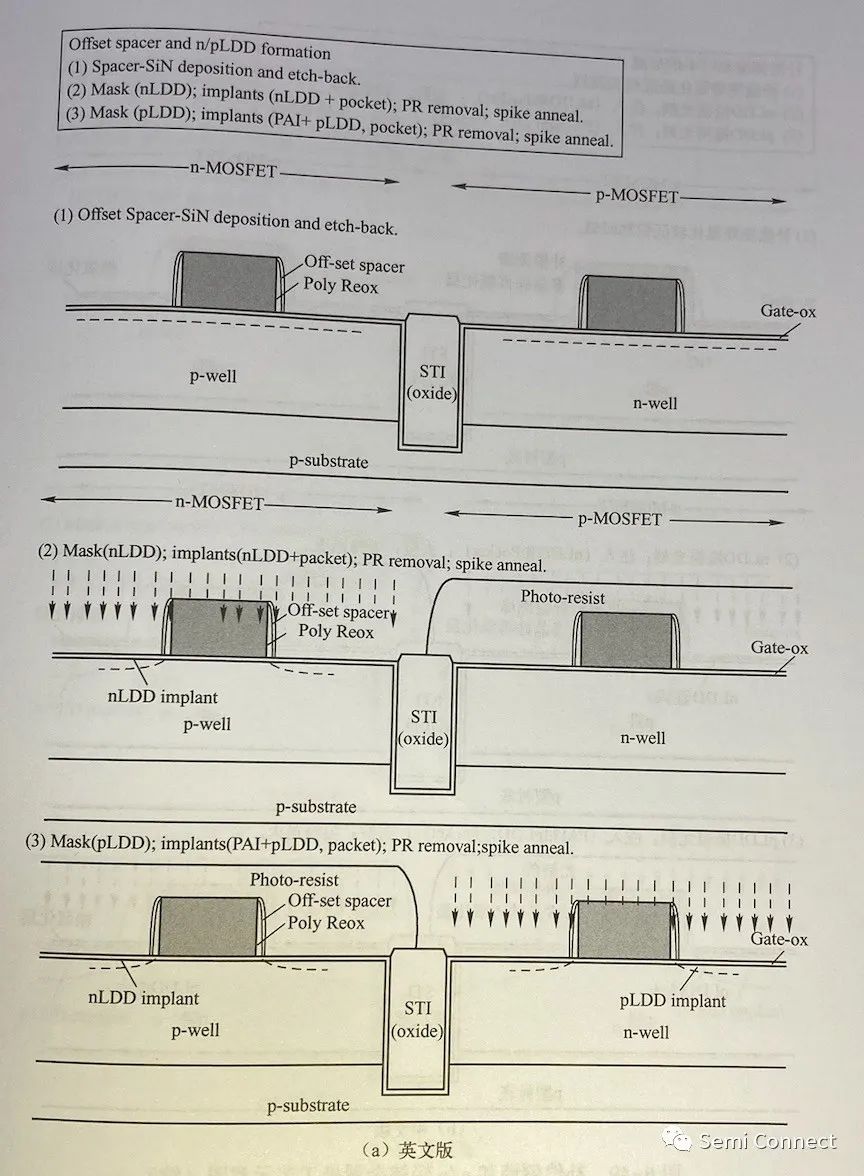

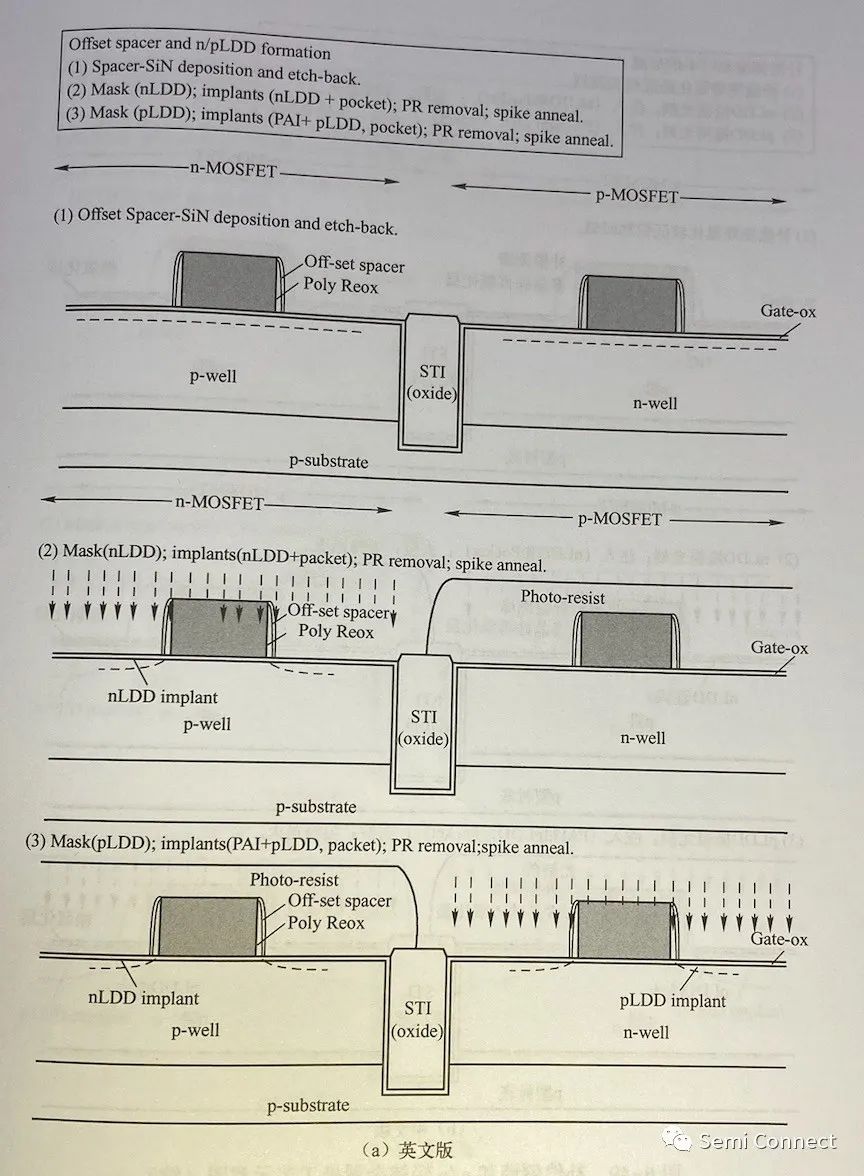

补偿侧墙 (Offset Spacer)和n/p 轻摻杂漏极 (n/ pLDD)工艺

补偿侧墙和 n/p 轻摻杂漏极工艺示意图如图所示。

首先沉积一薄层氮化硅或氮氧化硅(通常约2nm),然后进行回刻蚀(etch-Back),在栅的侧壁上形成一个薄层侧墙(Spacer)。在补偿侧墙刻蚀后,剩下的氧化层厚度约为 2nm。 在硅表面保留的这一层氧化层,在后续每步工艺中将发挥重要的保护作用。补偿侧墙用于隔开和补偿由于 LDD 离子注入(为了减弱短沟道效应)引起的横向扩散,对于 45nm/28nm 或更先进的节点,这一步是必要的。 然后分别对n-MOS和 p-MOS 进行轻掺杂漏极(LDD)离子注入。完成离子注入后,用尖峰退火(Spike Anneal)技术去除缺陷并激活 LDD 注入的杂质。nLDD 和pLDD离子注入的顺序、能量、剂量,以及尖峰退火或 RTA 的温度,对晶体管的性能都有重要的影响。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:前段集成工艺(FEOL)-4

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

相关推荐

本文介绍了集成电路制造工艺中的伪栅去除技术,分别讨论了高介电常数栅极工艺、先栅极工艺和后栅极工艺对比,并详解了伪栅去除

![的头像]() 发表于

发表于 02-20 10:16

•256次阅读

本文主要简单介绍探讨接触孔工艺制造流程。以55nm接触控工艺为切入点进行简单介绍。 在集成电路制造领域,工艺流程主要涵盖前段

![的头像]() 发表于

发表于 02-17 09:43

•219次阅读

本文介绍了集成电路工艺中的金属。 集成电路工艺中的金属 概述 在芯片制造领域,金属化这一关键环节指的是在芯片表面覆盖一层金属。除了部分起到辅助作用的阻挡层和种子层金属之外,在

![的头像]() 发表于

发表于 02-12 09:31

•360次阅读

Gate,简称HKMG)工艺。HKMG工艺作为现代集成电路制造中的关键技术之一,对提升芯片性能、降低功耗具有重要意义。本文将详细介绍HKMG工艺的基本原理、分类

![的头像]() 发表于

发表于 01-22 12:57

•503次阅读

芯片制造可分为前段(FEOL)晶体管制造和后段(BEOL)金属互连制造。后段工艺是制备导线将前段制造出的各个元器件串连起来连接各晶体管,并分配时钟和其他信号,也为各种电子系统组件提供电

![的头像]() 发表于

发表于 12-04 14:10

•3062次阅读

IMD4 工艺是形成 TMV (Top Metal VIA,顶层金属通孔)的介质隔离材料,同时IMD4 会隔离第三层金属和顶层 AL金属。IMD4 的材料也是 USG 和SiON材料。

![的头像]() 发表于

发表于 11-25 15:49

•445次阅读

共读好书欢迎扫码添加小编微信扫码加入知识星球,领取公众号资料

原文标题:集成电路封装基板工艺详解(68

![的头像]() 发表于

发表于 11-01 11:08

•435次阅读

随着信息技术的飞速发展,芯片作为现代电子设备的核心部件,其重要性日益凸显。而芯片封装工艺集成工程师作为芯片制造过程中的关键角色,需要掌握一系列复杂的课程知识,以确保芯片的性能、稳定性和可靠性。本文将从多个方面详细阐述芯片封装工艺

![的头像]() 发表于

发表于 10-24 10:09

•524次阅读

近日,晶合集成在新工艺研发领域取得了重要突破。在2024年第三季度,晶合集成成功通过了28纳米逻辑芯片的功能性验证,并顺利点亮了TV,标志着其28纳米制程技术又迈出了坚实的一步。

![的头像]() 发表于

发表于 10-10 17:10

•665次阅读

集成电路(IC)作为现代电子技术的核心,其制造工艺的复杂性和先进性直接决定了电子产品的性能和质量。对于有志于进入集成电路行业的学习者来说,掌握一系列基础知识是至关重要的。本文将从半导体物理与器件

![的头像]() 发表于

发表于 09-20 13:46

•1057次阅读

集成电路(IC)是现代电子设备中不可或缺的组件,它将成千上万的晶体管、电阻、电容等元件集成在一块微小的硅片上,实现了复杂电路功能的高度集成化。集成电路的制造涉及到多种精密

![的头像]() 发表于

发表于 04-10 13:40

•7830次阅读

锗(Ge)探测器是硅基光电子芯片中实现光电信号转化的核心器件。在硅基光电子芯片工艺中实现异质单片集成高性能Ge探测器工艺,是光模块等硅基光电子产品实现小体积、低成本和易制造的优先选择。

![的头像]() 发表于

发表于 04-07 09:16

•1263次阅读

此节以半导体的代表,CMOS-半导体为例,对前段制程FEOL进行详细说明。此说明将依照FEOL主要制程的剖面构造模型,说明非常详细,但一开始先掌握大概即可。

![的头像]() 发表于

发表于 04-03 11:40

•1415次阅读

前段制程包括:形成绝缘层、导体层、半导体层等的“成膜”;以及在薄膜表面涂布光阻(感光性树脂),并利用相片黄光微影技术长出图案的“黄光微影”。

![的头像]() 发表于

发表于 04-02 11:16

•5735次阅读

电子发烧友网站提供《东芝BiCD工艺集成电路硅单片TB67H450AFNG数据手册.pdf》资料免费下载

发表于 03-20 11:23

•1次下载

前段集成工艺(FEOL)-4

前段集成工艺(FEOL)-4

评论