应用材料公司今天举办了在线逻辑大师班,展示了几种材料工程解决方案,这些解决方案通过持续改进功率、性能、面积、成本和上市时间(PPACt)实现高级逻辑扩展。

正如我的同事在最近的博客中概述的那样,在将晶体管和互连扩展到3nm节点及更高节点时,多重挑战阻碍了功耗和性能的提高。还存在模式可变性问题,需要新的材料工程解决方案。在这篇博客中,我将重点介绍应用材料公司如何通过基于工艺步骤协同优化和集成材料解决方案(IMS)的创新,帮助客户实现先进逻辑的PPACt路线图。我们还在帮助业界实施一种称为设计技术协同优化(DTCO)的扩展技术,该技术将在新兴节点中变得越来越普遍,因为它使逻辑密度扩展能够继续进行,即使音高扩展速度变慢。

晶体管缩放:将FinFET扩展到5nm以上;启用门全方位拐点

FinFET路线图有三个重要的技术挑战:翅片弯曲、高k金属栅极(HKMG)和接口关键尺寸缩放以及源极/漏极电阻。应用材料公司正在使用新材料和工艺协同优化的组合来帮助解决每个问题。

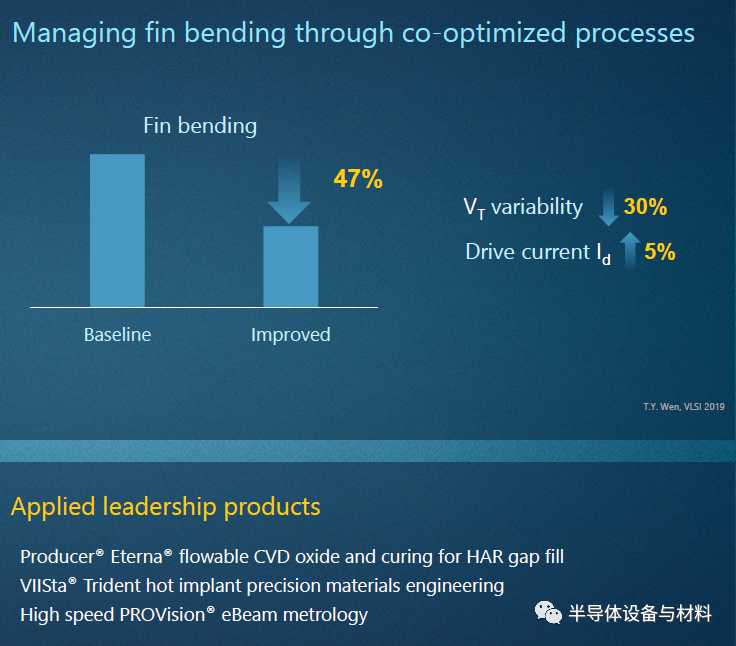

制造过程中的翅片弯曲会导致可变性,从而降低性能并降低电源效率。为了缓解这种情况,我们开发了协同优化的材料工程解决方案,包括用于翅片隔离的可流动氧化物,以及共同优化的离子注入和退火步骤,所有这些都使用应用材料公司的PROVision eBeam测量和检测技术进行监控。使用这些技术,我们可以实现高、直、高长宽比的翅片,具有更高的均匀性,从而将阈值电压变化率降低30%,并将驱动电流增加5%以上(见图1)。

图 1:应用材料公司共同优化的工艺可减少翅片弯曲,从而将阈值电压变异性降低 30%,驱动电流增加 5% 以上。

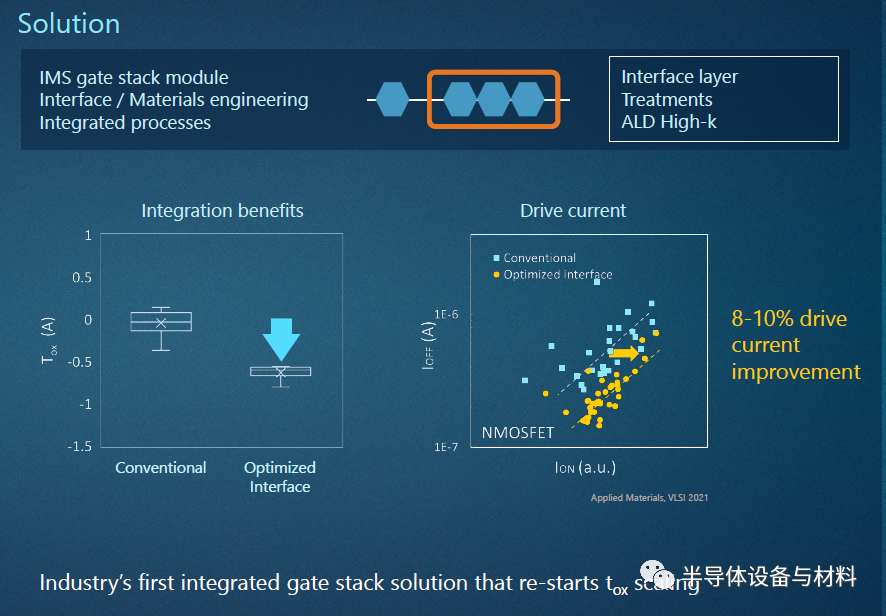

两个HKMG逻辑元件——接口和高k值层——是提高晶体管驱动电流的关键。但是,自14nm节点以来,这两层都没有扩展,从而造成了性能瓶颈。为了解决这个问题,应用材料公司开发了一种新的集成材料解决方案(IMS),该解决方案结合了真空中的关键工艺步骤,以实现更高程度的界面工程和调整。使用IMS,我们展示了一种新的集成栅极堆栈,该堆栈使等效氧化物厚度缩放能够恢复,并将驱动电流提高8%至10%(见图2)。

图 2:使用集成材料解决方案,应用材料公司展示了一种新的集成栅极堆栈,该堆栈可恢复等效氧化物厚度缩放,并将驱动电流提高 8% 至 10%。

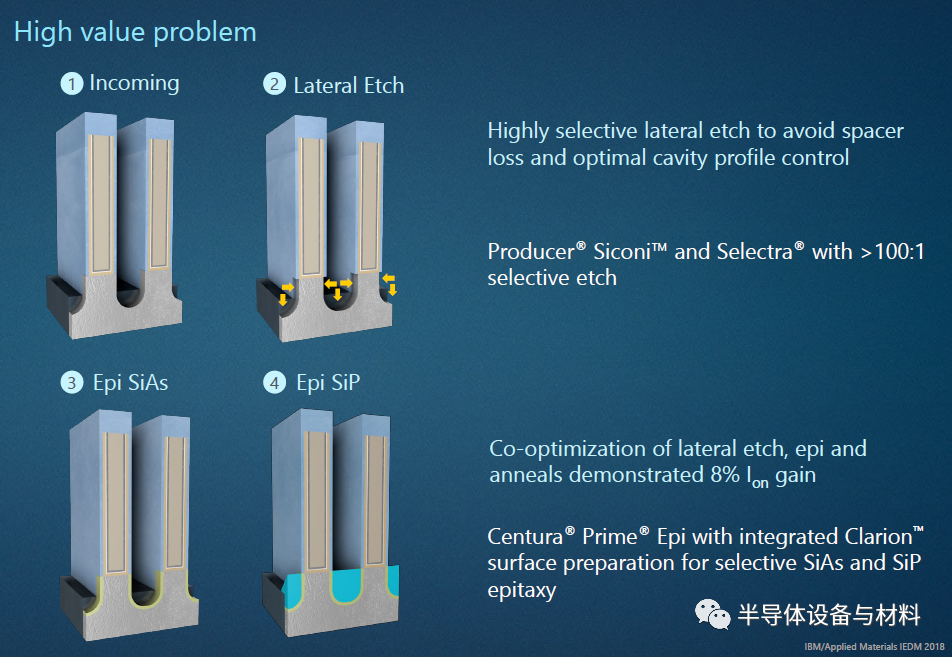

在晶体管的源极/漏极电阻模块中,缩放使每个节点的接触面积减少了25%,导致接触电阻不可持续地增加。为了解决这个问题,应用材料公司开发了一种新的协同优化工艺技术,可以最大限度地利用可用于应变工程的区域(见图3)。该解决方案包括横向蚀刻,使嵌入式源极-漏极应力源更靠近通道。此外,我们还开发了一种新型选择性砷化硅(SiAs)外延层。新的材料和材料工程技术降低了电阻,并将驱动电流提高了8%。

图 3:应用材料公司的源极/漏极电阻解决方案包括共同优化的蚀刻、外延和退火,驱动电流增益为 8%。

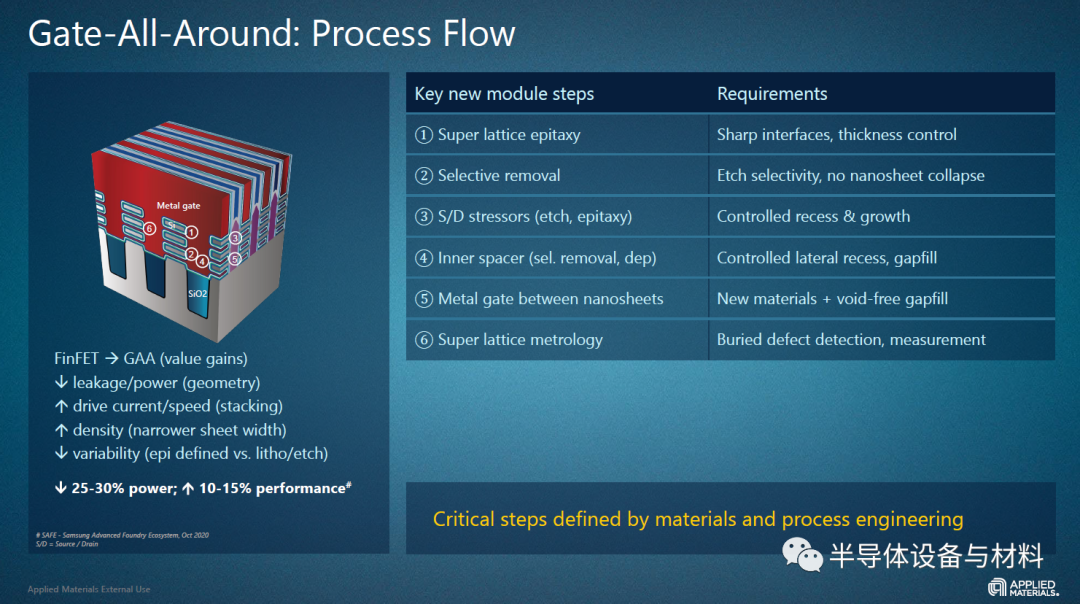

随着行业从 FinFET 过渡到栅极全能 (GAA) 晶体管架构,进一步提高性能和功耗,材料工程创新将变得更加重要(见图 4)。在GAA中,晶体管通道方向从垂直转向水平,栅极在所有四个侧面而不是三个侧面围绕通道。控制通道厚度对于性能和功耗至关重要:在从 FinFET 到 GAA 的过程中,通道厚度控制从高而薄的翅片的光刻和蚀刻转向 GAA 中的外延和选择性去除,因为它们提供了高度可控的增长和减少的可变性。GAA晶体管还需要通道之间的内部垫片,适当的工程设计有助于降低电容。垫片采用高度可控的选择性蚀刻和间隙填充工艺制成。使用 eBeam 进行计量有助于确保新结构正确、最佳地形成,从而实现 10% 至 15% 的预期性能提升和 25% 至 30% 的功率提升。

Epi、选择性去除和电子束计量是应用材料公司的领导领域,我们已经在开发协同优化的工艺,以帮助加速为客户提供 GAA 解决方案。因此,与FinFET相比,我们预计GAA中每10万WSPM(每月晶圆启动)将获得10亿美元的增量收入。

图 4:随着行业向栅极全能 (GAA) 晶体管架构过渡,材料工程创新将变得更加重要。

互连扩展:新的集成材料解决方案将过孔阻力降低 50%

互连器件消耗近三分之一的功率,占电阻电容(RC)延迟的70%以上。与每个工艺节点收缩而性能提高的晶体管不同,互连线在收缩时会遇到更高的电阻,这反过来又降低了性能并增加了功耗。如果没有突破,通过电阻的互连将从7nm到3nm节点增加10倍,从而抵消了晶体管缩放的好处。

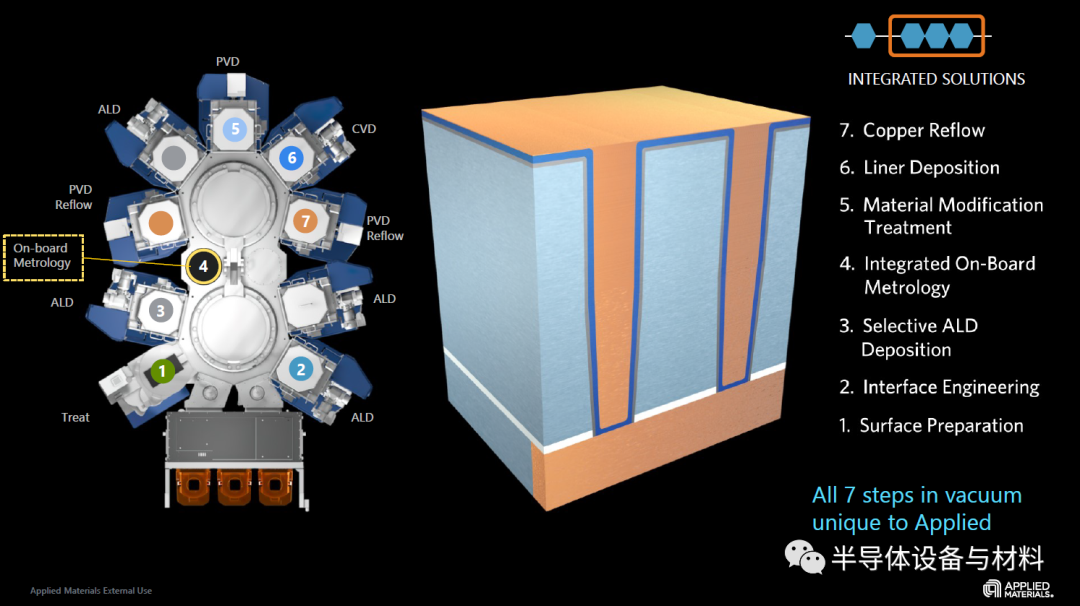

为了解决这一挑战,应用材料公司今天推出了一项材料工程方面的突破,称为Endura铜阻隔种子IMS。这款卓越的集成材料解决方案在高真空下将七种不同的工艺技术结合在一个系统中:ALD、PVD、CVD、铜回流焊、表面处理、界面工程和计量(见图5)。该解决方案通过将保形原子层沉积替换为选择性原子层沉积,消除了过孔接口处的高电阻率势垒。它还包括铜回流焊技术,可在狭窄的特征中实现无空隙填充。该解决方案将过孔触点接口处的电阻降低了多达 50%,从而提高了芯片性能和功耗。

图 5:新型 Endura 铜阻隔种子 IMS 在高真空下将七种不同的工艺技术结合在一个系统中,以提高芯片性能和功耗。

通过材料工程和 DTCO 的创新解决模式变异性问题

由于EUV光刻技术与多图案技术结合使用以创建更细的线条,因此在较小的节点上,图案可变性的问题变得越来越成问题。我们想要的不是笔直、光滑的边缘,而是越来越粗糙和不均匀。在过去,这并不是一个大问题,因为特征要大得多,边缘粗糙度的比例更小。但是,随着我们继续使用EUV进行扩展,特征和边缘粗糙度变得相当,从而导致随机缺陷,例如开路和短路。

在多图案化中,该行业通常使用旋入式电介质和炉子步骤将光刻图案转移到器件层中。为了减少随机误差,我们正在用高质量的CVD材料替换旋装电介质,该材料与我们的Sym3蚀刻系统共同优化,该过程由我们的PROVision eBeam测量系统监控。事实上,我们将CVD集成到我们的蚀刻室中。一旦具有粗糙特征的晶圆进入腔室,我们就会选择性地沉积一层薄薄的CVD材料,调整工艺,在宽开口上沉积更多材料,在小开口上沉积更少的材料,从而校正相邻线之间的距离。

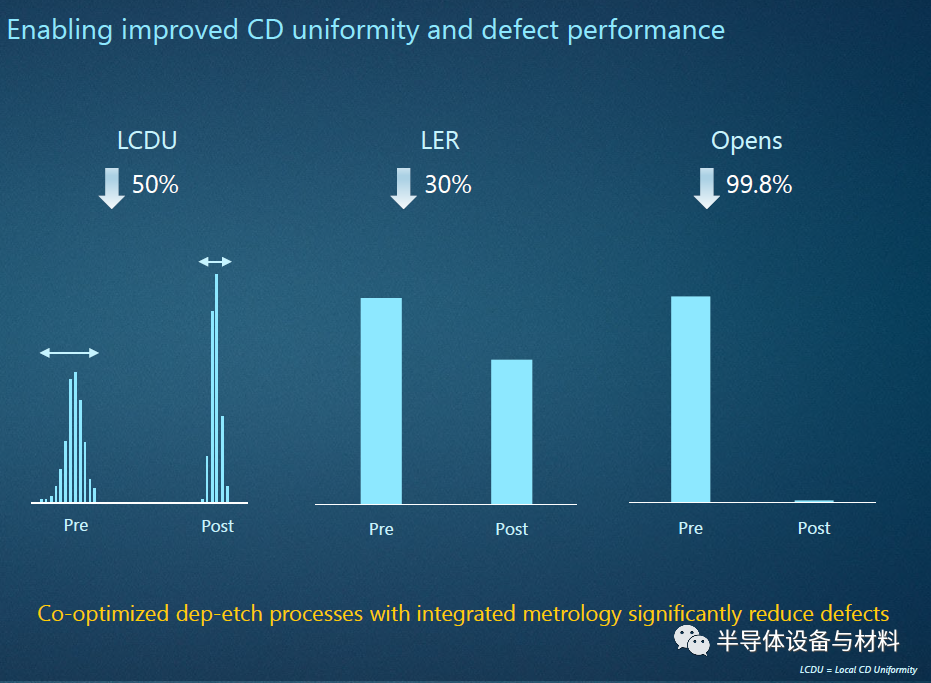

沉积后,我们使用经过特殊调整的蚀刻模式,该模式蚀刻小特征的速度快于大特征,再次减少了差异。因此,通过将CVD与我们先进的蚀刻技术共同优化,我们可以平滑线条并消除许多随机缺陷。我们还使用电子束测量技术来快速测量这些微小特征的尺寸变化。事实证明,这种协同优化的解决方案可以使特征尺寸的局部变化减少50%,线路边缘粗糙度降低30%,开路缺陷减少近100%,从而实现持续的逻辑缩放和健康的器件良率(见图6)。

图 6:应用材料公司 CVD 与先进蚀刻技术的共同优化消除了许多随机缺陷,从而显著降低了局部临界尺寸均匀性 (LCDU)、线边粗糙度 (LER) 和开路缺陷。

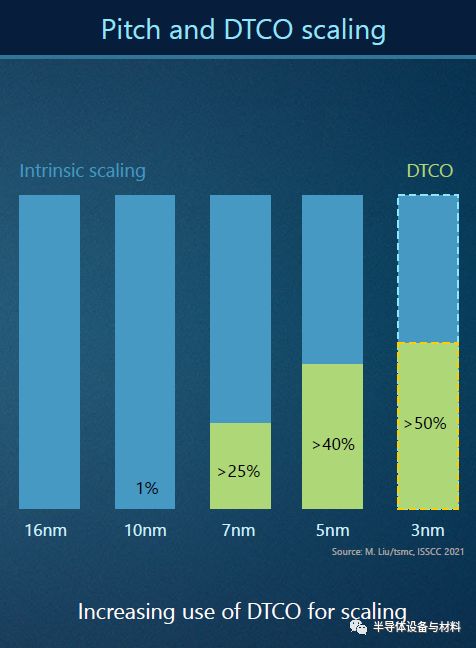

逻辑路线图依赖于持续的逻辑密度改进来降低面积成本。但2D收缩正在放缓并变得更加困难。可用于继续将栅极和电线拉得更近的物理空间越来越少,而且它们越接近,电气挑战就越严重。几十年来,传统的摩尔定律2D缩放(又名音高缩放或固有缩放)为该行业提供了非常好的服务。然而,展望未来,DTCO将越来越多地补充音高缩放,DTCO代表设计技术协同优化(见图7)。DTCO 允许逻辑设计人员使用巧妙的 2D 和 3D 设计技术来增加相同间距下的逻辑密度。基于DTCO的一个关键变化是带有背面供电网络的埋地电源轨。这种新架构将厚电源线从硅晶圆的背面或晶体管下方路由到晶体管单元,允许进一步的2D缩放,同时降低电压损耗。应用材料公司凭借在金属、隔离电介质、蚀刻和 CMP 工艺方面的专业知识,帮助实现此技术和其他 DTCO 技术。

图 7:设计技术协同优化 (DTCO) 预计将在未来节点中提供越来越大比例的整体扩展优势。

结束语

应用材料公司的目标是成为我们客户的 PPACt 支持公司,今天的大师班说明了材料工程对未来逻辑缩放的重要性。几十年来,逻辑路线图是由传统的摩尔定律2D缩放驱动的。然而,随着这种方法的好处放缓,业界正在通过基于材料工程的技术组合来补充它,以实现扩展到3nm节点甚至更远的地方。客户正在采用"PPACt的新剧本",这为应用材料公司创造了巨大的增长机会。随着逻辑从5nm过渡到3nm,应用材料公司预计其服务市场将增长25-30%。

审核编辑 :李倩

-

电压

+关注

关注

45文章

5642浏览量

116382 -

晶体管

+关注

关注

77文章

9801浏览量

139081 -

回流焊

+关注

关注

14文章

480浏览量

16896

原文标题:AMAT:材料工程

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶体管故障诊断与维修技巧 晶体管在数字电路中的作用

晶体管与场效应管的区别 晶体管的封装类型及其特点

全方位解剖MOS管

通过应用频率将TPS92210的调光范围扩展到通用AC范围

晶体管的基本工作模式

NMOS晶体管和PMOS晶体管的区别

晶体管处于放大状态的条件是什么

消息称台积电3nm/5nm将涨价,终端产品或受影响

晶体管放大时,各级电位状态是什么

什么是达林顿晶体管?达林顿晶体管的基本电路

晶体管缩放:将FinFET扩展到5nm以上;启用门全方位拐点

晶体管缩放:将FinFET扩展到5nm以上;启用门全方位拐点

评论