一、什么是多周期路径约束?

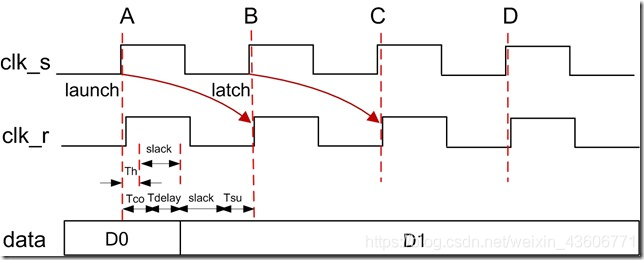

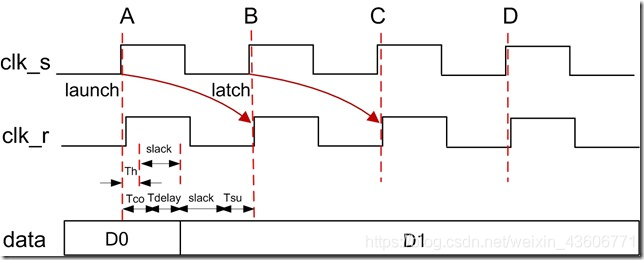

不管是quartus中还是在Vivado中,默认的建立时间和保持时间的检查都是单周期的,如图1所示,也就是说如果A时刻发送,B时刻捕获,这两者之间相差一个时钟周期,也就是很多文献所说的current launch和current latch,但是某些情况下,这两者之间并不一定只是一个时钟周期,比如加上一个捕获使能信号,或者跨时钟域的情况,两者时钟有相位差的情况,此时就需要设置多周期。

二、如何理解多周期路径约束?

首先要理解一个数据的发送流程,如图2所示:

这里的数据在发送以后,并不是理想状态下,瞬间达到下一个寄存器,二是包括Tskew时钟偏斜,Tdelay传输延迟,Tco源寄存器的输出延迟,Tsu和Th寄存器需要的建立保持时间等时间延迟,slack就是时间余量,理想的情况自然是slack为0,但是这是不可能达到的,因此要使得slack>0,有以下式子:

根据上式可以看出来,由于Tskew、Tco、Tdelay、Tsu、Th都是固定的,也就是跟实际硬件代码书写布局布线等相关,一旦这些都确定了,就是无法改变的,所以当在工程时序检查建立时间和保持时间出现问题,这些数据是无法改变的,只能改变 latch和 launch的沿的位置,这就是多周期路径约束的本质。

那么为什么约束形式是这样的?set_multicycle_path -from [get_clocks clk1] -to [get_clocks clk2] -setup -end 3

这是由于改变了建立时间和保持时间检查的位置,实际上就改变了 latch和 launch的沿的位置,处于人机交互的便利和理解,采取了这种语言。

三、实例讲解

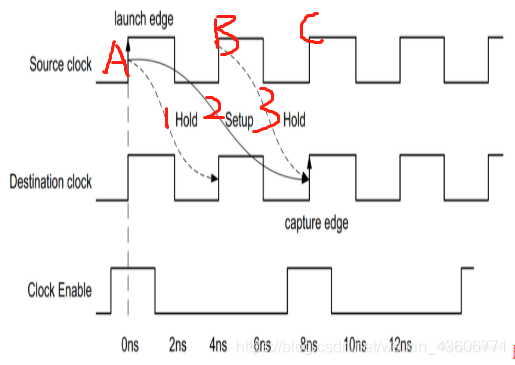

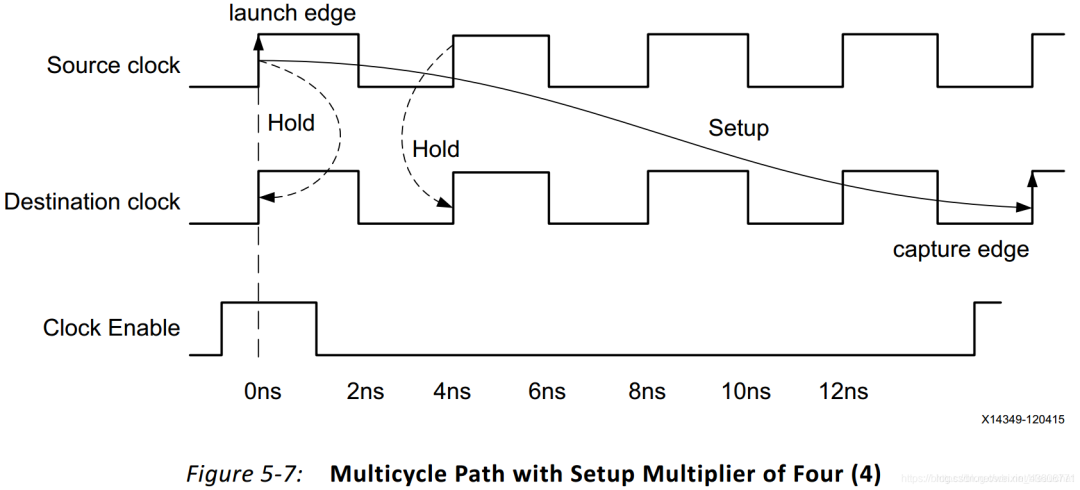

假设A时刻发送一个数据,那么默认情况下就是单周期路径,B就是捕获沿,也就是上文所提到的latch edge和 launch edge。红色箭头起点和重点也就是代表了current launch edge和current latch edge,此时,如果加入了一个使能信号,如果仍然在B时刻作为current latch edge,那么建立时间余量就会比较紧张(悲观),当然实际的不是在这里捕获的,只是时序分析工具默认是在这里的,那么往后移动一个时钟周期,current latch edge就在C时刻了,此时的检查时间就是比较充裕的。再看保持时间的检查,如果并不设置采取默认情况,那么应该是1线,B为previous latch edge时刻,也是next launch edge。

根据原则:

1)当前发起沿发送的数据不能被前一个捕捉沿捕捉。

2)下一发起沿发送的数据不能被当前捕捉沿捕捉。

显然,A时刻发送的数据也就是current launch edge时可能被B时刻捕获的,不满足第一个条件,于是需要往前调一个周期。如图4

同样的分析方法,此时的满足上述原则的。

四、总结

当时序检查报告中出现建立时间或者保持时间出现违规的情况,就需要考虑进行多周期路径约束。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:关于多周期路径约束

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22553浏览量

640500

原文标题:关于多周期路径约束

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

2026深入拆解:Gemini 3.0 镜像官网如何理解 FPGA 时序约束并自动生成 SDC 文件

SST固变的技术经济学分析与商业化部署路径

Vivado时序约束中invert参数的作用和应用场景

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

零碳园区的实施路径:从目标设定到净零落地的全周期

时钟周期、机器周期、指令周期介绍

时序约束问题的解决办法

关于综合保持时间约束不满足的问题

技术资讯 I Allegro 设计中的走线约束设计

技术资讯 I 图文详解约束管理器-差分对规则约束

关于多周期路径约束

关于多周期路径约束

评论