Verilog例化说明

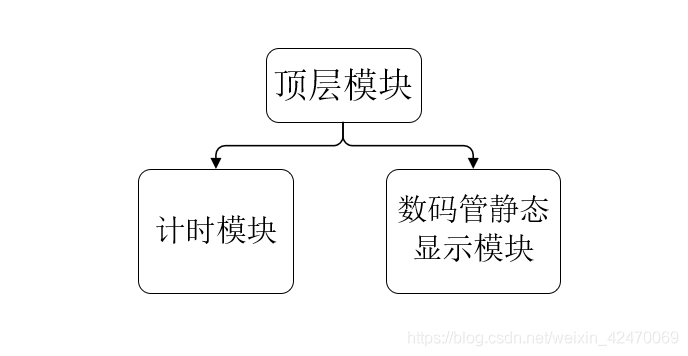

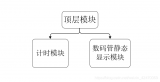

1.什么是模块例化?为什么要例化?

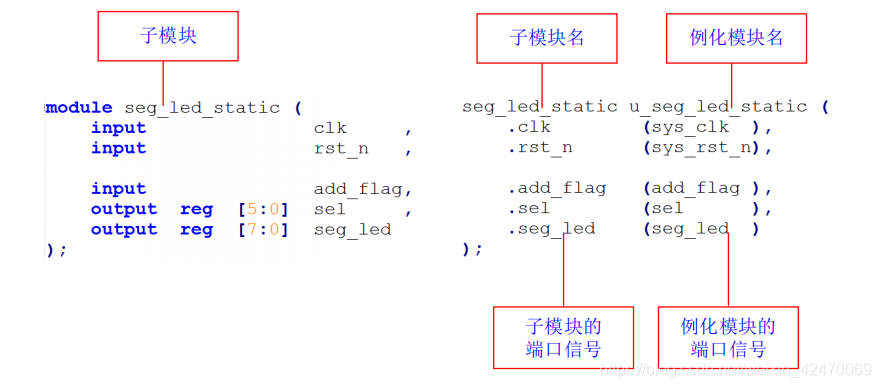

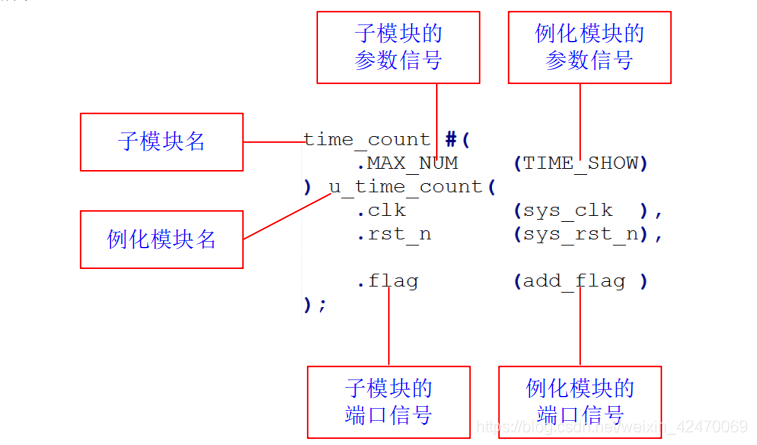

2.实例说明例化方法

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-Verilog例化说明

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1633文章

21817浏览量

607141

原文标题:FPGA学习-Verilog例化说明

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog 测试平台设计方法 Verilog FPGA开发指南

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog

Verilog与VHDL的比较 Verilog HDL编程技巧

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构

Verilog vhdl fpga

相关专业,具有良好的专业基础知识。 感兴趣可滴滴 JYHXDX534

2.工作年限不限,有工作经验或优秀应届毕业生亦可。

3.对FPGA芯片架构和资源有深入的理解,精通Verilog HDL、VHDL

发表于 11-12 16:40

FPGA加速深度学习模型的案例

FPGA(现场可编程门阵列)加速深度学习模型是当前硬件加速领域的一个热门研究方向。以下是一些FPGA加速深度学习模型的案例: 一、基于FPGA

FPGA编程语言的入门教程

FPGA(现场可编程逻辑门阵列)的编程涉及特定的硬件描述语言(HDL),其中Verilog和VHDL是最常用的两种。以下是一个FPGA编程语言(以Verilog为

FPGA Verilog HDL代码如何debug?

,共同进步。

欢迎加入FPGA技术微信交流群14群!

交流问题(一)

Q:Verilog代码如何debug?最近学习fpga,写了不少verilog

发表于 09-24 19:16

【招聘】verilog vhdl FPGA

1.熟悉FPGA架构及应用,熟悉图像算法的FPGA实现。

2.熟悉verilog vhdl,熟悉Xilinx或Intel等开发工具。

3.有AI算法 fpga实现经验优先。

4.本科及

发表于 09-02 15:50

求助各位关于Verilog当中模块例化、端口与引脚 的问题

初学者。我在刷HDLbits的时候做到了这道题

答案:

答案给的是定义了wire型的信号,并借这个来进行端口连接。而我的疑问在于:

1.模块例化时,如果采用按名字的方式进行例化,那么:点号后面写

发表于 07-15 20:38

FPGA基础知识学习

语言(HDL)如VHDL或Verilog来描述。这些描述定义了电路的功能和信号流,然后通过各种电子设计自动化(EDA)工具进行辅助设计、综合化、布局和布线等处理,最终将设计转化为可以在FPGA

发表于 04-29 23:26

如何快速入门FPGA

时钟管理模块、嵌入式块RAM、布线资源等。

学习FPGA编程语言:

掌握Verilog HDL(硬件描述语言)。Verilog用于数字电路的系统设计,具有简洁的语法和清晰的仿真语义,非

发表于 04-28 09:06

FPGA学习资料分享

的学习资源Verilog 教程,数字逻辑设计 (点击文字进入链接).

具备一定硬件描述语言基础是发开FPGA通用的。此外就是根据厂家型号、环境和提供的资源,能有效使用组织起来,实现目标功能,这更倾向于实践应用。 大家有关于实践应

发表于 03-31 13:23

fpga是用c语言还是verilog

FPGA(现场可编程逻辑门阵列)开发主要使用的编程语言是硬件描述语言(HDL),其中Verilog是最常用的编程语言之一。而C语言通常用于传统的软件编程,与FPGA的硬件编程有所区别。

fpga是什么专业学的

FPGA(现场可编程门阵列)的学习涉及多个专业领域,但主要与电子信息类、自动化类、计算机类等相关专业最为紧密。这些专业通常涵盖数字电路设计、硬件描述语言(如Verilog和VHDL)编

FPGA学习-Verilog例化说明

FPGA学习-Verilog例化说明

评论