USB是比较通用的,这里就写USB2.0和3.0的通用设计规则,以及几个实际中的注意事项。

一.电路设计

1.由于USB是外部接口,考虑到用户使用的各种复杂条件,防止有短路的情况影响到板卡自身的电源,所以需要设计限流IC。

这里使用的限流IC还是比较简单的,首先根据负载确定限流IC芯片,USB2.0跟USB3.0跑的最大电流不一样,限流的大小也不一样,需要注意。

笔者以前做设计用过另外一种限流IC,保护时能输出状态IO,这个信号可以连接到板卡的SOC,或者MCU等,以进行状态检测。

2.电容

因为USB设备拔插的时候,电压会波动,尤其是插入的时候,需要较大的电流,需要在接口附近使用较大的电容,防止电压被拉低。为了电源的干净,也可以增加两枚小电容。

3. 信号线。USB信号走的是差分信号,为了保护,需要在链路上增加TVS管,理论上每个元器件都有一定的容性,所以选用TVS管的时候,尽量选择容性负载小一些的,对信号影响最小。保护电压不必太大,考虑USB差分信号幅值大小来选型即可。考虑到PCB走线阻抗的连续性,TVS管在板卡的位置,距离USB座子不宜太远也不宜太近。太远不利于TVS,太近则会导致阻抗跌落。

二. USB2.0

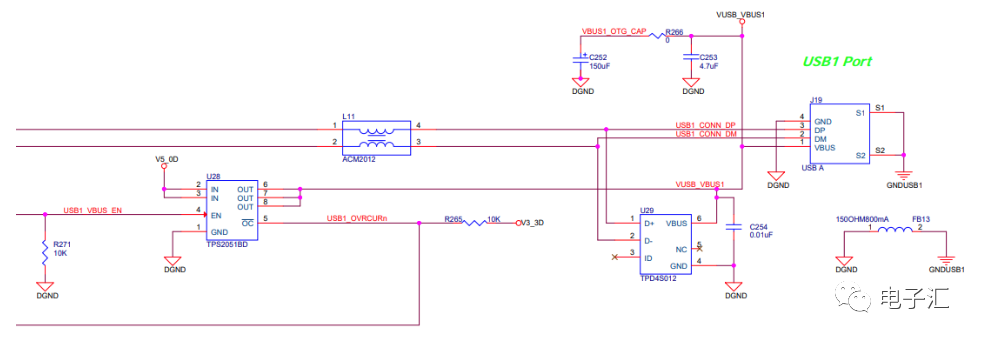

以下为USB电路设计;

1)U28是过流保护器件,USB协议中规定USB端口供电5V,电流500mA,超过该值要能实现关断输出,另外在负载短路时也能实现关断,所以使用该器件,该器件叫做负载开关芯片。

2)L11是共模电感,共模电流会导致EMC测试中的辐射测试超标,差分信号不平衡将会导致该情况发生,所以增加共模电感,来减小/阻碍共模电流。实际产品设计中,这个共模电感可以和两颗0402的电阻做共-lay,然后根据实际测试的数据决定电感要不要上件。如果贴电阻的情况下,EMC的表现也很好,那么就不贴共模电感,只贴电阻就可以了,毕竟一个共模电感可以买好多个电阻了,成本差异很明显。

3)U29是静电防护器件,因为USB端口我们会使用手插入USB设备,可能导致电源、数据线上有静电放电,用该器件来保护CPU端口。一般这个静电防护器件要注意结电容,结电容和信号速率相关。USB信号上通常用的ESD器件的结电容在几pF左右。同时,在PCB上,这个ESD器件不要有分叉走线,最好把ESD器件的焊盘直接放在USB信号线上。

4)Vbus上的电容,这是因为USB设备插入时瞬间电流较大,则可能导致Vbus电压下降,此时需要满足标准规定,所以增加电容来稳定电压。

5)FB13是信号地和外壳屏蔽地之间的隔离磁珠,磁珠是耗能原件,来消耗掉不需要的干扰高频信号,直流下基本上没作用。

6)J19是USB端子,可能是电脑那种的USB母头,也可能是手机上的Micro USB接口。

7)在USB靠近端子侧放置电阻是静电防护作用,因为有时候静电防护器件还没起作用,就要靠这个电阻起作用了。

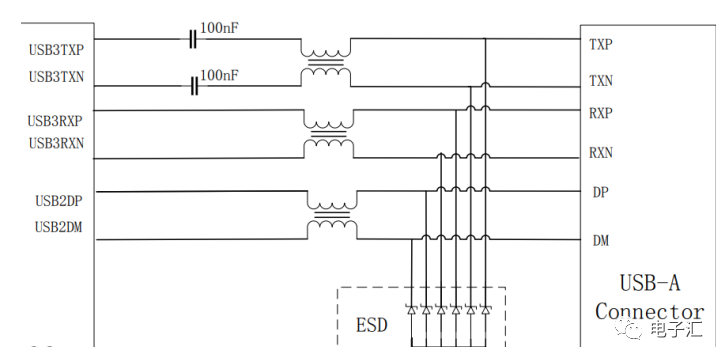

三. USB3.0

USB3.0相比2.0在硬件物理连接上有较大的改变,采用的是RX/TX全双工链路设计,由2对差分信号组成,同时向下兼容USB2.0,所以整个接口有3对差分信号,分别为USB3_RXM/USB3_RXP,USB3_TXM/USB3_TXP,USB2_DM/USB2_DP,USB3.0的传输速率可达到5Gbps,相比USB2.0 480Mbps有比较大的提供。

硬件原理设计

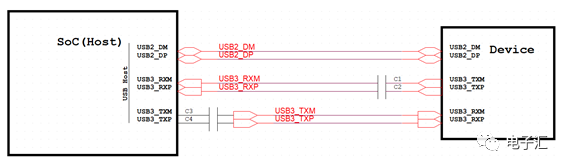

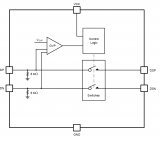

如下图,为USB3.0的Data数据连接原理图,从电路上可以看是USB2.0为半双工,数据收发在一对差分信号上传输。USB3.0为全双工,收发信号为独立的传输路径;其次,由于Sink端的直流偏置电压和source端的直流偏置电压不一样,故要需要串入AC耦合电容,电容一般取100nF,一般靠近驱动端放置,电容在设计上要求ESR ESL(特别重要)尽量小。

USB 3.0的Host的RX连接到Device Tx,Host的Tx连接到Device的 Rx,类似于我们常用的UART接口的连接。

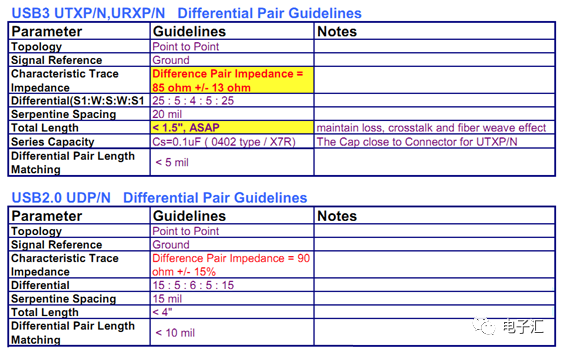

PCB Layout设计

硬件连接上相对比较简单,最终需要PCB Layout设计来保证信号的完整性,接下来从PCB层叠结构、阻抗控制、走线要求等细节上说明USB3.0的设计的注意事项。

阻抗控制:90Ω差分阻抗±10%

AC耦合电容:100nF

USB2.0: 5V,500mA

USB3.0: 5V,1A

1. PCB层叠结构要求

以下是4层板的层叠结构图,可通过Si9000计算出差分对所约束的线宽线距。

对于PCB阻抗线的定义,受那些物理参数影响,请自行查阅相关

2. USB差分阻抗控制要求

参考USB PHY手册,基于上图的层叠结构,计算出差分信号所要求的线宽线距,本文为ASM1153 为例进行阐述:

ASM1153为USB 3.0转Sata接口的桥芯片,要求USB 3.0的差分阻抗为85欧,USB2.0为90欧,差分对等长公差在+/-5mil。

3. PCB走线要求

5Gbps的速率需要以高速线的设计规则来严格把关走线,充分考虑PCB的设计细节

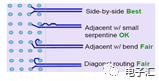

3.1 PCB出线要求尽可能平等出差,具体走线参考下图:

3.2 走线换层需要在信号过孔旁边增加地过孔,用于信号的回流(高速通用规则)

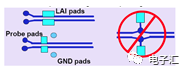

3.3 USB信号测试点的放置建议如下图,“一”字形放置在路径上,非Y字形或T字形放置,并且测试焊盘如果走线不连续的较大焊盘,请将相邻层的GND层垂直于测试焊盘掏空,避免出现影响信号的寄生电容或等效电容。测试点的焊盘尺寸,应尽可能的小,如果必需要放置测试点的话,比照0402封装的焊盘尺寸或直接将测试点放置在信号线的过孔上。

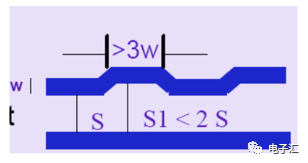

3.4 关于等长匹配蛇形线的走线方式,建议按下图方式走线

3.5 USB3.0 的P/M如果走线上有交差,可以将差分对的P/M交换,USB3允许P/M反转

四. 注意事项

USB2.0信号线换层次数。

一般是要求换层2次,即从SoC扇出换层一次,到Device端或者连接器端换层一次。十几种换3~4次也没有问题,但最好每次换层都伴随GND过孔,每个信号线一个,空间受限的话也可以两个信号先共用一个。

USB3.0信号

USB3.0速率更高,这方面的要求会更严格一点。在实际项目中,也可以参考2.0的信号处理。

如果是核心板和底板的方式,那么用非高速的普通连接器问题也不大。

审核编辑:郭婷

-

芯片

+关注

关注

463文章

54593浏览量

470595 -

接口

+关注

关注

33文章

9630浏览量

157762 -

usb

+关注

关注

60文章

8486浏览量

286471

原文标题:USB设计简介

文章出处:【微信号:电子汇,微信公众号:电子汇】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

瑞芯微(EASY EAI)RV1126B USB3.0 Host电路

湖南静芯推出USB 3.0的ESD EOS防护完整解决方案

探索FSUSB40:低功耗高速USB2.0开关的卓越之选

帝奥微发布USB2.0接口OVP过压保护开关芯片DIO5010

TUSB1210 USB2.0 收发器芯片:设计应用与技术详解

驱动板PCB布线的注意事项

电流功率检测USB3.0HUB,USB3.0扩展坞,可扩展的USB2.0

双USB2.0接口静电保护

USB2.0和3.0的通用设计规则和注意事项

USB2.0和3.0的通用设计规则和注意事项

评论