在数字IC设计面试中经常会被要求画出某一个逻辑表达式的管级电路,本文将基于逻辑门的构成解释如何完成任意逻辑的管级电路设计。

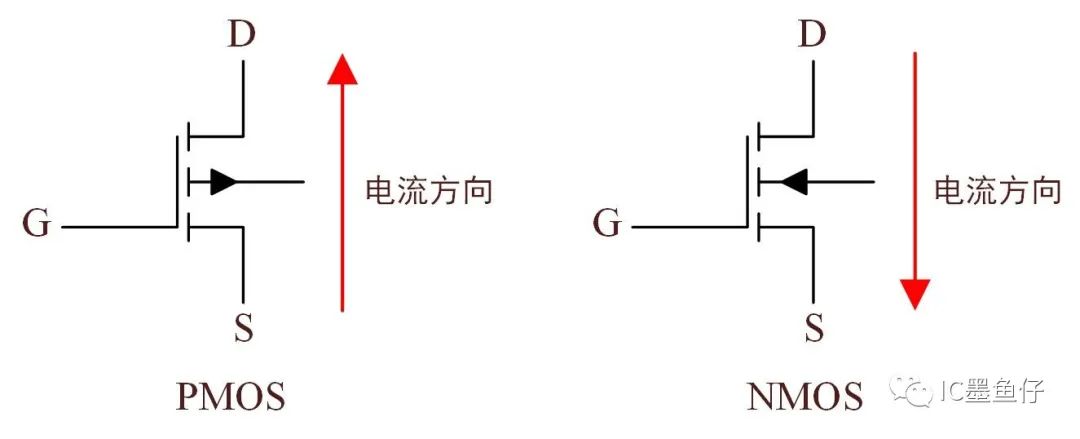

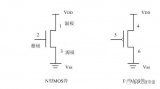

PMOS & NMOS

要想轻松画出管级电路,首先要理解,为什么在逻辑门中PMOS总是作为上管,NMOS总是作为下管。

对于P管来说,电流从S流向D,其导通条件为VSG>VTH(阈值);N管反之。

假设P管作为下管,即D极接地,此时,S级连接外部电路,VS不可知,想要通过改变G级输入控制VSG电压差,G级控制逻辑会比较复杂。

相反,将P管作为上管,那么S接VCC,VS电压确定,通过控制G级的高低电平即可控制MOS管开关。

同理分析NMOS,因此通常将P管作为上管,N管做为下管。

逻辑门的管级电路

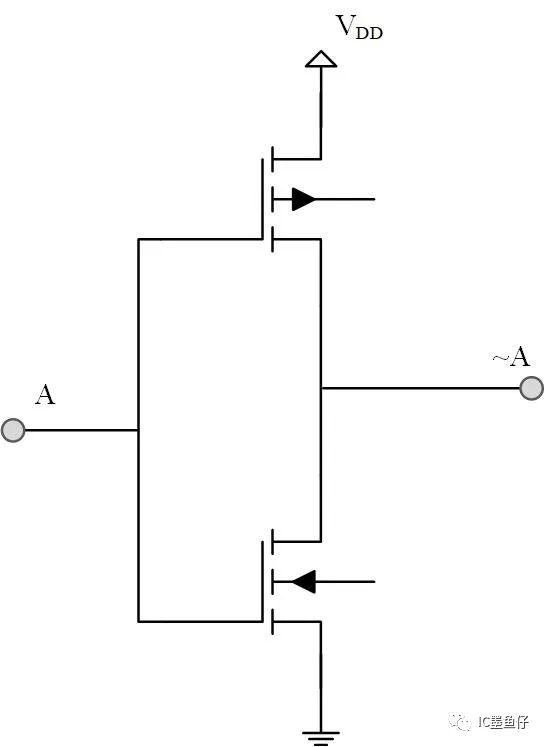

明白上述原因后,就可以理解输出的高电平由上管决定,低电平由下管决定。为了保证在某一时刻,输出只能为高电平或低电平,需要结合上下管,即当上管导通时,下管必然关断,反之亦然。

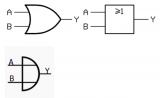

非门的管级电路如下图所示,由P管和N管串联组合而成。

当A = 1时,上管关断,下管导通,输出为0;

当A = 0时,上管导通,下管关断,输出为1。

由于MOS管本身的特性,我们无法直接搭建出与门和或门,只能通过与非门或非门结合非门间接搭出,也就是说,与门和非门的搭建至少需要6个MOS管。

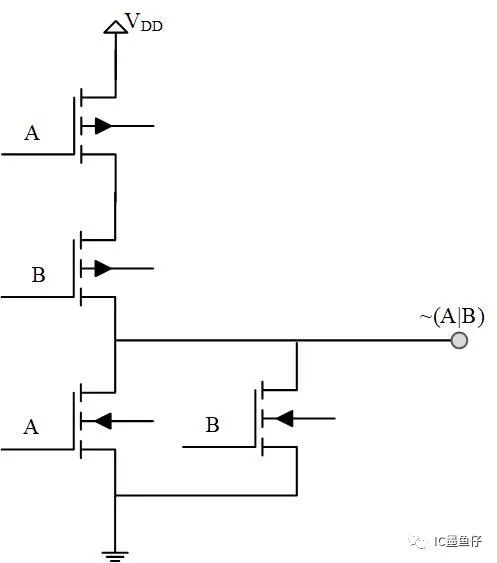

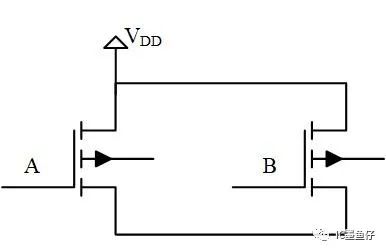

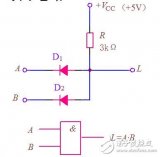

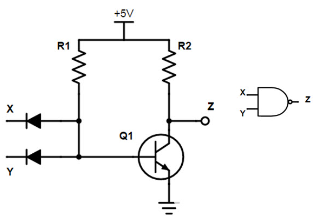

如图所示为或非门管级电路结构。两个P管串联后与两个并联的N管串联。

其输入输出特性如下表:

|

A |

B |

~(A|B) |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

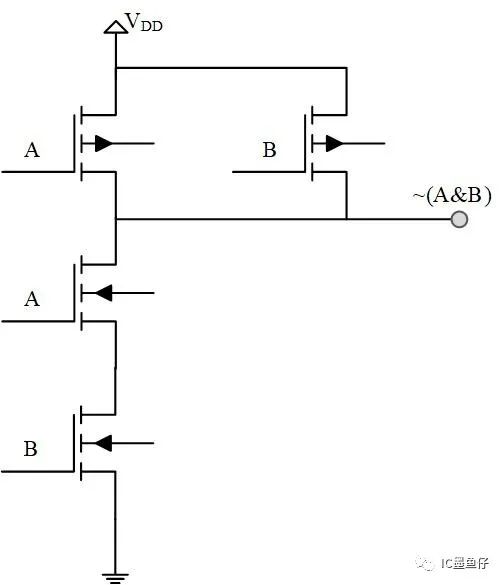

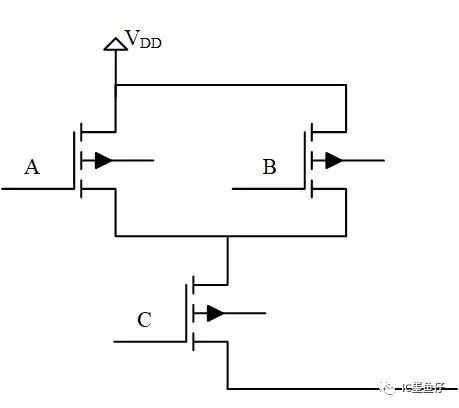

与非门的管级电路如下所示:

其输入输出特性如下所示:

|

A |

B |

~(A|B) |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

管级电路的转换

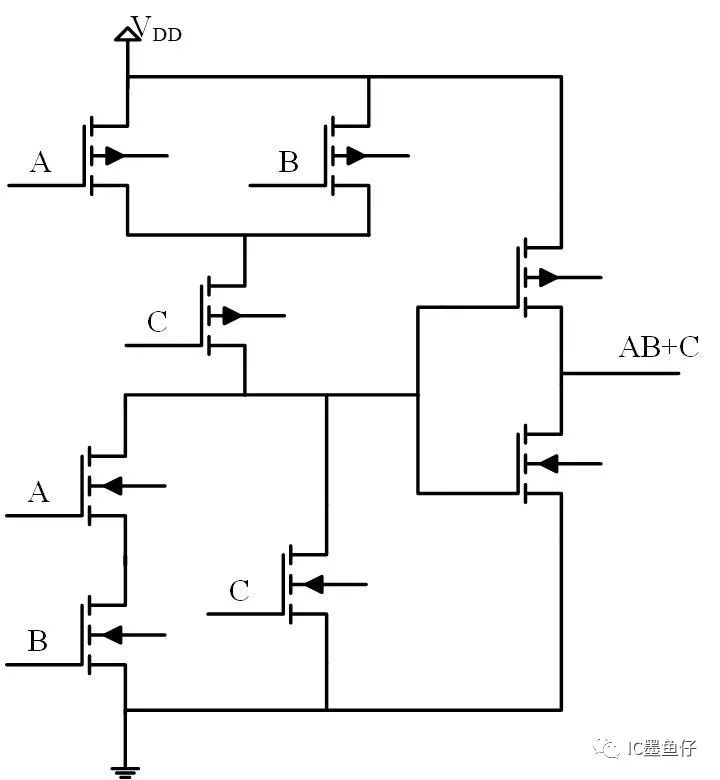

在理解了上述门电路的管级电路后,结合下述三个步骤,即可轻松用MOS管搭建任意逻辑电路。

-

对逻辑式按照摩尔公式取反,尽可能将每个输入转换成反逻辑形式;

-

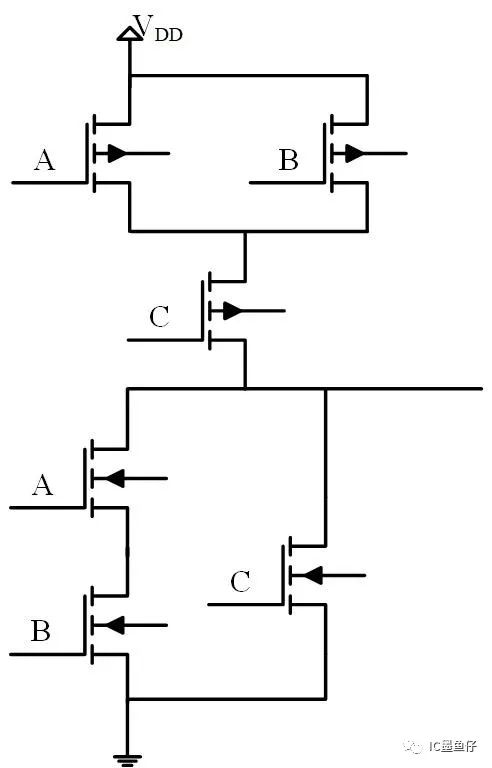

先画上管,与为串联,或为并联;下管与上管相反;

-

对整体结果取反(即加非门);

这里对D=AB+C进行举例。

D=((AB+C)')'=((AB)'C')'=((A'+B')C')'

1

A'+B'

2

(A'+B')C'

3

根据上管画出下管,串并联相互转换

4

A'+B'

审核编辑 :李倩

-

电流

+关注

关注

40文章

6928浏览量

132507 -

电路设计

+关注

关注

6678文章

2462浏览量

205073 -

逻辑门

+关注

关注

1文章

142浏览量

24102 -

MOS

+关注

关注

32文章

1280浏览量

94087 -

PMOS

+关注

关注

4文章

245浏览量

29663

原文标题:逻辑表达式如何转换为晶体管电路

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于逻辑门的构成解释如何完成任意逻辑的管级电路设计

基于逻辑门的构成解释如何完成任意逻辑的管级电路设计

评论