01旁路和去耦

旁路电容(Bypass Capacitor)和去耦电容(Decoupling Capacitor)这两个概念在电路中是常见的,但是真正理解起来并不容易。

要理解这两个词汇,还得回到英文语境中去。

Bypass在英语中有抄小路的意思,在电路中也是这个意思,如下图所示。

couple在英语中是一对的意思,引申为配对、耦合的意思。如果系统A中的信号引起了系统B中的信号,那么就说A与B系统出现了耦合现象(Coupling),如下图所示。而Decoupling就是减弱这种耦合的意思。

02电路中的旁路和去耦

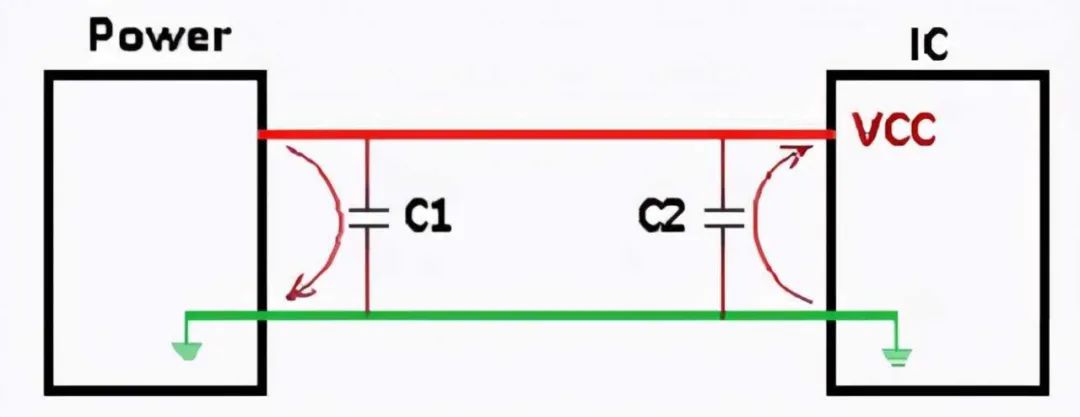

如下图中,直流电源Power给芯片IC供电,在电路中并入了两个电容。

1)旁路

如果Power受到了干扰,一般是频率比较高的干扰信号,可能使IC不能正常工作。

在靠近Power处并联一个电容C1,因为电容对直流开路,对交流呈低阻态。

频率较高的干扰信号通过C1回流到地,本来会经过IC的干扰信号通过电容抄近路流到了GND。这里的C1就是旁路电容的作用。

2)去耦

由于集成电路的工作频率一般比较高,IC启动瞬间或者切换工作频率时,会在供电导线上产生较大的电流波动,这种干扰信号直接反馈到Power会使其产生波动。

在靠近IC的VCC供电端口并联一个电容C2,因为电容有储能作用,可以给IC提供瞬时电流,减弱IC电流波动干扰对Power的影响。这里的C2起到了去耦电容的作用。

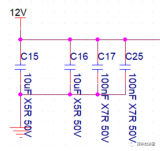

03为什么要用2个电容

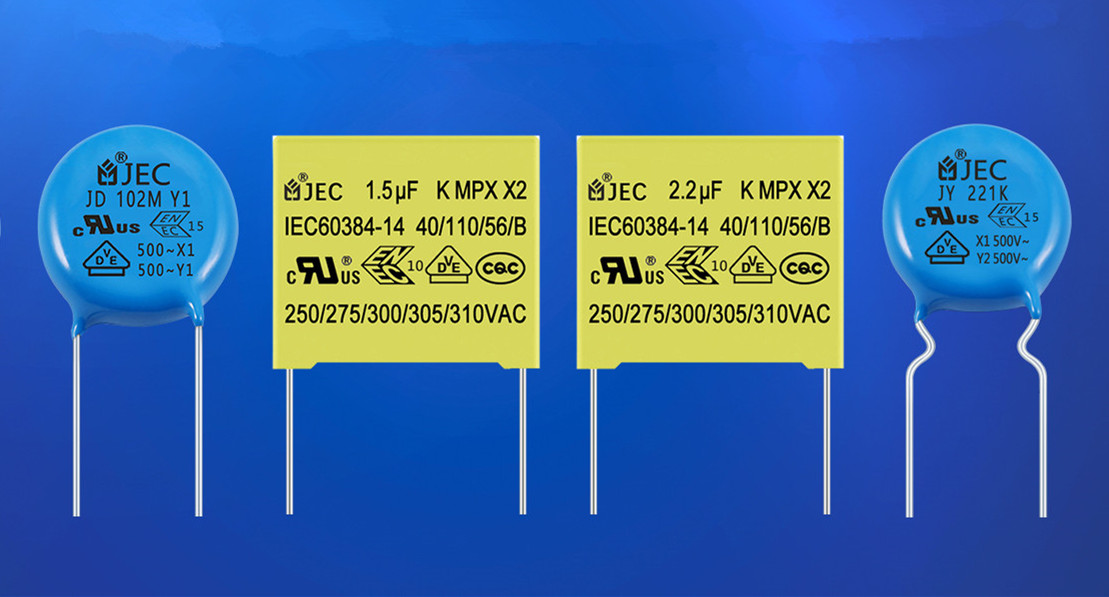

回到本文最开始提到的问题,为什么要用0.1uF和0.01uF的两个电容?

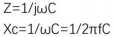

电容阻抗和容抗计算公式分别如下:

容抗与频率和电容值成反比,电容越大、频率越高则容抗越小。可以简单理解为电容越大,滤波效果越好。

那么有了0.1uF的电容旁路,再加一个0.01uF的电容不是浪费吗?

实际上,对一个特定电容,当信号频率低于其自谐振频率时呈容性,当信号频率高于其自谐振频率时呈感性。

当用0.1uF和0.01uF的两个电容并联时,相当于拓宽了滤波频率范围。

审核编辑 黄昊宇

-

pcb

+关注

关注

4333文章

23223浏览量

401854 -

电容

+关注

关注

100文章

6111浏览量

151657 -

电路设计

+关注

关注

6679文章

2474浏览量

206205

发布评论请先 登录

相关推荐

为什么PCB电路设计中加0.1uF和0.01uF电容,什么作用?

为什么PCB电路设计中加0.1uF和0.01uF电容,什么作用?

评论