来源:内容由半导体行业观察(ID:icbank)编译自semiwiki

通常,我们更喜欢把台式机/笔记本电脑的复杂指令集叫做CISC,把智能手机的精简指令集叫做RISC。戴尔和苹果等 OEM 一直在其笔记本电脑中使用 x86 CISC 处理器。让我在这里解释笔记本电脑的设计方法。主板以多核CISC处理器为主要部件,连接GPU、RAM、存储内存等子系统和I/O接口。操作系统在多核处理器上并行运行多个应用程序,管理内存分配和 I/O 操作。

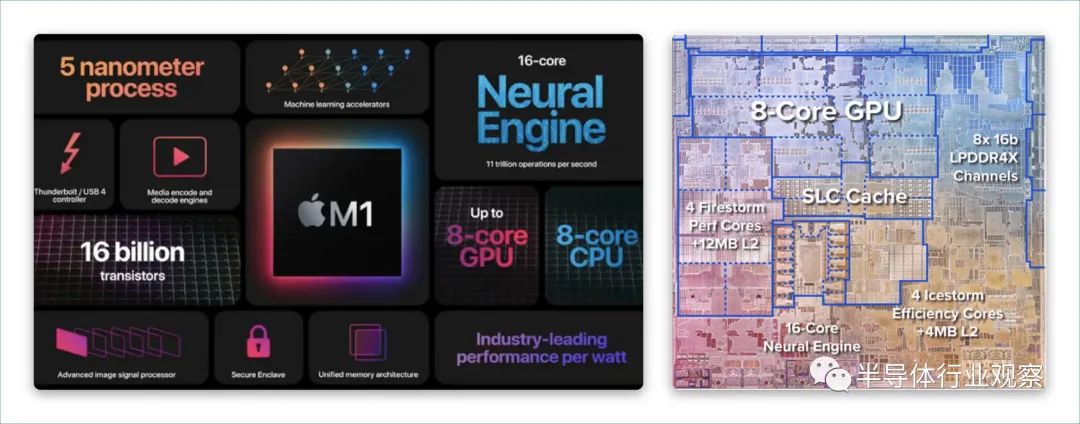

这就是我们使用处理器实现任何电子系统的方式。然而,我们更喜欢使用 RISC 处理器的智能手机系统级芯片,因为它有助于我们减小主板的尺寸和功耗。几乎整个具有多核 RISC CPU、GPU、DSP、无线和接口子系统、SRAM、闪存和 IP 的系统都在 SoC 上实现。OEM Apple 正在遵循这款智能手机的 SoC 设计方法,甚至将他们的 MAC 笔记本作为 OEM 潮流引领者。所有最新的 MAC 书籍都使用他们的 M 系列 SoC,这些 SoC 使用 ARM 的 RISC 处理器。

因此,很明显,英特尔的 x86 或 ARM 的 RISC 处理器的专有 ISA 一直是 Apple、戴尔、三星等 OEM 的选择,但现在为什么我们需要像 RISC-V 这样的开放 ISA,而不是所有这些经过充分验证的ISA。

在今天的情况下,每个人都将 SoC 用于他们的笔记本电脑和智能手机。这种复杂的 SoC 需要通用处理器和专用处理器。为了实现像 Apple 的 M 系列 SoC 这样的芯片,我们需要不同种类的处理器,如 RISC CPU、GPU、DSP、安全处理器、图像处理器、机器学习加速器、安全和神经引擎,基于来自多个 IP 的各种通用和专用 ISA供应商,如图1所示。图 1:Apple M1 SoC 参考:AnandTech

在这种情况下,主要挑战是:

1.选择并与多家 IP 供应商合作

2.不同的 IP 供应商可能有不同的 IP 许可方案,工程师将无法自由地定制 ISA 和设计,因为他们更愿意满足他们的设计目标。

3.所有专门的 ISA 都不会持续/生存很长时间,从而影响长期产品支持计划和路线图。

4.此外,涉及多个 ISA 和工具链的软件/应用程序开发和更新将具有挑战性。

RISC-V 是一种具有多种扩展功能的通用免许可开放式 ISA。它是一个 ISA,分为一个小的基本整数 ISA,可用作定制加速器和可选标准扩展的基础,以支持通用软件开发。您可以添加自己的扩展来实现您的专用处理器,或者根据需要自定义基本 ISA,因为它是开放的。没有许可证限制。因此,在未来,我们可以仅使用一个 RISC-V ISA 创建所有通用和专用处理器,并实现任何复杂的 SoC。

什么是 RISC-V,它与其他 ISA 有何不同?

RISC-V 是加州大学伯克利分校的第五个主要 ISA 设计。它是由非营利组织 RISC-V International维护的开放式 ISA,涉及所有利益相关者社区以实施和维护 ISA 规范、黄金参考模型和合规性测试套件。

RISC-V 不是 CPU 实现。它是通用处理器和专用处理器的开放式 ISA。一个完全开放的 ISA,可供学术界和工业界免费使用。

RISC-V ISA 被分成一个小的基本整数 ISA,可单独用作定制加速器或教育目的的基础,以及支持通用软件开发的可选标准扩展

RISC-V 支持应用程序、操作系统内核和硬件实现的 32 位和 64 位地址空间变体。因此,它适用于所有计算系统,从嵌入式微控制器到云服务器,如下所述。简单的嵌入式微控制器、保护运行 RTOS 的嵌入式系统、运行操作系统的台式机/笔记本电脑/智能手机以及运行多个操作系统的云服务器。

RISC-V 是一个相关 ISA 家族:RV32I、RV32E、RV64I、RV128I。

RV32I/ RV32E/ RV64I/RV128I 是什么意思:

RV——RISC-V

32/64/128 – 定义寄存器宽度 [XLEN] 和地址空间

I – 整数基 ISA

32 个用于所有基本 ISA 的寄存器

E – 嵌入式:只有 16 个寄存器的基本 ISA

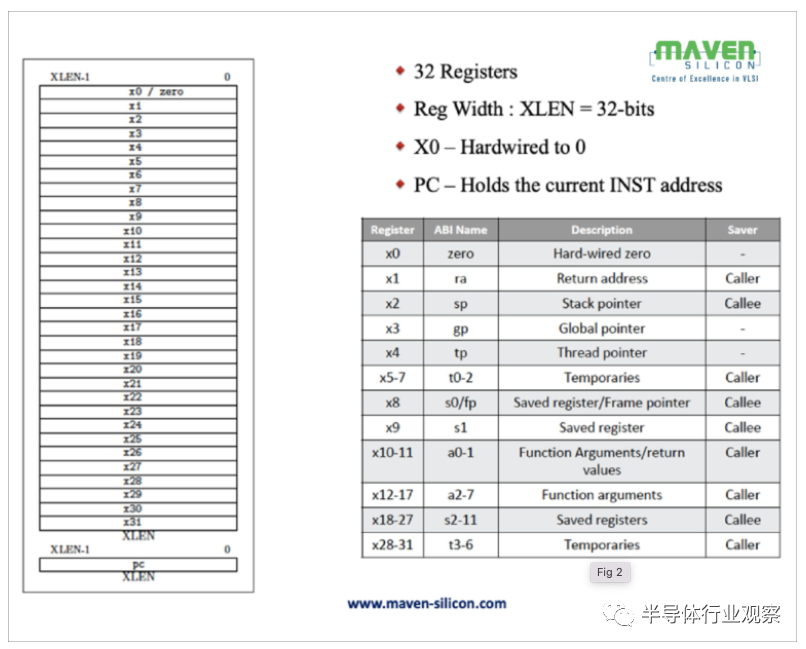

(1)RISC-V 寄存器:

所有基本 ISA 都有 32 个寄存器,如图 2 所示,除了 RV32E。只有RV32E base ISA对于简单的嵌入式微控制器只有16个寄存器,但寄存器宽度仍然是32位。寄存器 X0 硬接线为零。称为程序计数器的特殊寄存器保存要从内存中获取的当前指令的地址。如图 2 所示,RISC-V 应用程序二进制接口,ABI 定义了寄存器的标准功能。为了简单和一致,软件开发工具通常使用 ABI 名称。根据 ABI,额外的寄存器专用于 X0 到 X15 范围内的保存寄存器、函数参数和临时变量,主要用于 RV32E 基础 ISA,它只需要前 16 个寄存器来实现简单的嵌入式微控制器。但是 RV32I 基础 ISA 将拥有所有 32 个寄存器 X0 到 X31。图 2:RISC-V 寄存器和 ABI 名称参考:RISC-V 规范

(2)RISC-V内存:

RISC-V hart [硬件线程/核心] 具有用于所有内存访问的 2^XLEN 字节的单字节可寻址地址空间。XLEN 表示整数寄存器的位宽度:32/64/128。内存字定义为 32 位(4 字节)。相应地,半字为16位(2字节),双字为64位(8字节),四字为128位(16字节)。内存地址空间是循环的,因此地址 2^XLEN -1 处的字节与地址零处的字节相邻。因此,由硬件完成的内存地址计算忽略溢出,而是环绕模 2^XLEN。RISC-V 基础 ISA 具有小端或大端存储系统,特权架构进一步定义了大端操作。指令作为 16 位小尾数法包的序列存储在内存中,而不管内存系统的字节顺序如何。(3)RISC-V 加载存储架构

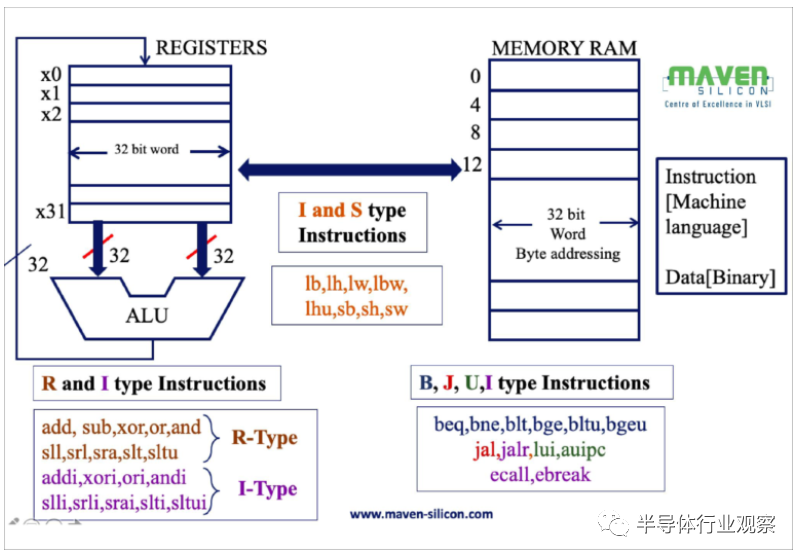

您可以可视化基于 RISC-V 寄存器和内存的 RISC-V 加载存储架构,如下图 3 所示。

RISC-V处理器根据PC中的地址从主存中取/载指令,译码32位指令,然后ALU进行算术/逻辑/内存读写操作。ALU 的结果将存储回其寄存器或内存中。

图 3:RISC-V 加载存储架构

(4)RISC-V RV32 I 基础 ISA

RV32I base ISA 只有 40 条 Unique Instructions,但简单的硬件实现只需要 38 条指令。R-Type:注册到注册说明

I-Type:立即注册、加载、JLR、Ecall 和 Ebreak

S型:商店

B型:分支

J型:跳跃和链接

U 型:立即加载/添加上层

图 4:RV32I 基本 ISA 指令格式

(5)用于优化 RTL 设计的 RISC-V ISA

在这里,我想解释一下 RISC-V ISA 如何使我们能够实现优化的寄存器传输级设计,以满足低功耗和高性能的目标。如图 4 所示,RISC-V ISA 在所有格式中将源(rs1 和 rs2)和目标(rd)寄存器保持在相同位置以简化解码。立即数总是经过符号扩展,并且通常被打包到指令中最左边的可用位,并且已被分配以降低硬件复杂性。尤其是,

所有立即数的符号位总是在指令的第 31 位以加速符号扩展电路。符号扩展是对立即数最关键的操作之一(特别是对于 XLEN>32),在 RISC-V 中,所有立即数的符号位始终保存在指令的第 31 位中,以允许符号扩展与指令解码并行进行。为了加快解码速度,基础 RISC-V ISA 将最重要的字段放在每条指令的同一位置。正如您在指令格式表中所见,

但是为什么立即位会被打乱呢?想想解码直接场的物理电路。由于它是硬件实现,因此这些位将被并行解码;输出立即数中的每一位都有一个多路复用器来选择它来自哪个输入位。多路复用器越大,成本越高,速度也越慢。

值得注意的是,只需要主要操作码(位 0-6)就可以知道如何解码立即数,因此立即数解码可以与指令其余部分的解码并行完成。

(6)RV32I 基本 ISA 指令

图 5:RISC-V ISA 扩展

我们遵循 RISC-V 处理器的命名约定,如下所述:RISC-V 处理器:RV32I、RV32IMAC、RV64GCRV32IMAC:整数基础 ISA + 扩展:[乘法 + 原子 + 压缩]RV64GC:64 位 IMAFDC [G-通用:IMAFD]整数 64 位基本 ISA + 扩展:[乘法 + 原子 + SP 浮动 + DP 浮动 + 压缩]

RISC-V 特权架构涵盖了 RISCV 系统的所有方面,超出了我到目前为止所解释的非特权 ISA。特权架构包括特权指令以及运行操作系统和连接外部设备所需的附加功能。

根据 RISC-V 特权规范,我们可以实现从简单的嵌入式控制器到复杂的云服务器的不同类型的系统,如下所述。应用程序执行环境 – AEE:“裸机”硬件平台,其中 harts 直接由物理处理器线程实现,指令可以完全访问物理地址空间。硬件平台定义了一个从上电复位开始的执行环境。示例:简单且安全的嵌入式微控制器主管执行环境——参见:RISC-V 操作系统,通过将用户级 harts 多路复用到可用的物理处理器线程并通过虚拟内存控制对内存的访问来提供多个用户级执行环境。

Hypervisor Execution Environment – HEE:RISC-V hypervisor,为来宾操作系统提供多个管理级执行环境。

图 6:RISC-V 特权软件堆栈参考:RISC-V 规范

此外,RISC-V 特权规范定义了各种控制和状态寄存器 [CSR],以实现各种功能,如任何系统的中断、调试和内存管理设施。您可能需要参考规范以探索更多信息。

如本文所述,我们可以使用通用的开放式 RISC-V ISA 高效地实现任何系统,从简单的物联网设备到复杂的智能手机和云服务器。由于单片半导体缩放失败,专业化是提高计算性能的唯一途径。开放式 RISC-V ISA 是模块化的,支持自定义指令,使其成为创建各种专用处理器和加速器的理想选择。

随着 IEEE 标准通用验证方法论的出现,我们在芯片验证方面取得了巨大成功,开放的 RISC-V ISA 也将继承各种专有 ISA 的所有优点,成为行业标准 ISA,引领我们走向未来开放的计算时代。您准备好使用 RISC-V 专业知识迎接这个美好的未来了吗?原文链接:https://semiwiki.com/semiconductor-services/maven-silicon/321555-is-your-career-at-risk-without-risc-v/

欢迎加入Imagination GPU与人工智能交流2群

(添加请备注公司名和职称)

对话Imagination中国区董事长:以GPU为支点加强软硬件协同,助力数字化转型

对话Imagination中国区董事长:以GPU为支点加强软硬件协同,助力数字化转型

Imagination Technologies是一家总部位于英国的公司,致力于研发芯片和软件知识产权(IP),基于Imagination IP的产品已在全球数十亿人的电话、汽车、家庭和工作场所中使用。获取更多物联网、智能穿戴、通信、汽车电子、图形图像开发等前沿技术信息,欢迎关注 Imagination Tech!

原文标题:RISC-V给我们带来了什么?

文章出处:【微信公众号:Imagination Tech】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:RISC-V给我们带来了什么?

文章出处:【微信号:Imgtec,微信公众号:Imagination Tech】欢迎添加关注!文章转载请注明出处。

相关推荐

嘿,咱来聊聊RISC-V MCU技术哈。

这RISC-V MCU技术呢,简单来说就是基于一个叫RISC-V的指令集架构做出的微控制器技术。RISC-V这个啊,2010年的时候,是加州大

发表于 01-19 11:50

“RISC-V产业发展大会”将于12月28日在北京亦庄通明湖会展中心举办。作为推动RISC-V生态发展的重要力量,赛昉科技将受邀出席此次盛会,带来应用、软件和人才

![的头像]() 发表于

发表于 12-24 11:10

•493次阅读

,设计人员可根据自己擅长的逻辑捕获语言,用不同的语言编写。”

O\'Connor强调OpenHW集团不只开发RISC-V内核。“我们真正专注的是异构集群计算所需的构件,用于各种尺寸的SoC。我们将不同类

发表于 11-26 20:20

目前,开源指令架构集RISC-V正以前所未有的速度高速发展,RISC-V以其开放、模块化和可扩展的核心特性,极大地降低了开发者参与创新的技术门槛,为整个半导体产业带来了前所未有的机遇。全球已经有70

![的头像]() 发表于

发表于 11-12 01:08

•327次阅读

我们会迎来前所未见的AI软件应用,而RISC-V有望打造出下一代的AI引擎。”

达摩院院长张建锋此前在3月2024玄铁RISC-V生态大会表示,随着新型算力需求激增,RISC-V发展迎

发表于 10-31 16:06

加入RISC-VAdvocate行列!我们正在寻找来自世界各地的RISC-V爱好者,通过全球推广和参与,成为支持RISC-V进步的关键参与者。作为一名

![的头像]() 发表于

发表于 09-10 08:08

•531次阅读

沁恒在历届峰会上分享RISC-V在MCU领域的创新成果,和大家共同见证了本土RISC-V产业的成长。早在第一届RISC-V中国峰会上,沁恒就公开了青稞RISC-V系列量产芯片的关键技术

![的头像]() 发表于

发表于 08-30 18:18

•1680次阅读

第四届RISC-V中国峰会(RISC-V Summit China 2024)于8月21日至23日在杭州盛大召开,成为RISC-V领域的一次重要盛会

![的头像]() 发表于

发表于 08-26 18:33

•1004次阅读

RISC-V的发展历史可以追溯到2006年左右,当时David Patterson和其他研究者开始探索创建一个开放和可扩展的指令集架构(ISA)。以下是RISC-V发展的主要里程碑:

一、起源与初步

发表于 07-29 17:20

RISC-V作为一种开源的指令集架构(ISA),自其诞生以来就受到广泛关注和应用,但它也存在一些不足之处。以下是RISC-V架构目前存在的主要缺点:

1. 性能问题

相对于专用ISA的性能差距:尽管

发表于 07-29 17:18

科技热潮呢?我们一起来探索其中的奥秘。RISC-V是什么?我们先来了解一下什么是指令集架构。指令集是计算机运行的核心,就像是电脑的“操作指南”。目前,主流的指令集架

![的头像]() 发表于

发表于 07-12 08:28

•726次阅读

提供了一个突破传统束缚、实现自主创新的绝佳平台。同时,随着通用人工智能技术的不断进步,与RISC-V架构结合的潜力巨大,为国产信创产业带来了新的增长点。此外,安全性

![的头像]() 发表于

发表于 07-05 08:36

•538次阅读

RISC-V的云端部署上取得了重要突破,成功将RISC-V丛集部署到云端服务器,为国内的RISC-V芯片开发和应用带来了更多的机会和可能性。同时,学术界也在积极推动

发表于 04-28 09:04

4月12日,第二期“大家来谈芯|解锁RISC-V技术力量”在上海临港新片区顶科永久会址举办,本期沙龙聚焦RISC-V技术,围绕AI时代的RISC-V市场机会、RISC-V在汽车领域的应

![的头像]() 发表于

发表于 04-16 08:16

•827次阅读

RISC-V不仅仅是一个流行语;它建立在坚实的技术基础之上,使其有别于其他指令集架构 (ISA)。RISC-V的核心是基于精简指令集计算(RISC)原则,强调效率和性能。

发表于 03-26 09:34

•3737次阅读

RISC-V给我们带来了什么?

RISC-V给我们带来了什么?

评论