单片 SoC 的尺寸变得太大,无法制造 某些 SoC 的功能要获得最佳实现,可能需要不同的工艺节点 对增强产品的可扩展性和可组合性需求正在增加

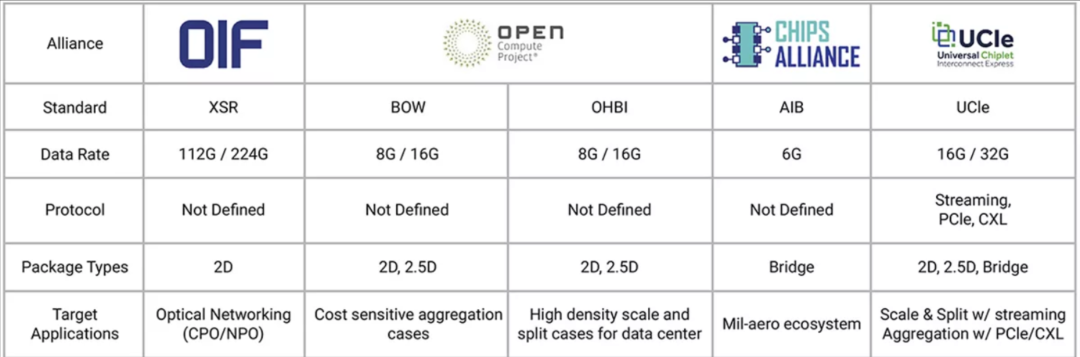

Optical Interface Forum (OIF) – 针对晶粒间连接而优化的 XSR 和 USR 物理层规范 Chips Alliance – 最初由英特尔推出的 AIB 规范 Open Compute Platform (OCP) – 针对不同用例而优化的 OpenHBI 和 Bunch-of-Wires (BOW) 规范 Unified Chiplet Interconnect Express (UCIe) – 涵盖多个用例和完整协议栈的全面晶粒间互连规范

UCIe 系谱

UCIe 路线图和用例

用于先进封装(硅中介层、硅桥或 RDL 扇出)的 UCIe 用于标准包装(有机基材或层压板)的 UCIe

UCIe 规范概述

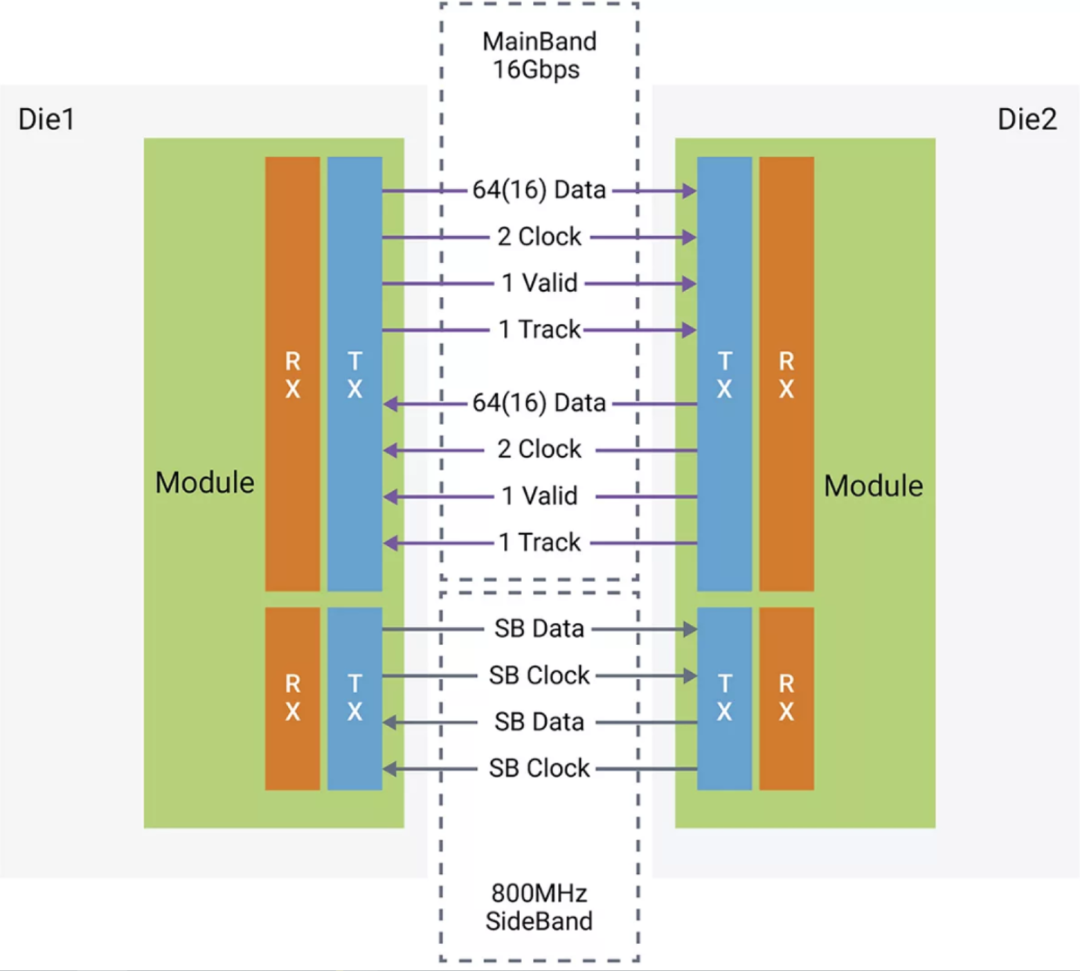

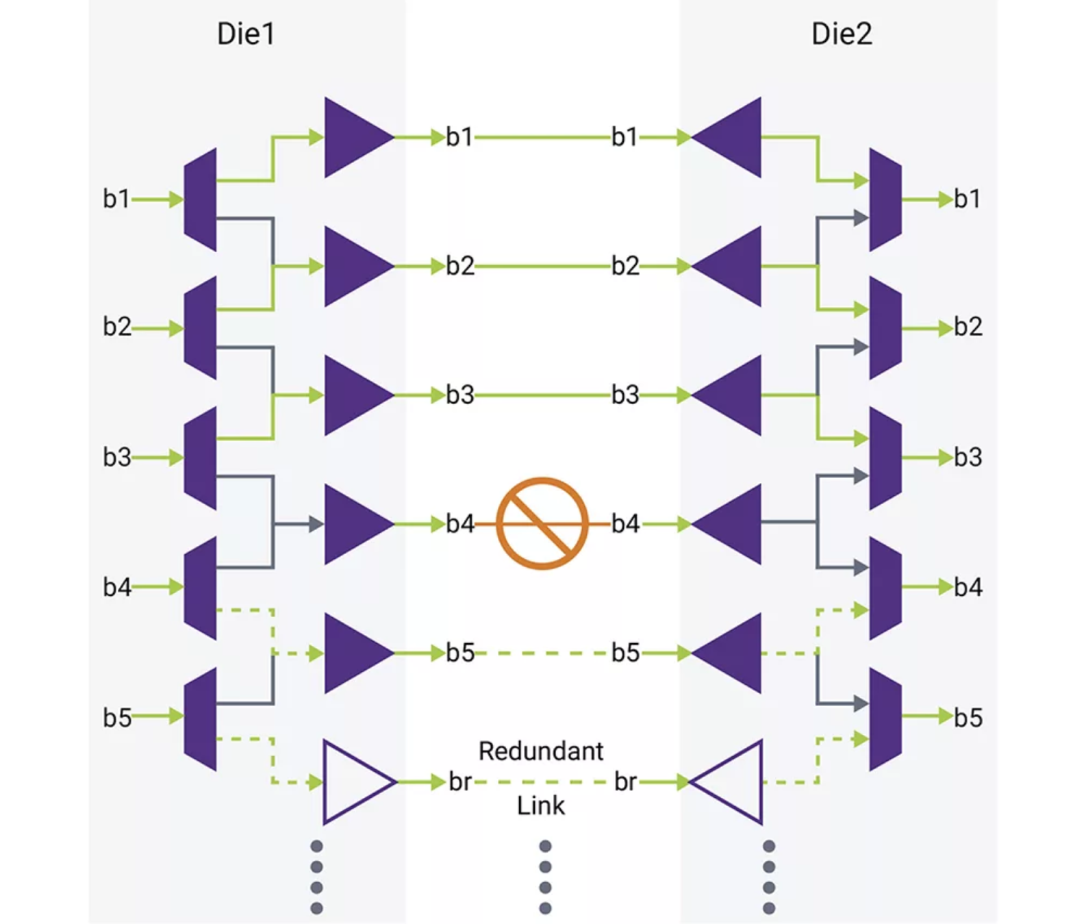

物理层是封装介质的电气接口。它包括电气 AFE(发射器、接收器)以及边带信道,可实现两个晶粒之间的参数交换和协商。它还包括可实现链路初始化、训练和校准算法以及测试和修复功能的逻辑 PHY。 晶粒间适配器层负责链路管理功能以及协议仲裁和协商。它包括基于 CRC 和重试机制的可选纠错功能。 协议层实施一个或多个 UCIe 支持的协议。如今,此类协议是 PCI Express、CXL 和/或流式传输协议。它们是基于 Flit 的协议,可提供最高效率和更低的延迟。

物理层

晶粒间适配器层

CXL3 256B 标准 FLIT 模式 CXL3 256B 延迟优化 FLIT 模式 PCIe6 256B FLIT 模式 CXL2 68B 增强型 FLIT 模式 流式传输 64B 原始模式

协议层

结语

原文标题:多晶粒SoC成趋势,UCIe标准助其一臂之力

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电子发烧友网

+关注

关注

1010文章

544浏览量

164398

原文标题:多晶粒SoC成趋势,UCIe标准助其一臂之力

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

金刚石多晶材料:高功率器件散热解决方案

功率器件散热材料的理想选择。 金刚石多晶材料的特点 多晶结构:金刚石多晶材料由多个微小的金刚石晶粒组成,具有各向同性的热导率和机械性能。 成本较低:与天然单晶金刚石相比,金刚石

云服务赋能数字化转型!828 企业节亮相的这款产品助您一臂之力

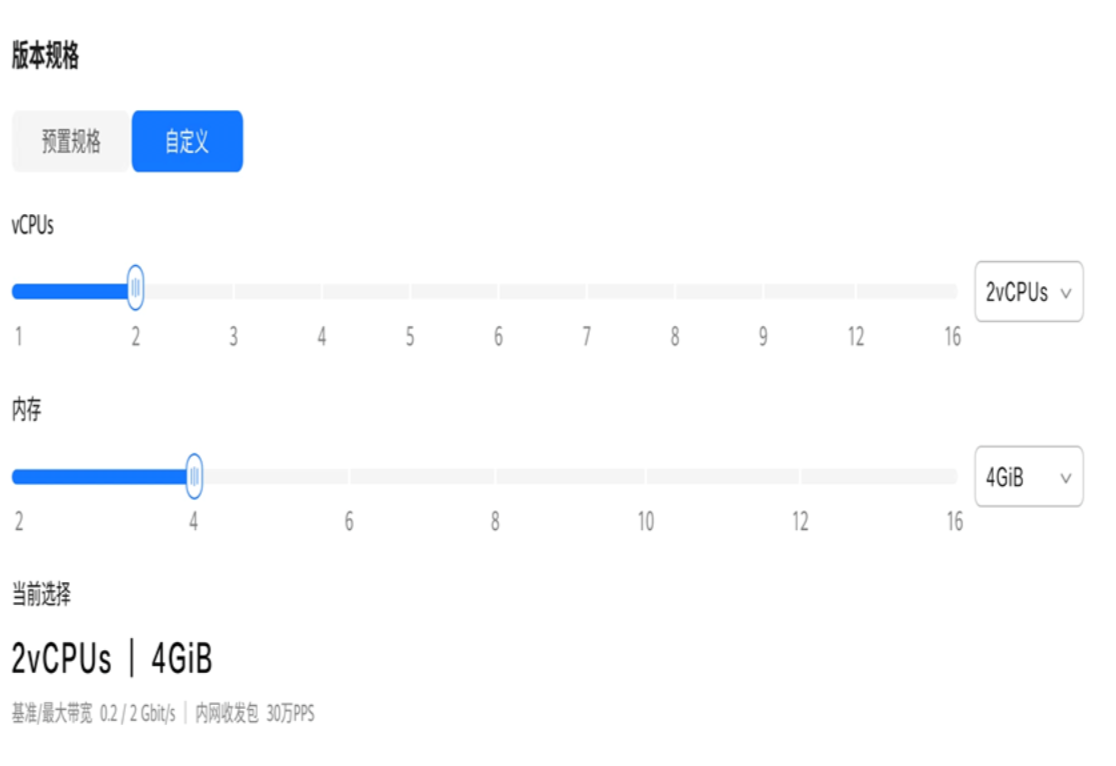

的核心产品,它可以提供计算、存储、网络等资源,承载了最基础也最重要的任务,性价比高、安全可靠、稳定性强的云服务器,是中小企业上云、用云,加快数字化转型的关键。 作为重磅推出的下一代“柔性算力”新物种,华为云

西部数据实用贴心好礼 满足父亲全面存储需求

硬盘WD_BLACK™ P40 游戏移动固态硬盘定可助父亲一臂之力,轻松驰骋游戏世界。 WD_BLACK™ P40 游戏移动固态硬盘 WD_BLACK P40 游戏移动固态硬盘适用于存储

新思科技与英特尔在UCIe互操作性测试进展

英特尔的测试芯片Pike Creek由基于Intel 3技术制造的英特尔UCIe IP小芯片组成。它与采用台积电公司N3工艺制造的新思科技UCIe IP测试芯片形成组合。

提升LED生产质量,木几LED透镜视觉偏心检测机助您一臂之力!

在LED照明和显示屏行业,LED透镜和LED灯珠之间贴合的精密度和同心度直接影响着产品的效果。为了确保每一颗透镜都达到贴合标准不出现遮光、漏光、偏光等缺陷,木几推出了LED透镜偏心检测机,用科技为品质保驾护航。

软件改变汽车进行时,VectorCAST助你一臂之力

作者|哪里桃小编|不吃猪头肉一百三十多年前,奔驰夫人贝尔塔为了回击社会舆论对奔驰一号的质疑,驾驶着奔驰汽车从曼海姆出发,直驶104公里外的位于普福尔茨海姆的娘家,全程虽开的磕磕绊绊,但却为汽车的宣传

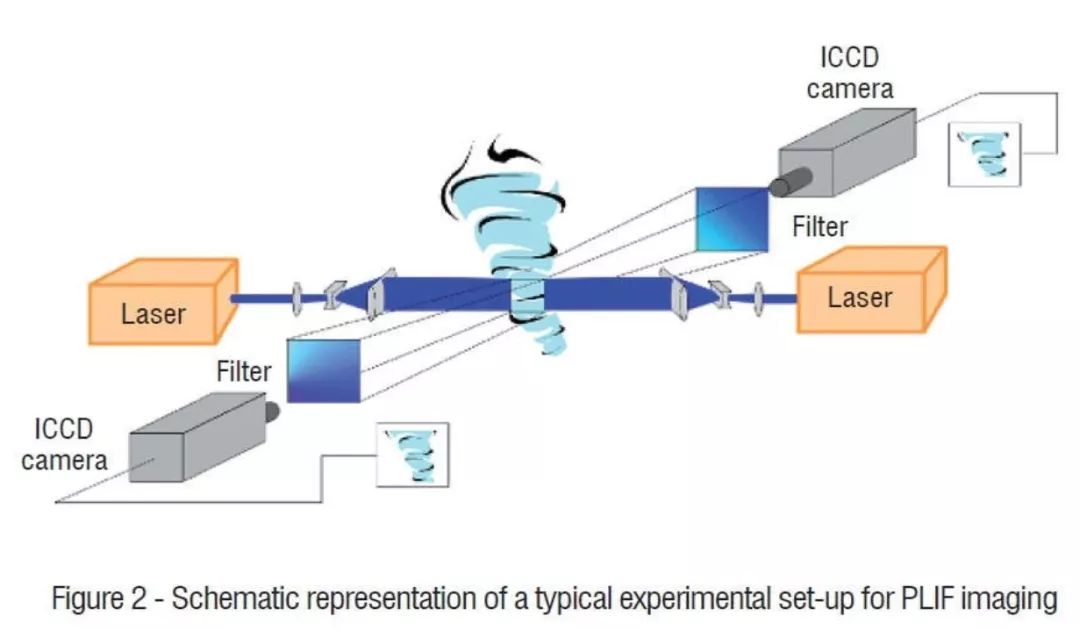

普林斯顿仪器为燃烧领域的研究提供一臂之力

的六大热门应用领域中的燃烧领域。 1、为什么研究燃烧? 人类文明发展的每一步都与燃烧利用息息相关,人类的文明史,就是燃烧的利用史。知道燃料的燃烧方式及原理,了解燃烧进程,排放的污染物等,对于燃烧类的工程活动至关

多晶硅的用途包括哪些

成太阳能电池板。多晶硅可以将太阳光转化为电能,并应用于太阳能发电系统,使之成为可再生能源的重要组成部分。 半导体芯片制造:多晶硅是制造集成电路芯片的主要材料之一。通过将

多晶粒SoC成趋势,UCIe标准助其一臂之力

多晶粒SoC成趋势,UCIe标准助其一臂之力

评论