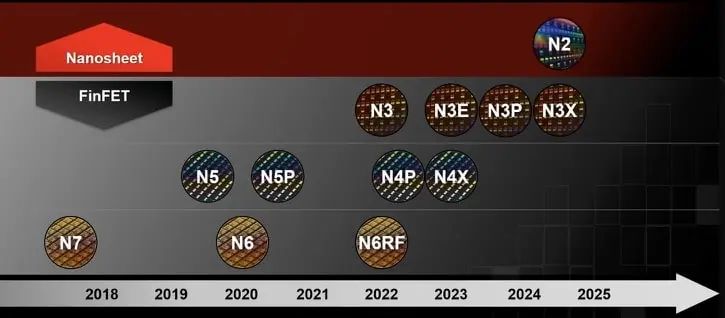

11月10日,台积电(TSMC)研究员兼副总裁L.C. Lu在短短26分钟内用几十张幻灯片讲述了如何实现系统创新。台积电是全球最大的半导体代工企业,其开放创新平台(OIP)活动广受欢迎,参与人数众多,其提供的工艺技术和知识产权对许多半导体设计部门都非常有吸引力。台积电的技术路线图展示了FinFET和Nanosheet到2025年的计划表。

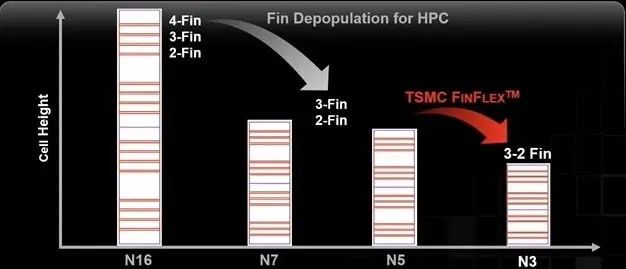

从N3开始,有一个叫做FinFlex的新东西,它使用了设计技术协同优化(DTCO),承诺在节能和高性能等领域提高功率、性能和面积(PPA)。使用FinFlex方法,设计师可以根据他们的设计目标,从三种晶体管配置中选择:

•3-2fin blocks,用于高性能;

•2-2 fin,高效性能;

•2-1 fin,最低的功率,最佳密度;

进程节点N16到N3中使用的fin blocks选择的历史如下所示:

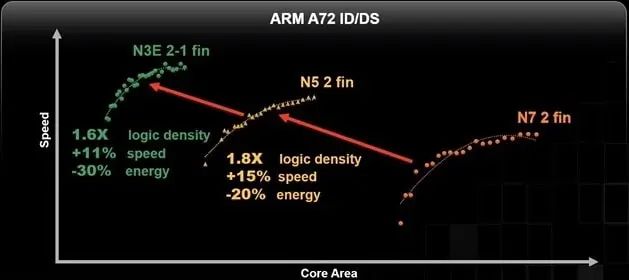

EDA供应商Synopsys, Cadence, Siemens EDA和ANSYS已经更新了他们的工具来支持FinFlex,在一个单一的SoC内,甚至可以混合不同的fin blocks。在时序关键路径上,可以使用high-fin单元,而非关键路径单元可以使用low fin。作为进程缩放效益的一个例子,Lu展示了一个ARM Cortex-A72 CPU,它在N7中实现了2fin,N5实现了2 fin,最后N3E实现了2-1 fin:

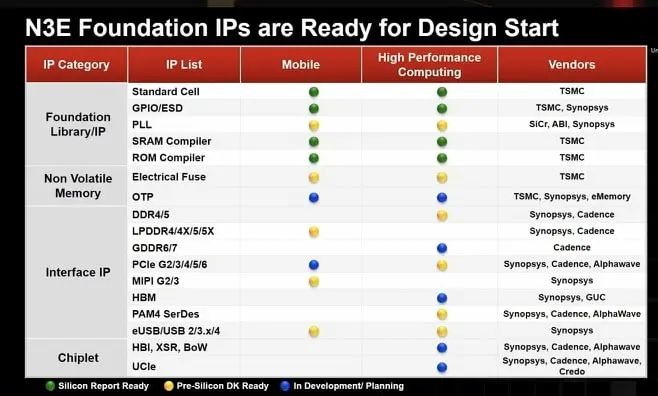

用于N3E的IP单元来自几个供应商:TSMC, Synopsys, Silicon Creations, Analog Bits, memory, Cadence, Alphawave, GUC, Credo。知识产权准备有三种状态:报告准备,设计工具包准备,以及开发状态。

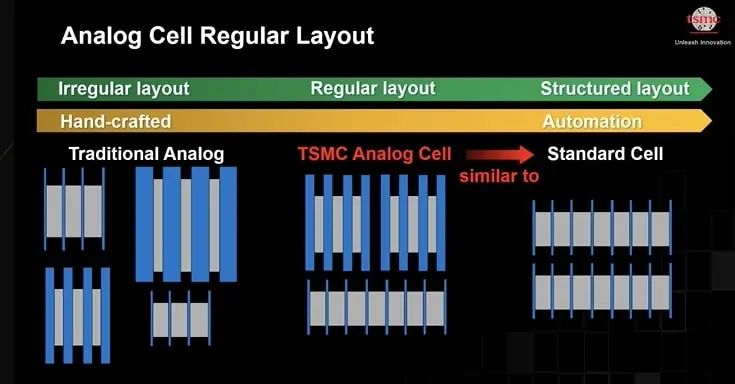

模拟IP

在台积电,他们的模拟IP使用了更结构化的规则布局,这产生了更高的成品率,并让EDA工具自动化模拟流,以提高生产率。TSMC模拟电池具有均匀的聚氧化物密度,有助于提高产量。他们的模拟迁移流、自动晶体管尺寸和匹配驱动Place和Route使Cadence和Synopsys工具实现设计流自动化。

模拟单元可以通过以下步骤进行迁移:原理图迁移、电路优化、自动放置和自动路由。例如,使用模拟迁移流将VCO单元从N4迁移到N3E需要20天,而手动方法需要50天,大约快2.5倍。

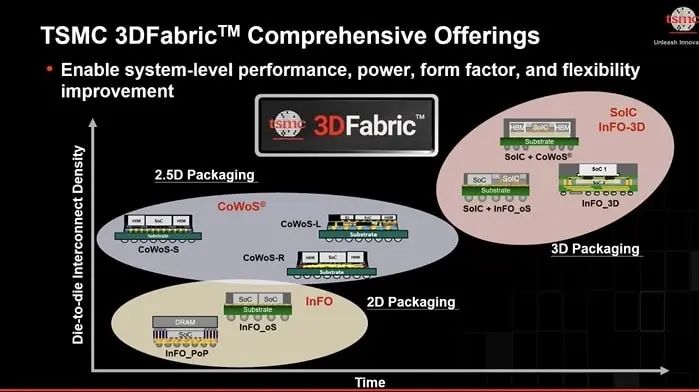

3D Fabric

台积电有三种封装需要考虑:

•二维封装

ØInFO_oS

ØInFO_PoP

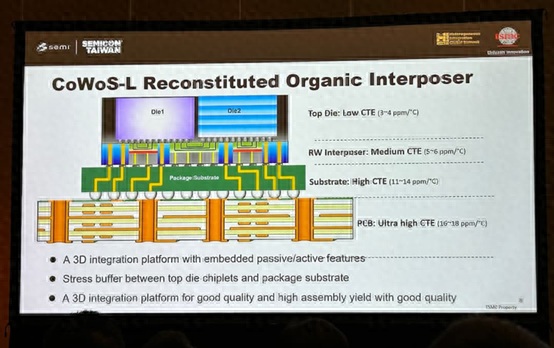

•2.5 D封装

ØCoWoS

•三维封装

ØSoIC

ØInFO-3D

在3D Fabric中有八种封装选择:

最近使用SoIC封装的一个例子是数据中心CPU AMD EPYC处理器,其互连密度比2D封装提高了200倍,比传统3D堆叠提高了15倍,CPU性能提高了50-80%。

3D IC设计的复杂性是通过3Dblox解决的,这是一种使用通用语言实现EDA工具互操作性的方法,涵盖了物理架构和逻辑连接。四大EDA供应商(Synopsys, Cadence, Siemens, Ansys)已经通过完成一系列五个测试用例:CoWoS-S, InFO-3D, SoIC, CoWoS-L 1, CoWoS-L 2,为3Dblox方法准备好了他们的工具。

台积电建立了3DFabric联盟,与跨领域的供应商合作:IP、EDA、设计中心联盟(DCA)、云计算、价值链联盟(VCA)、内存、OSAT、衬底、测试。在内存集成方面,台积电与美光、三星内存和SK海力士合作,实现CoWoS和HBM的集成。EDA测试供应商包括:Cadence, Siemens EDA和Synopsys。IC测试供应商包括:Advantest和Teradyne。

总结

像AMD、AWS和NVIDIA这样的半导体设计公司正在使用3DFabric联盟,随着2D、2.5D和3D封装的推广吸引更多的产品创意,这个数字只会随着时间的推移而增加。台积电拥有世界一流的工程团队致力于DTCO的研发,有足够的国际竞争使他们不断创新新业务。台积电在FinFlex上宣布的技术路线图选择将使数字、模拟和汽车细分市场受益。3D芯片设计由3DFabric联盟的团队支持。

审核编辑 :李倩

-

处理器

+关注

关注

68文章

19342浏览量

230203 -

eda

+关注

关注

71文章

2767浏览量

173421 -

3D封装

+关注

关注

7文章

135浏览量

27149

原文标题:台积电:2025年用几纳米?3D封装怎么整?

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

台积电:2025年用几纳米?3D封装怎么整?

台积电:2025年用几纳米?3D封装怎么整?

评论