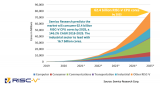

随着各行业加速向 RISC-V 转变,开放标准指令集架构 (ISA) 正在引领新一波创新与协作。为了推动这一趋势,高度可扩展 RISC 处理器 IP 的领先开发商MIPS宣布推出 eVocore () P8700,这是业界性能最高、可扩展性最强的 RISC-V 多处理器 IP。

P8700 已获得汽车驾驶员辅助系统 (ADAS) 和自动驾驶等应用的许可。

eVocore P8700 多处理器 IP 内核具有一流的性能效率,适用于片上系统 (SoC) 应用,是首批基于 RISC-V 开放 ISA 的 MIPS 产品之一。P8700 是第一个提供乱序 (OOO) 处理和一致的多线程、多核、多集群可扩展性的 RISC-V IP 内核——这使半导体公司和 OEM 能够实现新水平的 RISC-V 性能并进一步加快创新。

P8700 将深度pipeline与多问题 OOO 执行和多线程相结合,以提供出色的计算吞吐量。内核的高水平可扩展性使其非常适用于汽车(ADAS、AV、IVI)、数据中心和存储以及高性能计算 (HPC) 等广泛市场和应用中的计算密集型任务。

“包括 P8700 在内的 eVocore 系列 IP 内核代表了 MIPS 在我们全面采用 RISC-V 时的持续发展,” MIPS 首席执行官Desi Banatao说。“我们设计 P8700 是为了让客户能够在 CPU IP 内核中利用 RISC-V 的强大功能,从而提供最高水平的可扩展性和性能。我们相信我们的 RISC-V P8700 多处理器内核将有助于使以下公司成为可能:各种规模的创新 SoC 解决方案可以快速推向市场。”

在广泛且不断发展的工具和软件生态系统的支持下,客户现在可以开始使用 P8700 进行设计。

eVocore P8700 的特点包括:

可扩展至 64 个集群、512 个内核和 1,024 个 harts/线程

单线程性能优于其他 RISC-V CPU IP 当前可用的性能

适用于各种应用程序中的计算密集型任务。包括汽车、数据中心和存储、HPC 等

P8700 还包括强大的汽车安全功能,例如:

性能高效的 ASIL-D 系统的安全性和性能之间的完美平衡

可用于多种应用(视觉、雷达、激光雷达等)的稳健安全模型

内部故障检测和报告;特殊故障总线监视器,可加快系统恢复速度

MIPS 的 eVocore P8700 多处理器已获得Mobileye的许可,Mobileye 是 ADAS 和自动驾驶技术及解决方案开发和部署的领导者。Mobileye 已将 P8700 纳入其最新一代 EyeQ Ultra 片上系统 (SoC)。

“Mobileye 高效、可扩展且经过验证的 EyeQ SoC 正在推动驾驶辅助和自动驾驶汽车技术的革命。新的 MIPS eVocore CPU 不仅提供了 MIPS 众所周知的无与伦比的性能和效率组合,而且还提供了差异化的开放的软件开发环境,” Mobileye 工程执行副总裁Elchanan Rushinek说道,该公司的技术已被多家汽车制造商采用。

P8700 提供标准版和具有功能安全特性的汽车版。汽车版本已证明适用于 ISO 26262 ASIL-B(D) 和 ASIL-D 系统的强大安全功能,利用安全元素断章取义 (SEooC) 缩短上市时间。

审核编辑 :李倩

-

处理器

+关注

关注

68文章

19259浏览量

229653 -

mips

+关注

关注

1文章

239浏览量

47749 -

RISC-V

+关注

关注

45文章

2270浏览量

46130

原文标题:MIPS 推出首款 RISC-V IP 内核:支持乱序处理、多线程、多核、多集群

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RISC-V架构及MRS开发环境回顾

《RISC-V能否复制Linux 的成功?》

RISC-V内核是如何与FPGA内核进行资源共享的?

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

国产RISC-V MCU推荐

Achronix与Bluespec联合宣布推出一款支持Linux的RISC-V软处理器

瑞萨电子推出采用自研RISC-V CPU内核的通用32位MCU

瑞萨电子推出采用自研CPU内核的通用32位RISC-V微控制器

瑞萨推出采用自研CPU内核的通用32位RISC-V MCU 加强RISC-V生态系统布局

芯来科技发布超低功耗嵌入式RISC-V处理器CPU IP—NS100系列内核

MIPS推出首款RISC-V IP内核

MIPS推出首款RISC-V IP内核

评论