在低功耗特性中,软件可能实现起来并没有那么难,从设计到实现的时间可能并不会耗时特别长,耗时最长的是后续的商用问题定位以及对功耗的优化,这些都是建立在一定的实战基础上才能做的越来越好,在这里推荐几种比较常用的优化或者定位问题的手段供大家参考,希望能给大家带来一些帮助。

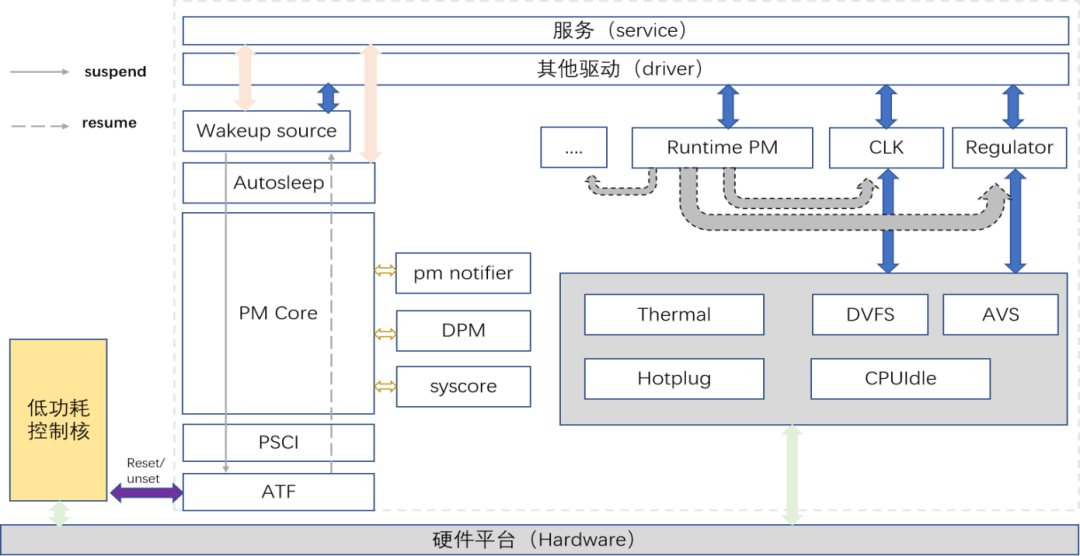

图:低功耗软件栈组成

19.1多子系统配置

比如某一个公共外设,如果多个子系统共用的话,在芯片设计上建议每个子系统各放置一个,这样一可以节省系统运行过程中的访问带宽,二可以做好访问隔离,尽可能的降低了芯片通路访问的复杂性和软件设计的复杂性。

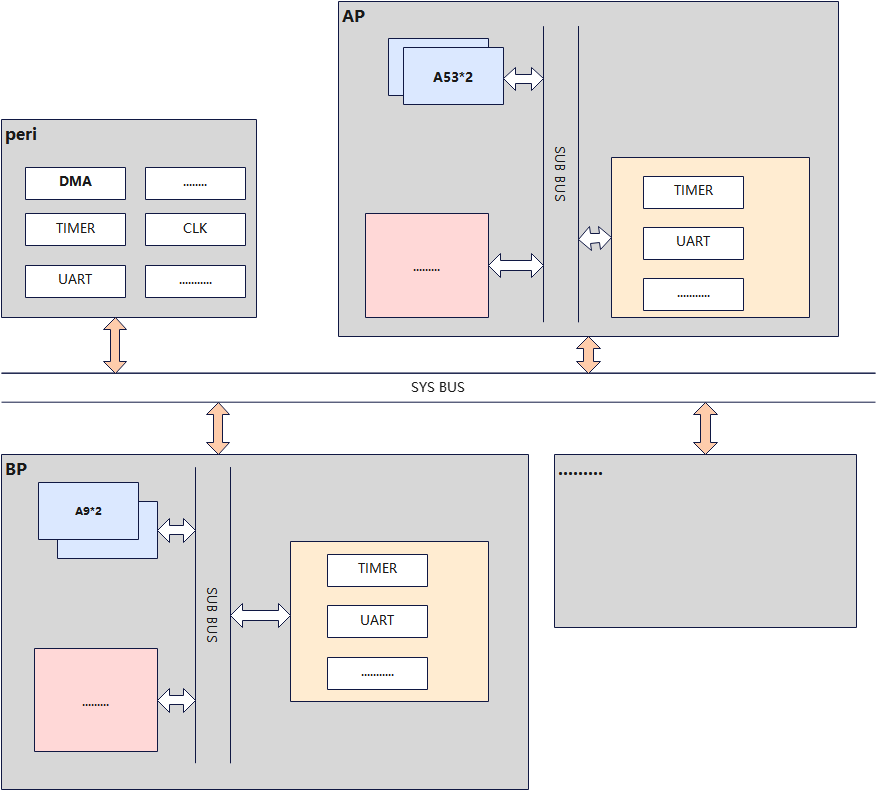

我们通过一个例子来说明一下:比如在一个系统中,只有一个DMA,存放在公共外设区(peri),这个时候如果AP需要访问DMA的话,那么它需要先经过自己系统的SUB BUS总线,再通过SYS BUS总线访问到外设区的DMA;如图19-1所示。

图19-1 DMA部署优化前布局示意

如BP需要访问DMA的话,那么它也需要先经过自己系统的SUB BUS总线,再通过SYS BUS总线访问到外设区的DMA;如此这般,其他子系统都是同样的访问路径。在这样的情况下,有2个缺点:一是访问路径过远增加了总线的繁忙程度,可能导致访问延时;二是可能存在资源竞争的发生,比如AP、BP或其他子系统同时访问的话,可能需要做仲裁处理。

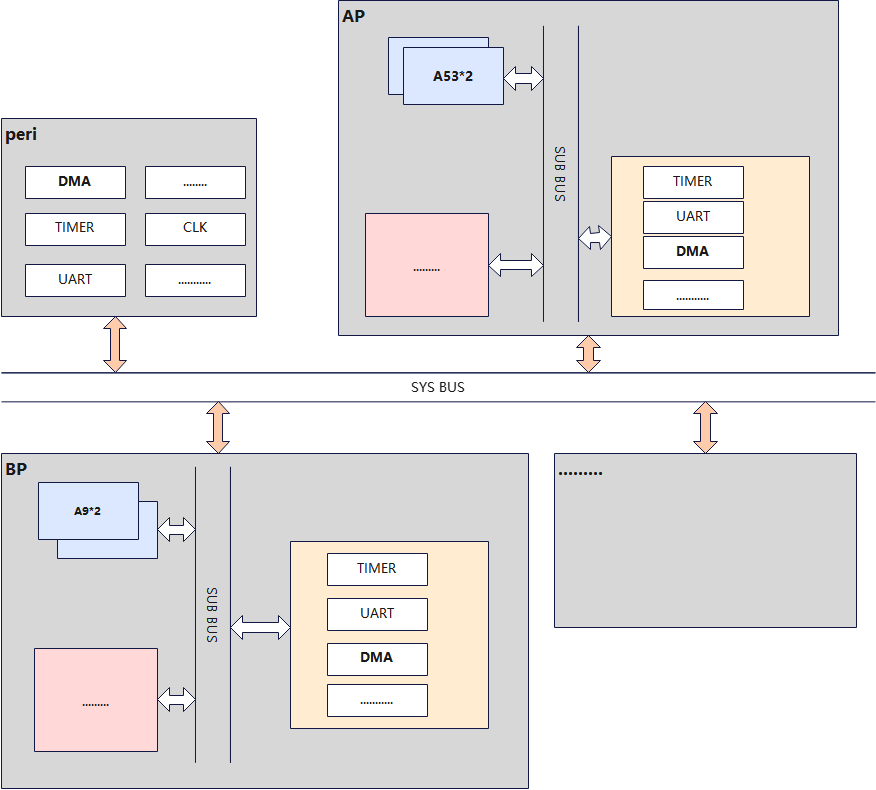

那么针对这种情况,我们可以做个优化,就是把DMA在每个子系统内部的device区各放置一个,如图19-2所示,各个CPU需要使用DMA时,只用访问自己内部的DMA即可,这样可以很好的化解前边说的2个缺点。为什么说这样设计也可以做到功耗优化呢?试想如果AP侧没有这个DMA,那么在AP侧唤醒而其他子系统都睡眠的情况下,AP侧如果要访问DMA,势必需要给其他子系统上电,从而带来功耗的浪费,而如果AP子系统内部本身就有DMA的话就没有必要给其他子系统上电。这个思想当然可以用在任何IP的归置上,需要根据实际的设计场景做对应的优化。

图19-2 DMA部署优化后布局示意

19.2并行处理

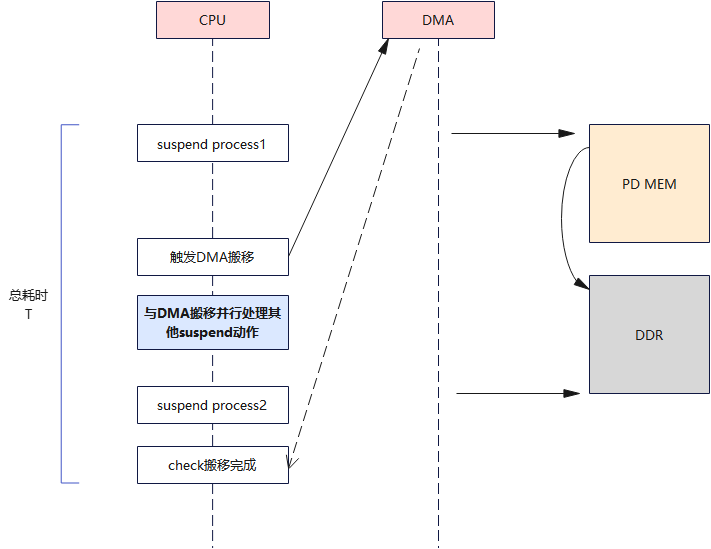

低功耗比较敏感的一个KPI是suspend和resume的时间,因为低功耗是系统中的一个常态,这一块的处理时间当然是越短越好,这样可以让用户体验更流畅。一个好的思想是让处理尽可能的并行起来,比如在suspend和resume的流程中,有一长段地址空间需要保存恢复,那么如果是用CPU的话,效率是十分低下的,这个时候我们可以使用DMA来搬移数据,同时CPU继续处理低功耗处理的其他流程,在合适的点来检查DMA的搬移状态。我们可以通过以下例子来说明。

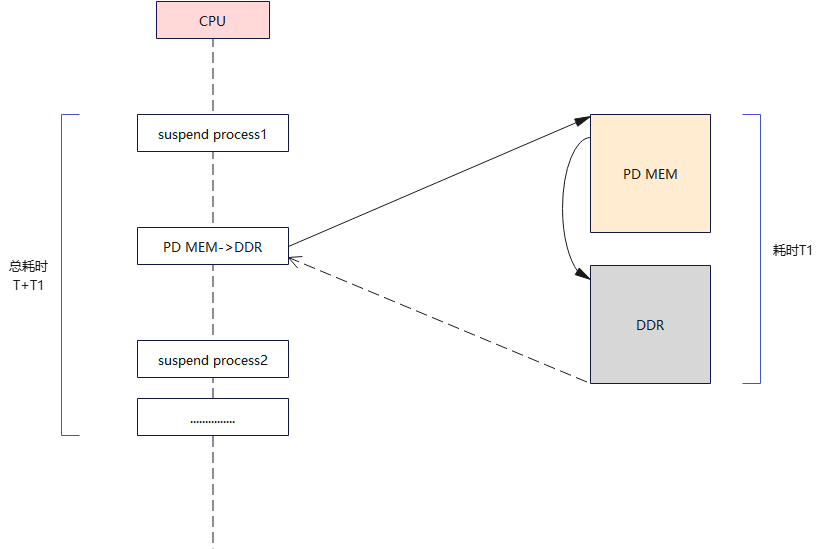

在suspend流程中,PD MEM中的内容我们使用CPU来做下电前的保存动作,如图19-3所示,把内容保存到DDR中,耗时T1,其他suspend处理耗时为T,那么suspend总耗时为T+T1,T1时长与PD MEM的大小强相关,越大耗时越长。

图19-3使用DMA搬移前

那么关于大内存保存恢复这一块,其实我们可以做一个优化,那就是不使用CPU进行处理,我们使用DMA去做搬移,CPU去做其他的suspend动作,那么T1这个耗时就可能会省下来,总耗时为T,从而达到时长优化的目的。如图19-4所示。

图19-4使用DMA搬移后

前边讲了suspend流程的并行处理优化思想,对于resume流程来讲,同样适用,就不再做过多阐述。

19.3增加打点信息

因为在低功耗流程中,会涉及到关闭时钟或者关闭电源等操作,很多debug工具是无法使用的,一个好的手段是在内存中划分一片区域专门用来给低功耗流程打点使用,打入数据通常是系统中递增的时间戳,这样有2个好处:一是可以方便查看各个阶段的耗时,二是可以根据时间戳的递增特性来快速的定位到哪一步出了异常。如图19-5所示。

审核编辑 :李倩

-

cpu

+关注

关注

68文章

10882浏览量

212242 -

soc

+关注

关注

38文章

4182浏览量

218521 -

内存

+关注

关注

8文章

3037浏览量

74151 -

低功耗

+关注

关注

10文章

2409浏览量

103783 -

dma

+关注

关注

3文章

565浏览量

100691

原文标题:SoC低功耗问题定位及优化的10个思路

文章出处:【微信号:LinuxDev,微信公众号:Linux阅码场】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于Kemet PL-N823-01和OnSemi RSL10蓝牙低功耗SoC

【书籍评测活动NO.19】 SoC底层软件低功耗系统设计与实现

《SoC底层软件低功耗系统设计与实现》基于Linux专门讲解软件低功耗框架和设计的书籍

SoC的低功耗设计

如何选择低功耗蓝牙SoC

DSP不同层次的低功耗设计研究思路综述

STM32芯片超低功耗设计思路

BlueNRG-LP支持128个并发连接的蓝牙低功耗SoC

超低功耗MCU的选型技巧与设计思路

功耗优化的片上系统(SoC)解决方案,引领低功耗蓝牙与2.4GHz应用新潮流

SoC低功耗问题定位及优化的10个思路

SoC低功耗问题定位及优化的10个思路

评论