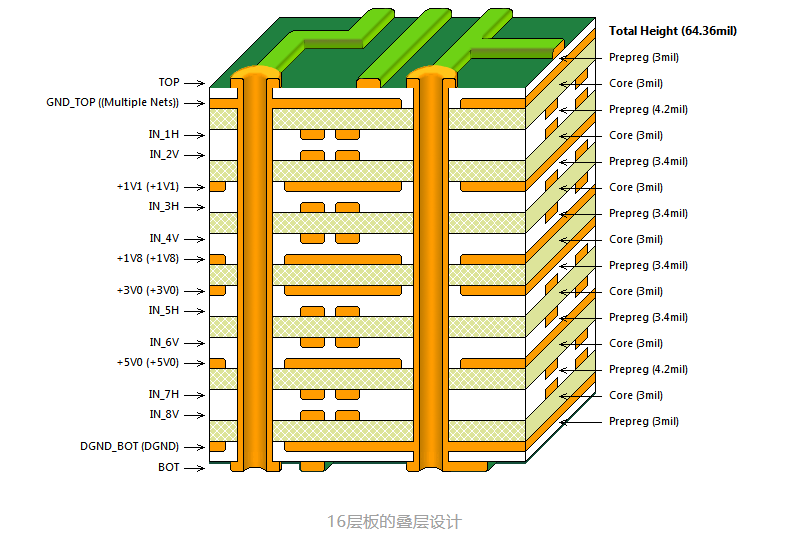

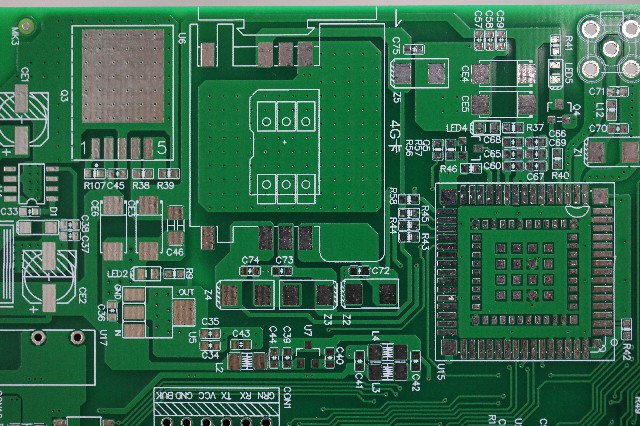

大家在进行PCB设计的时候都是需要对我们的板子选择叠层方案的,一个好的层叠方案能使我们的信号质量变好,板子性能也会更稳定等等,大家可能或多或少的接触过多层板,也就是两层往上的板子,那么大家在做六层板的时候是否有听过“假八层”的说法,“假八层”是什么意思呢?他到底是六层还是八层呢?我们在搞清楚这个问题之前需要先了解一下以下两个知识点。

01 PCB的叠层知识

我们的PCB板通常是有芯板,铜箔,半固化片(又称PP片)以及阻焊油组成的。

芯板:由铜箔、固态树脂材料和玻璃纤维组成,制作PCB的基础材料,具有一定的硬度及厚度,并且两个表层都有铜箔。

半固化片(PP片):主要由树脂和增强材料组成,增强材料又分为玻纤布、纸基、复合材料等几种类型,而制作多层印制板所使用的半固化片(黏结片)大多是采用玻纤布做增强材料。

02 PCB的阻抗基础知识

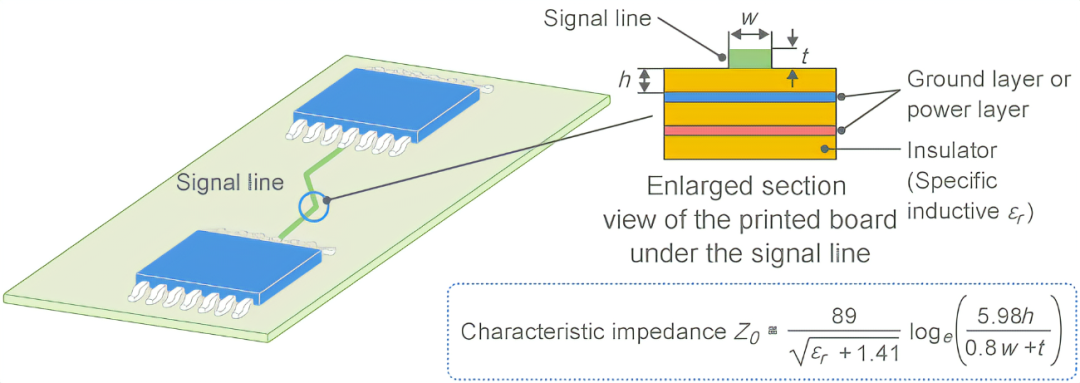

我们简单了解完我们的板子组成之后,下面还需要了解一个知识点,那就是“阻抗”。随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。印刷电路板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确、无干扰、噪音的传输信号。阻抗匹配在高频设计中是很重要的,阻抗匹配与否关系到信号的质量优劣 。而阻抗匹配的目的主要在于传输线上所有高频的微波信号皆能到达负载点,不会有信号反射回源点。

通常影响我们阻抗的因素主要有板材,介电常数,铜厚,阻焊油,线宽等等,如果是差分线那么差分线之间的距离也会影响阻抗。一般介质厚度,差分线之间的间距和阻抗成正比关系,铜厚,线宽和阻抗成反比关系,一般阻焊油刷上去也会减小我们的阻抗值。

我们知道这些知识之后就可以进入主题了,什么是“假八层”:

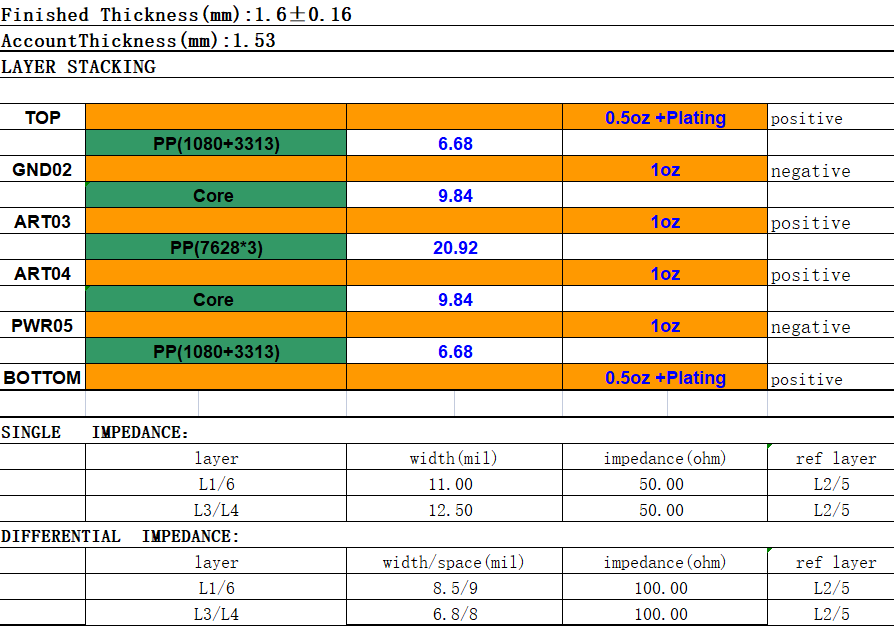

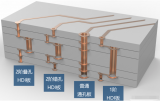

上图所示是一个1.6mm板厚六层板的叠层,他内部有两个芯板,一二层与五六层的pp片厚度为6.68mil,core厚度是9.84mil,芯板与芯板之间有三张pp片因此厚度达到了20.92mil,我们用此叠层设计PCB,如果我们板子上面有很多阻抗线的情况下这个时候我们经过计算会发现表底层需要控50om单端的情况下线宽是11mil,100om差分其线宽线距为8.5mil/9mil,而内层50om单端线宽达到了12.50mil,差分线宽线距为6.8mil/8mil,

这个线宽大小无疑增大了我们的设计难度,甚至很有可能设计不出来,所以我们可以通过更改叠层的方法实现降低线宽和满足阻抗的要求,从上面介绍的阻抗知识当中我们了解到介质厚度和阻抗值成正比关系,所以我们如果要减小表层的线宽则可以通过减少表层与第二层之间的pp片数量以及选用更薄的pp片类型来减小介质厚度,此时介质厚度减小,阻抗值也会随之小,那么这时可以减小线宽来达到我们的目标阻抗值,由于叠层的对称性所以底层也是通过此方法减小线宽。

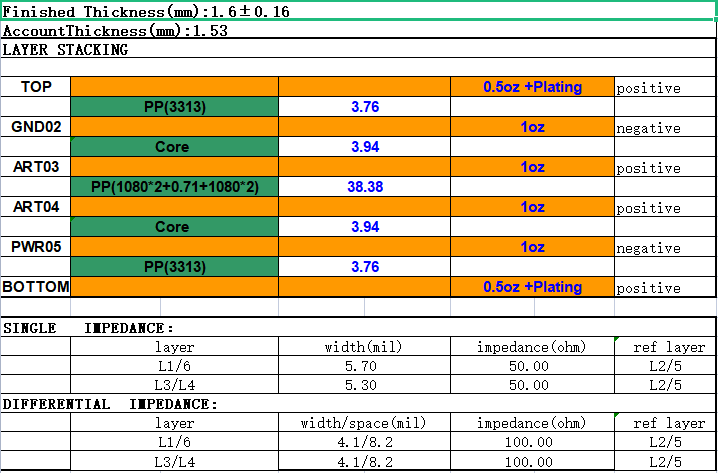

第三层是参考第二层和第五层的,其中第三层离第二层GND平面比较近,第五层离第三层比较远,我们主要是参考第二层GND平面,受第二层的影响多一点,所以我们可以通过更改芯板的类型减小core的值,介质厚度减小了,第三层的相同线宽的情况下阻抗值越小,那么我们要达到目标阻抗值也是一样减小线宽就可以了,这样内层也实现了减小线宽和满足阻抗的要求了,第四层也是如此,但是这个时候我们会发现,一二层和五六层之间的pp片都变薄了,芯板也变薄了,这个时候要达到目标板厚就只能在芯板与芯板之间增加厚度了,我们可以增加pp片的数量来达到增厚的目的,但是我们不能一直增加pp片的数量,一般最多只能用三张pp片,数量过多的情况下在板子压合的时候板子会出现滑片的风险,我们上面已经介绍了芯板和pp片的组成 ,都含有树脂和玻璃纤维,但是芯板的两侧有各有一块铜箔,我们可以在芯板与芯板之间再加一块“芯板”来满足我们的板厚要求,但是这块“芯板”我们是把两侧的铜箔是去掉的。新的叠层如下图所示

(假八层)

这时我们发现表底层的50om单端线宽是5.7mil,100om差分线宽线距为4.1mil/8.2mil,内层50om阻抗单端线宽5.3mil,100om差分间距为4.1mil/8.2mil

这个线宽对常规设计来说一般都是可以满足的,那么我们可以对比一下这两个叠层,你会发现他们之间的差异就是core是变薄了,然后一二层和五六层的pp片也变薄了,芯板和芯板之间多了一个两侧不带铜箔的芯板,那么一般这种叠层我们称之为“假八层”。

了解完他们之间的不同后那么我们也可以总结一下他们之间的优缺点:

1、在需要阻抗的情况下,我们采用假八层的设计可以减小我们的设计线宽,从而满足我们的设计要求。

2、在六层板叠层第三层和第四层走线的情况下采用假八层的设计可以减小第三层和第四层之间的串扰,因为第三层和第四层是相邻层,都要走线的话,两层之间太薄的情况下会产生串扰,影响信号质量,所以我们假八层的设计加大了这两者的距离,串扰会相对来说会比较小,但是我们也需要注意的是,有相邻布线层的情况下,我们要采用”垂直布线”,即走线一层走水平的,另一层走垂直的。

3、由于材料的增加从而导致我们的成本也会相应的提高,假八层是比六层贵的,但是比八层便宜。

以上就是本次要介绍的知识点了,相信大家在阅读完成之后对什么是假八层也有一个基本概念了。

声明: 本文凡亿教育原创文章,转载请注明来源!投稿/招聘/广告/课程合作/资源置换请加微信:13237418207 分享点赞在看“三连”支持!

点击“阅读原文”查看更多干货文章

分享点赞在看“三连”支持!

点击“阅读原文”查看更多干货文章

原文标题:PCB叠层当中的“假八层”是什么意思呢?

文章出处:【微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

-

pcb

+关注

关注

4319文章

23105浏览量

398071

原文标题:PCB叠层当中的“假八层”是什么意思呢?

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何根据贴片叠层电感参数进行选型

阻焊层解析:PCB的“保护伞”是什么?

谷景揭秘贴片叠层电感精度是不是越高越好

钙钛矿叠层电池:Topcon与HJT底电池性能对比研究

PCB叠层结构与阻抗计算笔记分享

PCB叠层设计优化ESD性能设计

PCB叠层当中的“假八层”是什么意思呢?

PCB叠层当中的“假八层”是什么意思呢?

评论