知道明德扬科教是一个偶然,但后来耐心看完明德扬知识大串讲系列视频却是一个必然。因为做得用心,所以看得放心。

本人是一个纯FPGA小白,就连FPGA这个名词我都是最近才知道,所以如果你也正想入门学习FPGA的话,请耐心看下去吧,相信你看完绝对不会后悔。

因为最近参加了一个集成电路类的比赛,需要用FPGA进行功能的实现,无奈我们专业目前还没有开设这门课,于是就只能自己开始着手自学了。经过我们老师的推荐,我第一次了解到了明德扬科教,了解到这样一个这么纯粹做技术和教育的机构,免费看完潘老师知识大串讲系列视频后颇有感触,下面我来向大家分享一下作为一个FPGA小白的学习经历吧!

首先大家可能会疑问学习FPGA需要什么基础知识,实话告诉你,基本不需要。我在学习FPGA之前除我们专业开设的模拟电子技术课外,自己只是自学了一下51单片机开发和数字电子技术的一些最简单基础的东西,最后发现用到的就是一个二进制和一些基本的门级电路知识,其次就是一种编程思维的培养,但我相信作为想学FPGA的你应该也多少具备一些这类知识吧。如果没有的话不妨简单看看吧。

视频的六个部分

知识大串讲系列视频一共由六个部分组成,分别是:学习误区、FPGA知识大串讲、组合逻辑、D触发器、时序逻辑和FPGA时序。每个视频针对性地讲一个小点,条理清楚,逻辑清晰,由浅入深,循序渐进,非常适合新手入门。这套视频不像其他有些视频一样很冗长,让人一看到视频的时长就望而却步,这套视频最长的不过半个小时,最短的也就五分半,让人看着不会觉得很枯燥。日常刷一个小视频的时间而已,而且还能学会很多东西,何乐而不为呢?

明德扬知识大串讲系列视频的知识体系

大家可能还会疑惑一个问题:在这么短的时间内真的能学到知识吗?

诚然,在如此短的时间内想要掌握一门技术有些不太实际,但我看完视频的经历告诉我,这套视频只要你认真看,理解潘老师讲的每一个细节,看不明白的地方就反复看看,再结合自己的理解思考一下,有些问题你就会恍然大悟。而且视频中有些言语非常地道幽默,所以也很让人容易理解接受。另外潘老师每个视频只针对一个小点进行讲解和分析,所以也很容易听懂,当然大家也不要有会听不懂的顾虑了。当然,对于能力比较强的初学者来说1.5倍速播放可能更适合你!

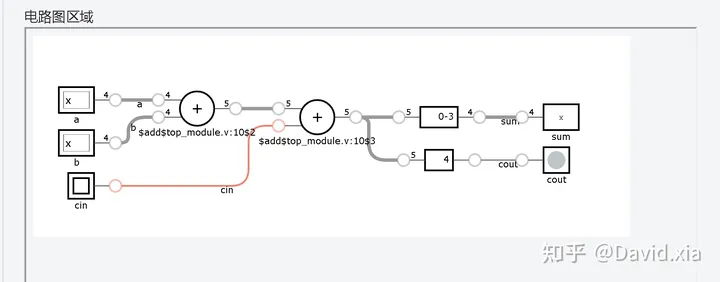

大家都知道,一个工程的好坏不在于代码量的多少,不是说实现一个功能用的代码越少越好。评价一个工程的好坏要看综合出来的电路,如果一个工程所在效率满足的前提下,所调用的资源最少、可维护性高、拓展性强、代码精简便于阅读,那么这就是一个好的工程。关于代码,潘老师在视频中也详细教了一些方法和思维,以下是我学习后的一些思考和总结。

不要试图用软件思维去编写代码。因为软件思维是在单片机编写程序时运用广泛的一种思维,主要通过一些串行或并行输出的代码去控制单片机处理一些问题,这样就会涉及到一些诸如延时和初始化这样的代码,但在FPGA中则不一样,在FPGA中是电路的反应,只要一通电就开始执行。在FPGA中也没有for循环和while循环、高阻态和不定态的说法。关于时序的功能都是通过时钟来实现的。FPGA是使用Verilog语言进行编写的,Verilog中文翻译又叫硬件描述语言,不是一种设计语言。所以我们在做一个FPGA设计之前,其实已经有硬件的电路结构在头脑里面了,我们只是用Verilog语言把它描述出来而已,绝不是用Verilog设计一门电路出来,这个思维模式是完全不一样的。

FPGA中是电路的反应

软件思维编写的代码可读性较差,而且和硬件思维编写的代码比起来运行的时候更耗时。

以下是两者实现一个摄像头输入模块采集功能的代码对比:

软件思维编写的代码

明德扬规范的代码

可以看出,两种思维的代码相形见绌。用软件思维写出的代码不仅结构冗长、可读性差,而且理解起来也比较麻烦。同样是实现一个摄像头输入模块采集功能,摄像头输入过来有三个信号:时钟、使能和数据。数据分别用两个字节的二进制数的值来表示一个像素点中RGB的值,我们主要做的就是把这两个值通过一个16bit的总线输入到下一个模块。软件思维就是定义一个变量进行加一运算,而明德扬规范中就用一个取反就解决了。这只是一个简单的例子,如果不够明显的话,接下来我们来看一个稍微复杂一点的例子。

现在我们需要实现一个帧频率的计算,统计两秒钟内输入帧的个数,然后把得到的数除以2就得到一秒钟的帧频率。下面我们来一起看看这个功能用两种不同代码实现的区别:

软件思维写出的代码

明德扬规范的代码

大家不难看出,用软件思维写出的代码不仅繁杂,理解起来也比较困难,而明德扬规范的代码则显得更简洁、高效,效率也是不可同日而语的。

另外我们还不难发现一点,潘老师和明德扬规范的代码结构和语法非常简单,很多语法几乎都只是用得到了if和else这些最简单的语句,所以我们在学习语法上其实不用花费太多的时间,这也为我们新手入门降低了很多难度,节省了很多宝贵的时间。

明德扬规范的代码结构和语法

另外潘老师个人讲课也比较有特点,虽然潘老师普通话不是特别标准,但这并不影响我们对于知识和思维的学习。

潘老师研发经验非常丰富,曾在华为这种世界500强的公司工作过,做过很多项目的开发,所以实战经验丰富,讲的很多东西实用性比较强。特别是对于我这种是抱着参加竞赛的小白来说帮助很大。

我们都知道,想要提要时钟频率就要减小时钟周期,但因为D触发器和线路之间传递的那部分延时是由物理器件决定的跟器件的工艺和材料等因素有关,我们没办法进行修改,我们能做的就是对组合逻辑那部分电路的延时减到最小。这条把延时减到最小的路径也叫关键路径。

关键路径

老师在一开始就讲过在FPGA里面的电路是一通电就可以工作,指的是对于最基本的门电路而言的。于是老师就举了他在海思里面做项目的一个例子:要把一个集成电路跑到2G的频率!可想而知这需要多么小的时钟周期,他们的方法就是把所有能拆的组合逻辑都拆成了基本的门电路,甚至连选择器他们也不放过,只为了一步步提高频率。就这样一直不停地拆,直至把任何两个寄存器之间的延时缩小到最小最小,从而达到就可以达到提高时钟频率的目标,这个方法也叫流水线设计。

减小时钟周期

潘老师讲课还善于联系现实生活进行分析。在讲到关于状态机的设计时,为了将状态机设计的目和过程一目了然,于是便联系生活讲到了我们日常生活中常见的自动售货机的设计。

自动售货机的设计

并且还就这个例子讲到了代码设计的三段论格式,让设计代码显得非常实用高效,便于分析。

自动售货机代码的设计

总而言之,看完整套视频后,作为一个小白的我感觉对于FPGA有了一个大概的了解了,让原本在门外徘徊的我慢慢地就走进了门里。在这里常感谢明德扬科教提供的这个让我免费学习的机会。

以上就是我看完明德扬知识大串讲系列视频后的一些收获和总结,希望能给同样热爱学习的你带来一些启发!也让我们在学习FPGA的道路上共同进步吧!

审核编辑:汤梓红

-

FPGA

+关注

关注

1626文章

21665浏览量

601793 -

单片机

+关注

关注

6032文章

44514浏览量

632919 -

时序逻辑

+关注

关注

0文章

39浏览量

9146

发布评论请先 登录

相关推荐

FPGA学习笔记-关于FPGA资源

FPGA基础知识学习

FPGA初步学习印象

FPGA学习资料分享

小白学习FPGA的四大误区

从入门到放弃……为什么你会觉得FPGA难学?如何学习FPGA?

【学习FPGA必看】一个FPGA小白的自述

【学习FPGA必看】一个FPGA小白的自述

评论