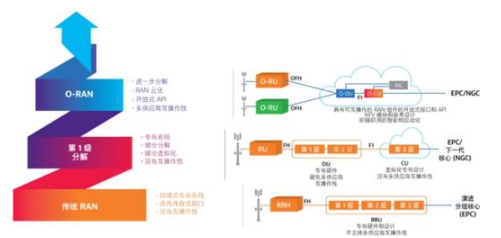

O-RAN的创建是为了改变无线社区的催化剂,以 启用无线设备的新渠道,并使创新得以实现 3GPP对5G的承诺。1为了成功和具有成本效益, 无线设备的开源和优化的 5G 技术设备 必须可用。本文将回顾其中一种设计解决方案 并构建高能效解决方案。

5G 挑战是什么?

无线电和网络工程师正在使用几种技术来 实现这些目标。除了将数据服务移动到网络边缘, 大规模MIMO和小型蜂窝技术的利用有助于提高两者 容量和吞吐量。大规模MIMO技术利用大量无线电 阵列不仅实现了容量,还实现了对中心位置的覆盖。喜欢它的 宏蜂窝的前身,大规模MIMO无线电将提供相对广泛的 覆盖该位置周围。然而,大规模MIMO无线电被放置在更高的位置 频率,通常为 2.6 GHz 及以上,不能很好地穿透建筑物。 为了服务室内场所和其他难以到达的室外区域,小型蜂窝 将被利用。考虑到室内和室外位置的数量,范围从 家庭到企业安装到商业购物区甚至 竞技场上,小基站的利用对于5G的成功至关重要。鉴于浩瀚 网络中所需的小基站数量和部署多样性,它们 安装和操作必须成本低廉;这将是5G的关键推动因素。

有哪些可用的技术?

在过去的几年中,多种技术朝着一个方向发展 这为5G提供了解决方案。首先,从基带的角度来看,摩尔的 Law不仅继续降低每个栅极的硅成本,而且能够实现更多 集成到无线电技术中的复杂功能。现在可以 将许多所需的控制算法直接集成到无线电中,包括 数字预失真 (DPD) 等功能。许多其他可能性作为新存在 一代又一代的无线电变得可用。

二、O-RAN等产业联盟2正在整个无线行业工作 实现规模经济,不仅降低成本,而且改善供应 链安全,并提供通过这些无线网络获利的新方法。 具体来说,“O-RAN联盟是由运营商创立的,旨在明确定义 要求并帮助建立供应链生态系统以实现[其]目标。

为了实现这些目标,O-RAN联盟的工作将体现” 开放和智能的原则。3因此,他们的活动侧重于定义 3GPP 指定的物理接口,以便对其进行标准化和 作为可互操作的白盒解决方案在整个行业中实施。此外 O-RAN还定义了硬件要求,并为以下方面提供了参考设计: O-CU、O-DU 和 O-RU(开放式集中式单元、开放式分布式单元和开放式 无线电单元,分别由 O-RAN 定义)。这些将共同使 前传和基带处理器的标准化,以进一步减少解决方案 成本。与其他集成5G设备(如集成无线电)一起,这些可以 用于定义小蜂窝将成为什么以及实现 这些标准。这些机构的工作是关键的一步。

第三,无线电技术在过去几年中迅速发展。高性能 无线电现在有多种格式可供选择,能够满足所需的要求 3GPP 在 38.104 和相关文件中要求的性能标准。1这些无线电高度集成,不仅包括模拟和射频组件 但关键算法,如DPD和波峰因数降低(CFR)。虽然这些 无线电建立在细线CMOS上,RF中发生了其他演变 低成本射频工艺(SiGe、SOI、GaN、GaAs等)正在生产的前端 高度集成的LNA和高功率、高性能PA,可满足 挑战这些标准的要求。

最后,高度集成的高效电源解决方案,包括供电 以太网 (PoE)、标准功率设备、监控和保护 解决方案—可提供紧凑的电力传输。这些解决方案 在无线电环境中提供非常高的效率和非常低的噪声,包括 为功率放大器等关键设备提供保护的选项。

这些技术共同实现了低成本、高性能的小型蜂窝。 可以有效地部署在整个运营商网络中的平台 低功率和高功率系统。

系统概述

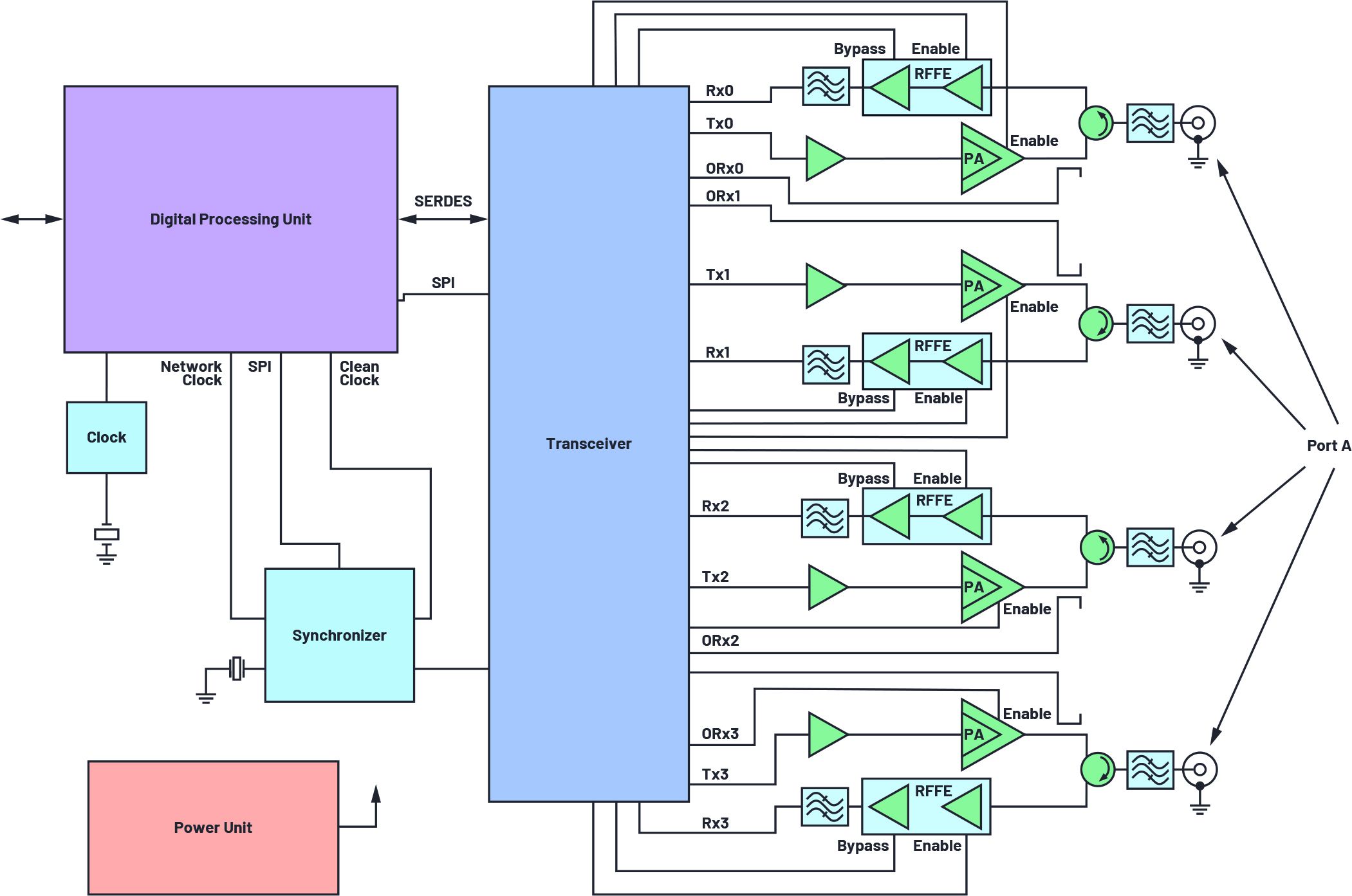

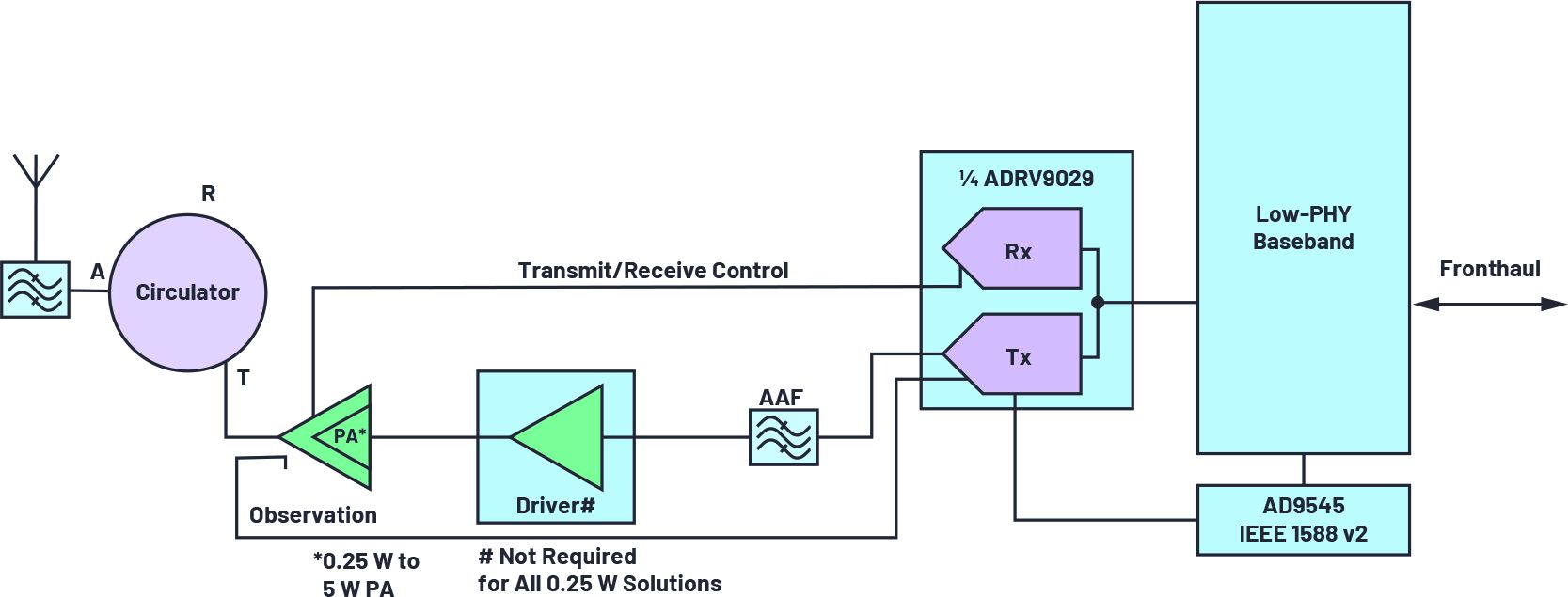

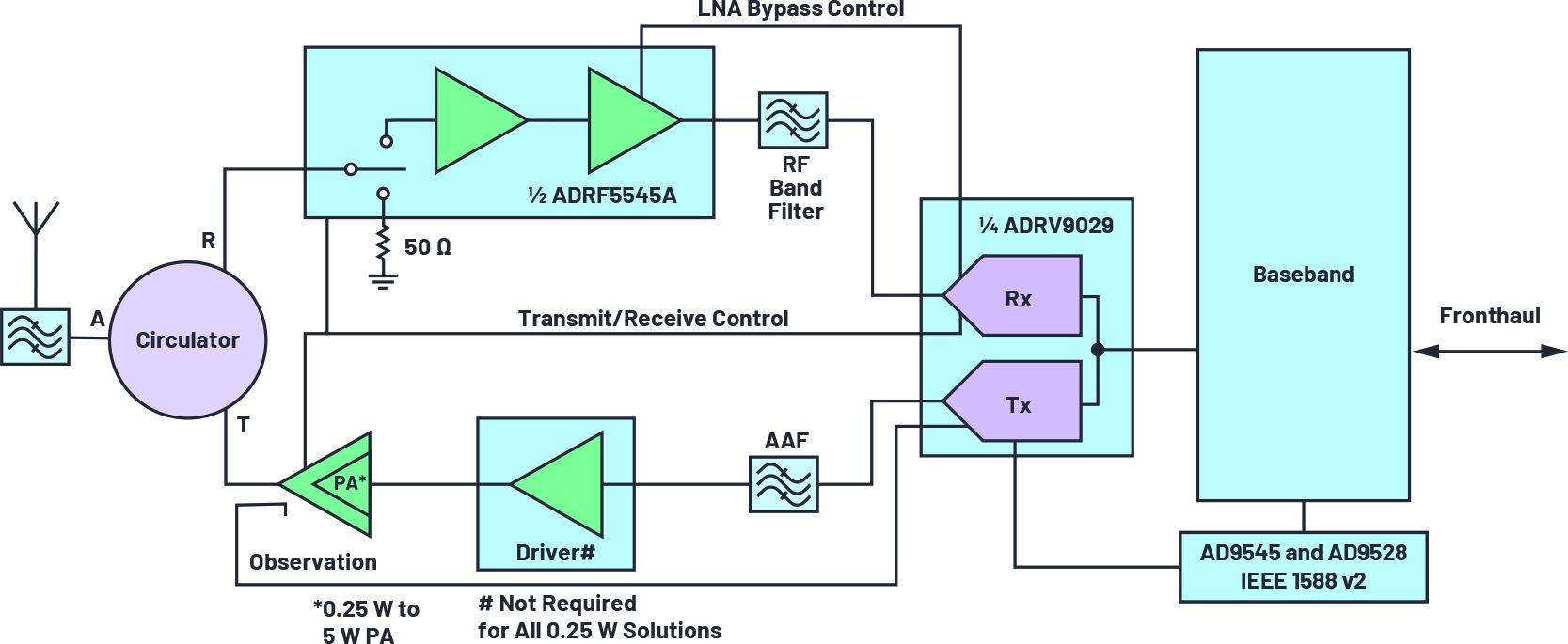

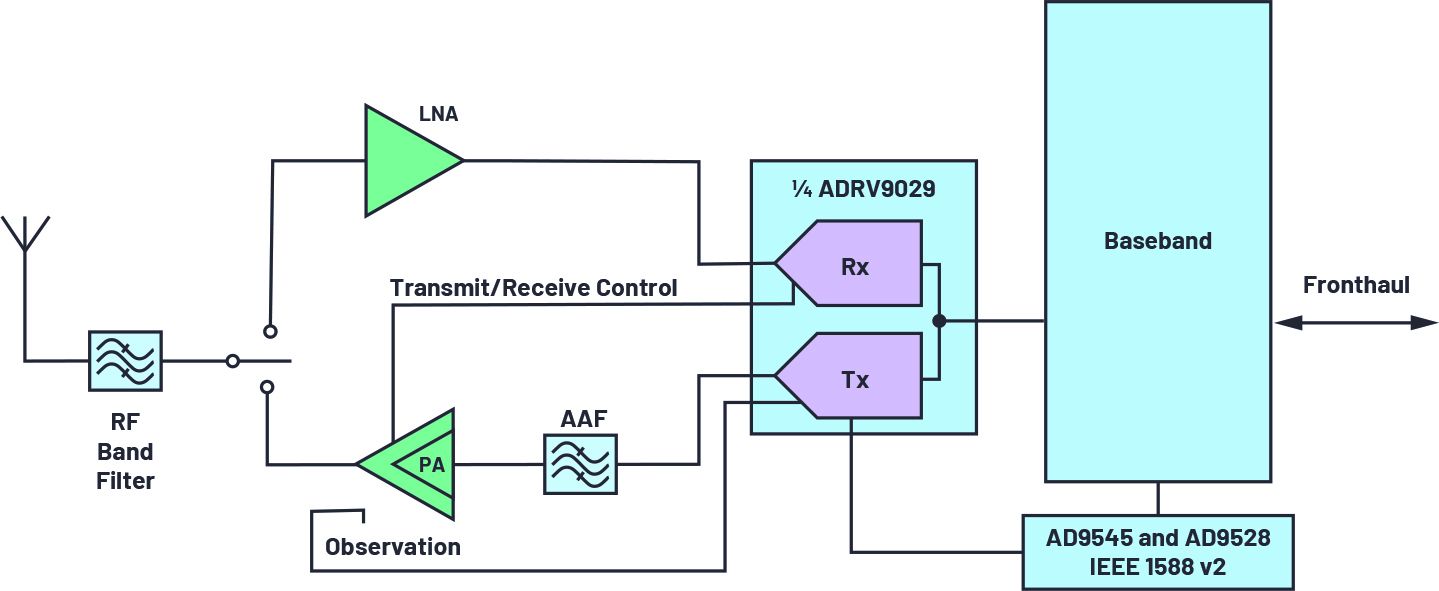

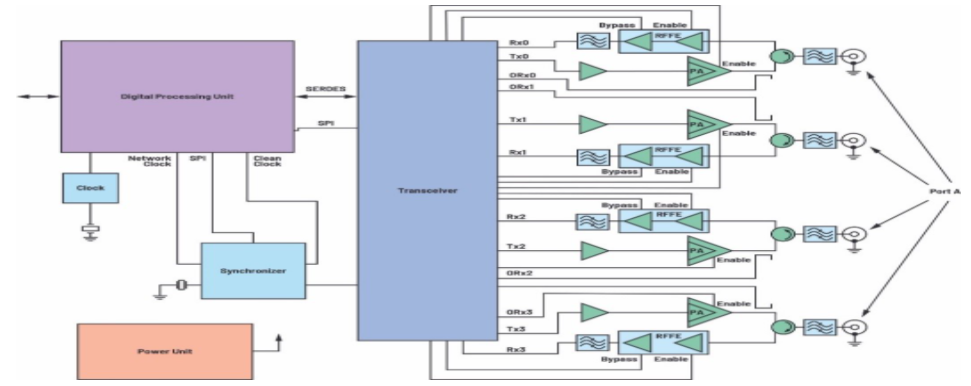

图 1 显示了典型的 4T4R(四个发射器和四个接收器)5G 小型蜂窝 方框图。有许多可能的排列,包括 2T2R 和范围 功率等级从 24 dBm 或更高。这个数字将成为 讨论的其余部分,重点是易于操作的5G技术设备 针对 O-RU 内的频段和功率电平变化进行缩放。

图1.小型蜂窝高级框图。

关键无线电元件

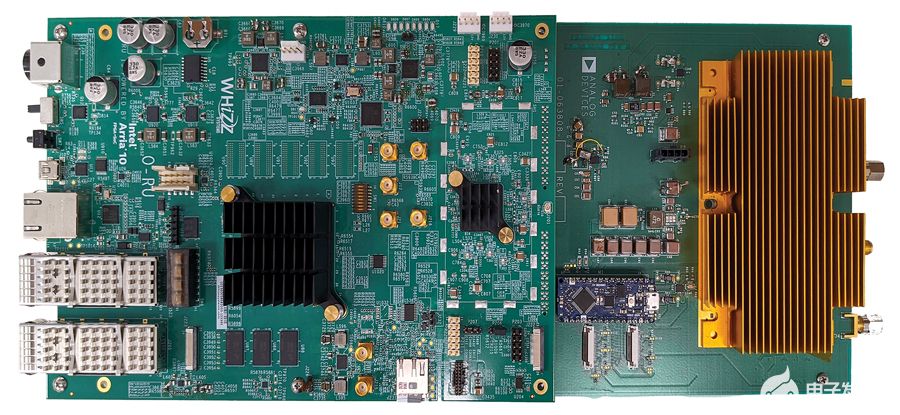

在过去十年中,集成收发器已经成熟为高性能平台。ADI电台™系列包括广泛的集成 收发器支持高达 200 MHz 的占用带宽,集成 DPD 等高级功能。总之,该系列产品不仅满足 需要5G技术设备,同时也持续支持LTE和多载波 GSM 射频要求。虽然新一代的这些设备总是在 开发,最新的之一如图2所示,ADRV9029,一款4T4R 配置。其他产品包括带和不带的设备 集成 DPD 和其他配置,包括 2T2R。

图2.ADRV9029收发器。

每个RadioVerse设备都包含构建完整设备所需的一切 无线电,除了LNA和PA。这包括传输和 接收、合成器和时钟。它还包括状态机和VGA。 需要运行AGC和增益控制放大器。虽然无线电宇宙产品 都是高达 6 GHz 的宽带,LNA 和 PA 不是,必须由 频段或频率范围。因此,要完成对讲机设计一个合适的 LNA 和 PA 必须与 RadioVerse IC 配对。以下部分将 描述 5G NR 小型接收和发送的信号链 单元设计,并深入了解这些设备的选择。

接收器信号链示例

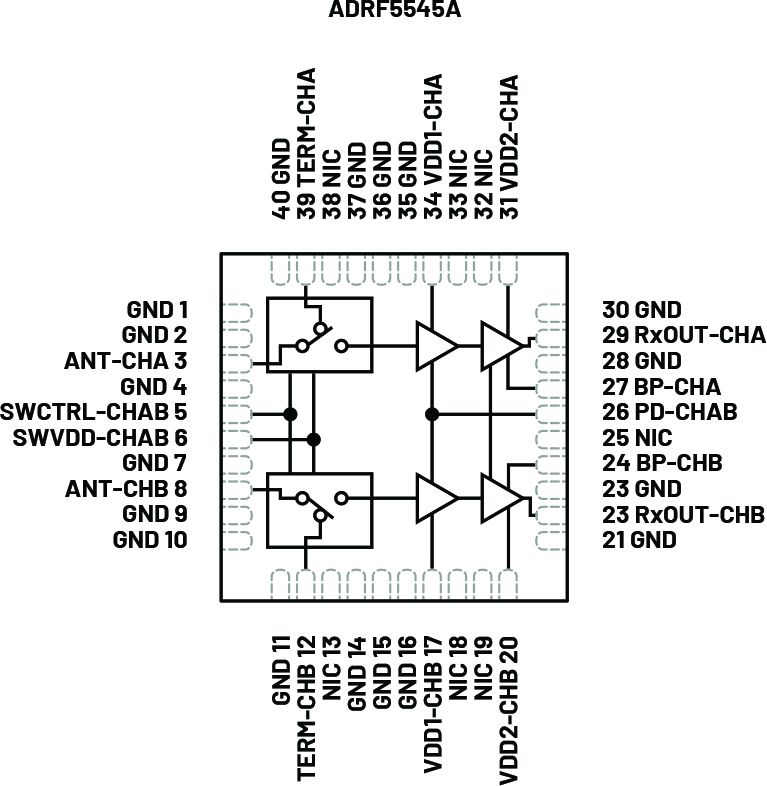

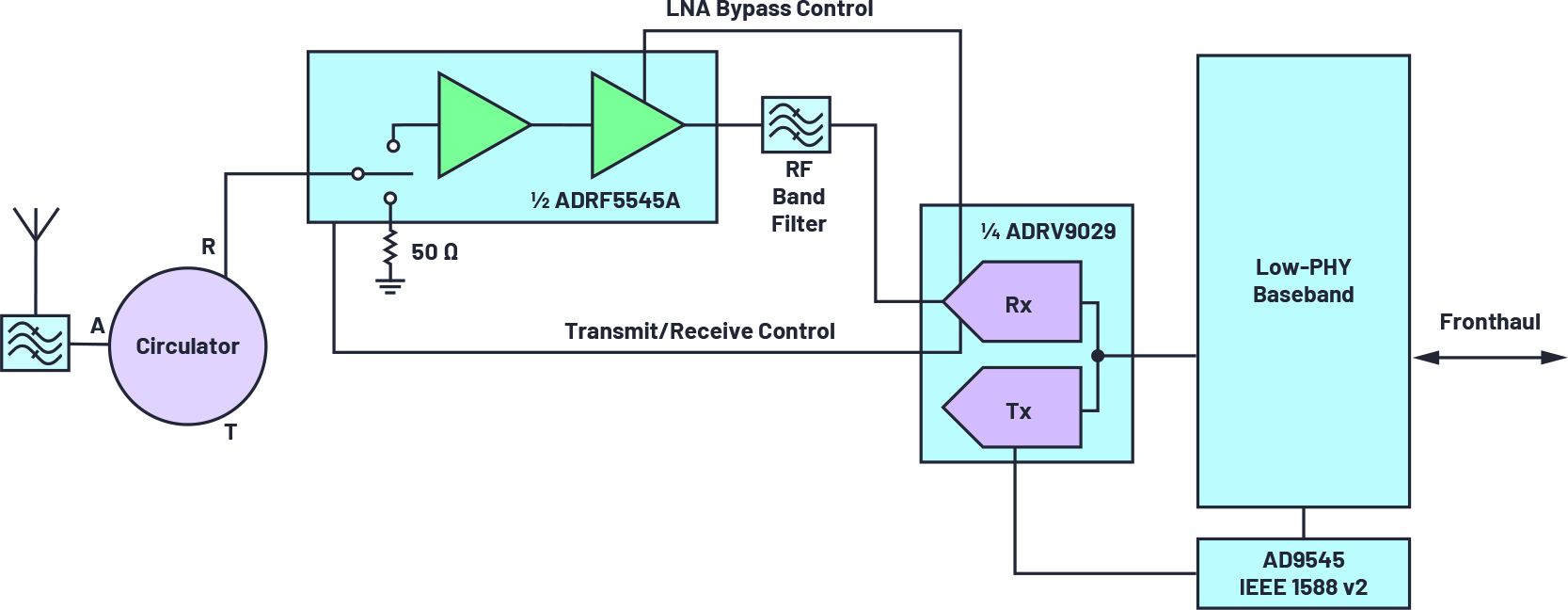

如图3所示,当ADRV9029与ADRF5545A结合使用时,a 2芯片接收器易于构造。ADRF5515引脚兼容,可以 也可以使用。仅与少数其他无源元件结合,可以形成 信号链中所示的非常紧凑的高性能接收器设计 在图 4 中。这种架构的主要优点是高度集成 可能,这不仅导致成本非常低的实施,而且导致 可实现最低功耗。4

图3.ADRF5545A双通道TDD接收器前端。

图4.接收器信号链详细信息。

RadioVerse系列的架构消除了许多元素 通常与经典的接收器设计相关联,包括一些RF。 放大、滤波和集成大部分剩余的无线电功能, 包括通道滤波器(模拟和数字)和基带放大器。这些是 通常是系统中一些最大和最高功率的器件,这导致 与直接射频采样等其他架构相比,可显著节省成本。

如图4所示,小型蜂窝接收器阵容由一个环行器(用于TDD)组成 应用), ADRF5545A, 锯/波(表面声波/体声波) 或单体滤波器、巴伦和收发器。附加放大器或 VGA 不是 考虑到ADRV9029的良好噪声性能和低输入IP1dB,这是必需的 以及RadioVerse家族的其他成员。使用该信号链,可以 从天线支持整个系统的低至 2 dB 的噪声系数 到位。虽然此设计包括一个集成的射频前端模块 (FEM),但许多 设计仍将受益于此处未表示的分立设计。集成的 FEM 以集成为代价,以略微增加天线中的滤波器要求 过滤器,但仍为许多高度集成的解决方案提供引人注目的设计,例如 作为大规模 MIMO 和其他 TDD 部署。通常,分立式前端 用于FDD设计。

假设LNA之前的损耗约为0.5 dB,并且如果带式滤波器的损耗 为1 dB,给定两个有源器件的数据手册规格,标称噪声系数为 完整的接收器信号链应约为2 dB。假设信噪比和失真比与MCS-4一致,基准灵敏度将 对于 G-FR1-A1-1 5G 载波 (~5 MHz),约为 –104.3 dBm。这应该不止 足以满足本节中显示的广域传导要求 7.2.2 的 38.104 有余量空间,对于本地来说绰绰有余 面积/小基站设计,在此条件下需要 –93.7 dBm 如下所述 在表 1 中。一些低性能的小型蜂窝应用可能能够利用 单级LNA,如GRF2093,后跟SAW滤波器。

| 广域(分贝) | 中量程 (分贝m) | 局部区域(分贝) | |

| 5兆赫带宽/15千赫 | –101.7 | –96.7 | –93.7 |

| 20兆赫带宽/15千赫 | –95.3 | –90.3 | –87.3 |

| 50兆赫带宽/30千赫 | –95.6 | –90.6 | –87.6 |

| 100兆赫带宽/30千赫 | –95.6 | –90.6 | –87.6 |

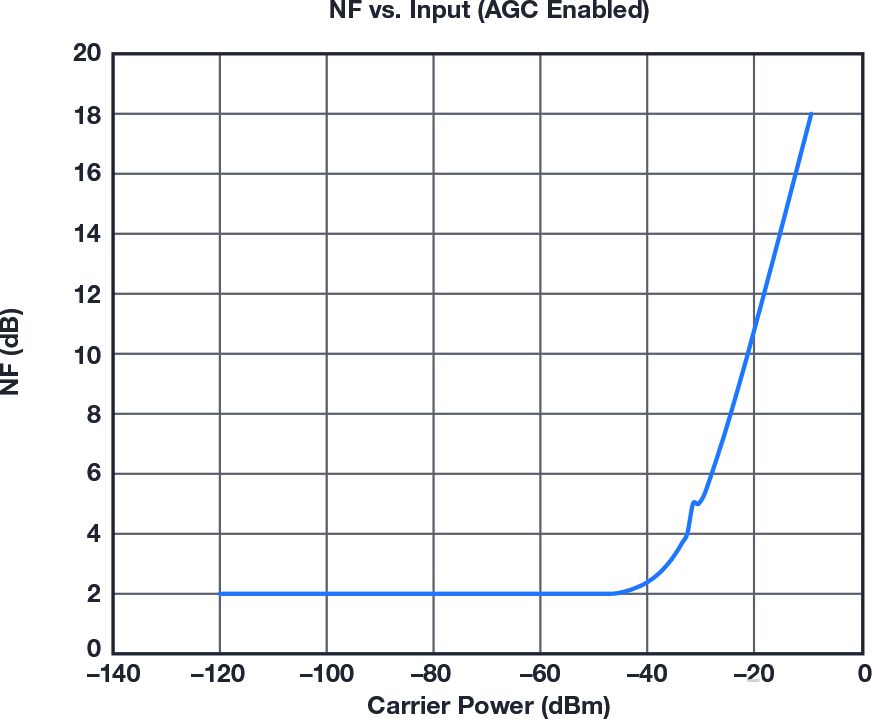

此外,38.104 第 7.4.1 节要求低于 –52 dBm(广域)的 ACS 阻止接收器的灵敏度不超过 6 dB。基于 NF 与输入 电平如图5所示,–52 dBm处产生的附加噪声比在–52 dBm处产生的噪声非常小 较低的级别。事实上,本底噪声直到–40 dBm之后才会向上倾斜, 非常适合需要 –44 dBm 容差的局部区域 ACS。

图5.接收器 NF 与输入电平的关系。

一般阻塞要求 (7.4.2) 要求侵略者为 –35 dBm(局部区域) 以 ±7.5 MHz 的偏移量施加到目标频带内的接收器 允许的降敏不超过 6 dB。图5显示了ADI公司 信号链性能方面,仅发生约0.9 dB的降敏。窄带 阻塞是一种功率稍低的类似CW的刺激,但也不是问题。

也许一个更有趣的挑战是带外阻塞 第 7.5.2 节.在这里,–15 dBm的信号被传递到天线输入端。对于一个小 小于 200 MHz 的单元,此信号最接近频带边缘的信号为 20兆赫。该测试需要从 1 MHz 到 12.75 GHz 的扫描,不包括频段 在工作频率的 20 MHz 以内。有几件事有效 这对信号链的优势。首先,环行器的带宽有限 并且会拒绝许多带外信号,但接近它并不是一个大贡献者。 其次,ADRF5545A后面所示的滤波器将提供一些滤波,通常: 20 MHz带外~20 dB抑制是合理的。最后,一个独特的 以及ADI收发器系列中最有用的特性,这是收发器固有的 架构,是内置的带外抑制。图20来自ADI公司的 应用笔记AN-1354,固有带外抑制表现为: 增加信号电平以降低接收器的灵敏度。在本应用笔记中,扫频 通带周围任一方向的频率表明信号越大 对于相同程度的脱敏是可以容忍的。在应用说明中,我们看到 在频带边缘附近,6 dB 降敏可能达到约 10 dB。除此之外, 集成滤波器可显著滚降带外信号,不会混叠回 带内,并且在很大程度上被片内和外部滤波衰减。

这些模块共同将 –15 dBm 带外侵略者滤波至大约 –40 dBm 至 –45 dBm,最高可达 20 MHz 排除频带。更远,甚至更大 将假定拒绝。在这个级别上,图 5 显示的降敏效果非常小 是意料之中的。

也许更大的问题是前端模块的线性度。此时 水平,可以预期一个重要的IM3产品。取决于实际有限元 选定后,可能需要在第二个波段选择滤波器之前移动波段选择滤波器 LNA,保护其免受带外信号的影响,这些信号通常会产生较大的IM 产品。不可能在这些类型的阶段之间放置过滤器 的 FEM,因此实施了替代选项。

为了帮助限制大型带外阻断器下互调的影响,a 典型的 FEM 包括第二级旁路开关,以降低增益并保护 第二阶段从驱动到非线性,如图3所示。 切换LNA增益可将信号链SNR降低1 dB,但有助于保持 通过限制由这些引起的互调失真来获得整体动态范围 大型阻塞器,远远抵消了噪声性能的损失。总的来说,这个 将导致最坏情况下的NF约为5.7 dB,这仍然在局部区域内 基准电压源灵敏度的(小蜂窝)占位面积要求。任何剩余的过滤器 要求由天线滤波器提供,并可确定抑制 基于接收器FEM的低增益压缩点和IP3。

发射机信号链示例

当ADRV9029与合适的RF驱动放大器或RFVGA结合使用时 (访问 analog.com/rf 了解更多选择),以及合适的PA,紧凑型室内微微蜂窝, 室外微蜂窝或室外微蜂窝5易于构造。只有少数 其他无源元件,这些5G技术器件可以组合形成 非常紧凑和高效的变送器设计,如 图6.这种架构的主要优点是高度集成 可能,这不仅导致成本非常低的实施,而且导致 通过利用集成的DPD功能实现最低功耗 在部分ADI收发器上可用。

图6.发射器信号链详细信息。

如图6所示,小型蜂窝发射器系列由环行器PA、 滤波器和收发器。此外,该电路在输出端包括一个耦合器 用于监控输出失真的PA(也可用于 监控天线的驻波比以及正向功率),并可用于 DPD提高传输功能的运行效率,提高 杂散性能。虽然可以使用外部DPD,但可以选择ADI收发器 包括完全集成的DPD,其工作功率为350 mW或更低 取决于给定PA所需的校正量。低功耗 PA 将 需要较少的校正,因此DPD消耗的功率更少。另外 集成的DPD将SERDES通道的数量减少了一半,即 外部基带芯片作为观察接收器SERDES通道被消除 考虑到带宽扩展,完全减少发射器有效载荷 DPD完全在收发器内处理。等效的 DPD 在 FPGA 通常具有 10× 的高功率,并且对于 低功耗小型蜂窝和大规模 MIMO。但是,通过将DPD集成到 收发器,极低的功耗和小的成本效益使DPD能够 甚至用于低功率小型电池,从而获得效率和 提高发射线性度,无需繁重的外部计算负担。

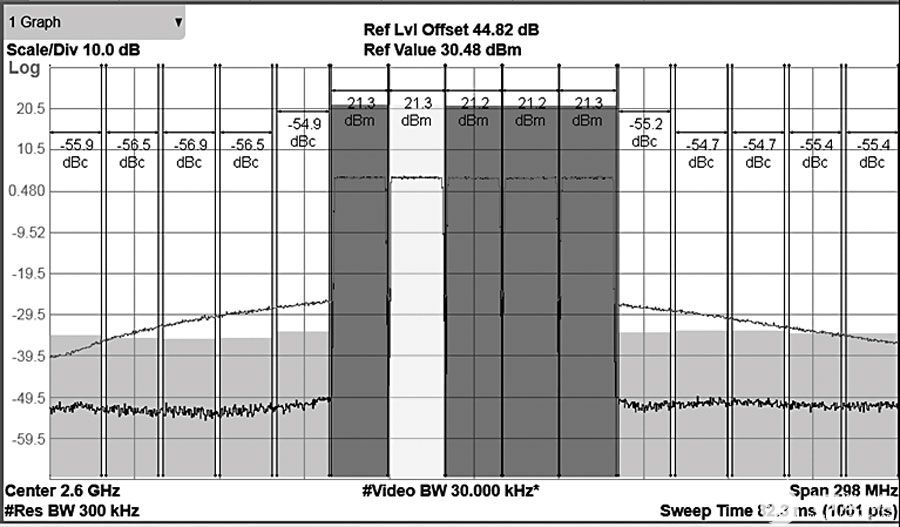

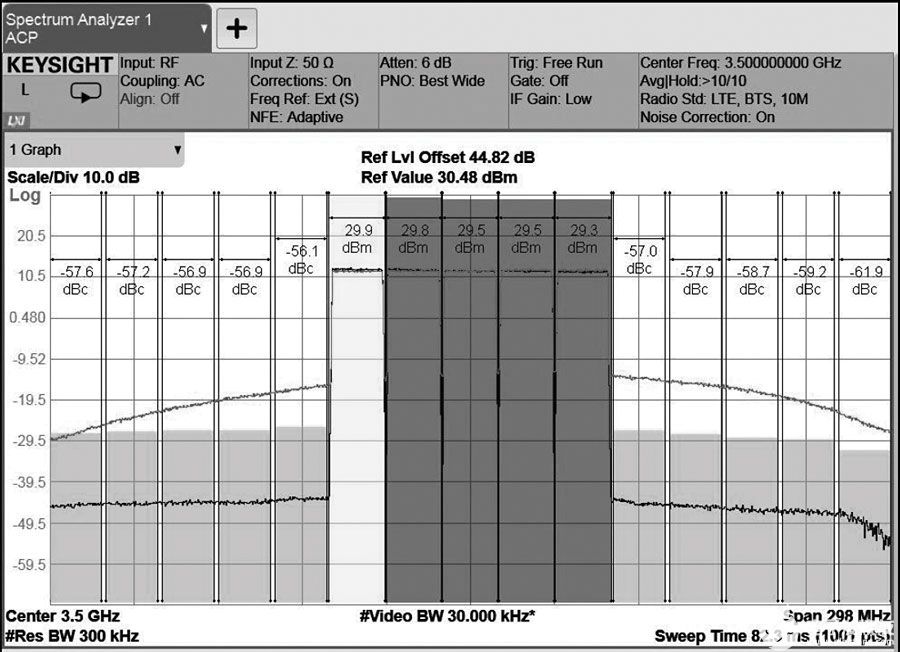

图7和图8显示了ADI的DPD在中低端工作的示例 为小型蜂窝应用供电。所示激励针对五个相邻的 20 MHz LTE 总频率为 100 MHz 的载波。 通常,LTE 至少需要 45 dB ACLR 预计大多数部署将获得更多。ADI进行持续测试 实验室始终审查所有功率等级的新PA。检查功率放大器 测试报告,或咨询工厂以获取有关可用DPD技术的最新详细信息 来自ADI公司以及最新合格PA的列表。

图7.带或不带DPD的典型PA频谱总RF为26 dBm。

图8.带和不带DPD的典型PA频谱总RF为37 dBm。

这一切是如何结合在一起的?

图9显示了完整的信号链,包括一些所需的控制信号。 为了提高功率效率,该电路包括发送和接收信号,使能 并在各自的TDD周期内禁用放大器。同样,这个 可与FDD一起使用,在未使用的插槽期间关闭电源以节省电力 也。还需要LNA开关才能将LNA上的输入开关更改为 将任何返回的发射功率分流到终端而不是内核放大器 输入。这些不同的信号可以由ASIC生成和编排, FPGA 或收发器。

图9.完整的收发器信号链。

接收器信号链包括一个相应变化的功能 数字数据流用于解释模拟增益的降低,从而保留 绝对信号电平,因为它被传递到低 PHY,然后传递到其余部分 的基带下游。

此处显示的应用程序适用于单频段。当收发器是宽带时 并涵盖高达 6 GHz 的所有频率,但并非设计中的所有设备都能覆盖。设备 像LNA和PA通常是带状的,需要根据频段进行选择 支持。通常,这些器件提供引脚兼容选项,以 覆盖 6 GHz 以下的所有常见频段,易于更换。这使得 支持所有流行的TDD和FDD频段,包括5G频段和那些 建议用于 O-RAN。

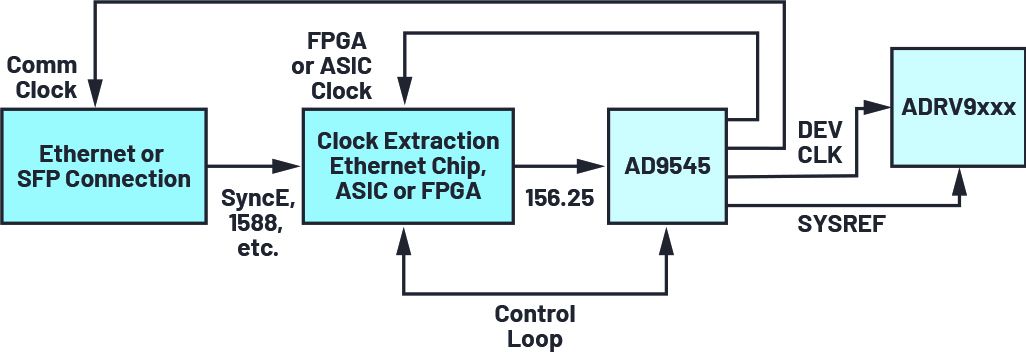

时钟树

根据配置的不同,可以有几种不同的时钟配置。 如果需要精确的时序对齐,则将进行 2 级时钟合成 必填。第一阶段需要通过ASIC连接到基带, FPGA或控制器,用于正确计时和对齐无线电数字化。此应用程序 将需要处理由 前传方式或本地 GPS 接收器。这将确保收音机和 基带处理器确切地知道何时应处理无线电帧。

AD9545系列非常适合精确调整频率、相位和 主时钟到收音机的时间。它的好处是可以配置 在没有参考的情况下临时操作并保持情况下的准确性 与TCXO(温度)耦合时有故障或间歇性的参考时钟 补偿晶体振荡器)或OCXO(烤箱控制的晶体振荡器)。

对于不需要精确时序对齐的配置,或作为 第二阶段,需要一个时钟分配设备。这 分配设备的目的是在整个时钟范围内生成时钟范围 收音机。这包括 JESD、eCPRI、以太网、SFP 和其他 整个无线电的关键信号。AD9528提供低抖动时钟,总计 多达 14 种不同的速率,包括支持 JESD204B/JESD204C 器件 时钟和系统参照信号。

两级时钟框图如图10所示。对于不这样做的应用程序 需要精确的时序对准,AD9545可以省去或旁路 并且仅使用AD9528。系统的输入时钟来自 基本网络定时,由基带和网络功能恢复 以太网功能块或 FPGA 内,具体取决于确切的 建筑。根据特定的 无线电的要求,此处仅显示表示形式。

图 10.时钟树示例。

权力

汇总总功耗由许多因素决定。其中 因素包括所选的FPGA和实现的功能,收发器 选择并启用选项,需要时钟树,并产生射频功率。

实现O-RAN CUS和M平面处理的典型中端FPGA SoC, 与 IEEE 1588 v2 PTP 堆栈同步后,将消耗大约 15 W 的功率。 典型的ADRV9029收发器功耗在5 W至8 W之间,具体取决于 在 TDD 或 FDD 配置以及启用的 DFE 功能范围上。 为此,时钟功率,接收器功率,发射器功率以及 必须增加杂项权力。表 2 显示了 系统的总功率不包括发射器链,该功率各不相同 功率输出等级很大。

| 装置 | # 必需 | TDD 70:30 典型耗散 (4T4R) |

| 中端 FPGA SoC | 1 | ~15 瓦 |

| ADRV9xxx | 1 | ~5 瓦 |

| ADRF5545A | 2 | 0.6 瓦 |

| AD9545 | 1 | 0.7 瓦 |

| AD9528 | 1 | 1.4 瓦 |

| PA驱动放大器 | 4 | 1.2 瓦 |

| 杂项。 | 1 | 1 4 |

| 总 | 14 | 26 W 至 29 W |

汇总无线电的功耗,总功耗为 70:30 Tx:Rx 的周期显示 26 W 至 29 W,具体取决于确切的无线电配置 不包括与 PA 相关的电源。表 3 显示了 PA 的几个示例 耗散。因为PA主要在晶体管的线性范围内工作 AB类的一些变化,它们的效率可能在20%之间 和 50%。这就是集成DPD的价值所在。即使对于 小带宽、低功耗PA,几十mW的DPD耗散超过。 被PA效率的提高所抵消。

| 装置 | # 必需 | TDD 70:30 典型耗散 (4T4R) |

| PA (+24 dBm/天线) | 4 | ~2.5 瓦 |

| PA (+37 dBm/天线) | 4 | ~47 瓦 |

对于低功耗小型蜂窝,增加约 2.5 W 的额外功率可带来 总耗散约为 30 W,这对于被动冷却的室内来说是舒适的 由 PoE 解决方案供电的小型蜂窝。

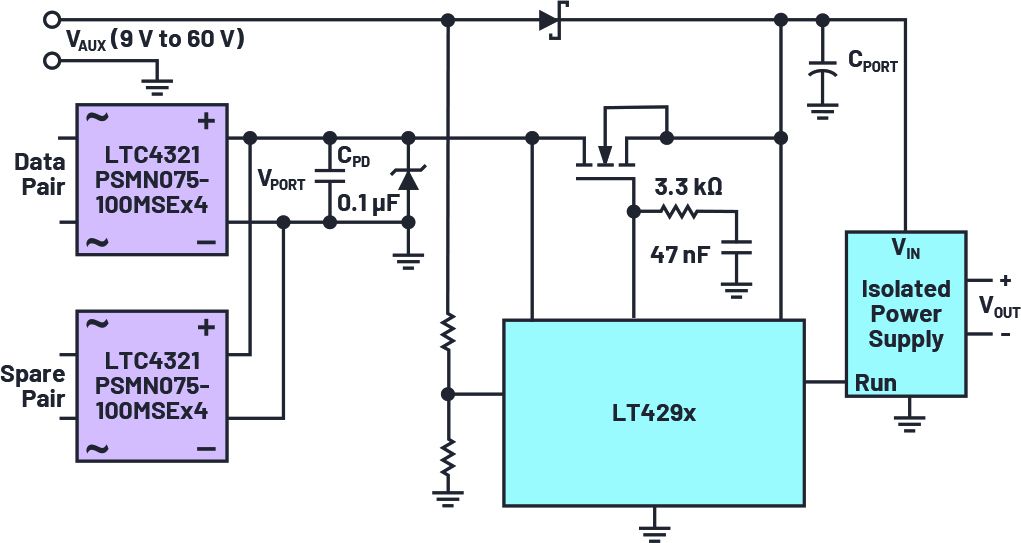

图 11 概述了一种可能的 PoE 解决方案。该解决方案包括 LT4321 桥式控制器,该控制器允许将 MOS 晶体管用作理想二极管,而不是 整流器,其优点是大大提高了效率。这是遵循的 由 LT4295 提供,这是一款符合 802.3bt 标准的 PD 器件。然后可以 适当的当地监管机构,以满足上表所示的要求, 根据需要提供高达 90+ W 的功率。

图 11.PoE 隔离式小型蜂窝电源解决方案。

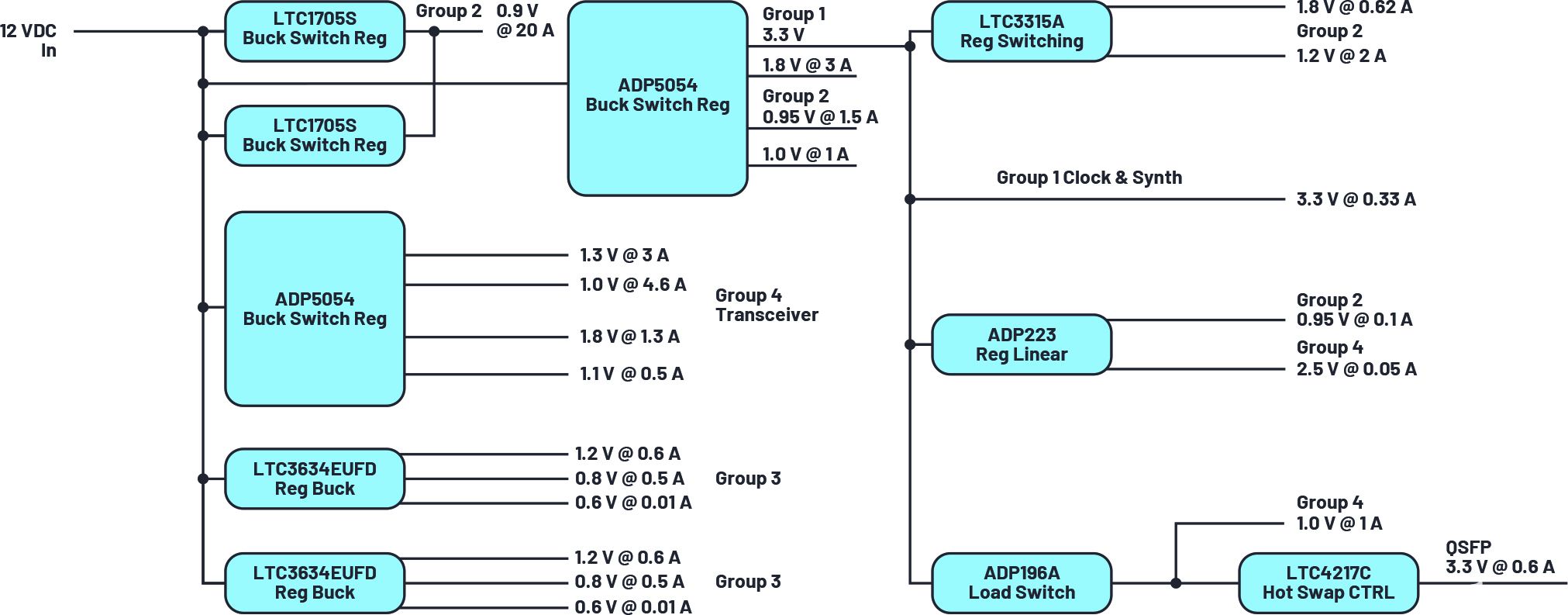

除了 PoE 转换设备之外,还有许多其他设备可用于支持 小型蜂窝参考设计。其中包括ADP5054系列等基石器件,该系列专为ADI收发器以及许多收发器供电而设计。 其他降压转换器和低噪声LDO稳压器,如图12所示。

图 12.小型蜂窝应用的典型电源树。

选项

这种无线电架构的一大优点是它提供的灵活性 在满足一系列市场需求方面。此体系结构经过优化 适用于包括FDD和TDD在内的一系列应用。它同样能够 在低、中和高频段的性能,非常适合小蜂窝通过 大规模 MIMO 平台。在发射器和接收器电路中都可以进行许多不同的权衡,以优化成本、尺寸、重量和功率。而 本介绍侧重于更高的性能和集成度,可以 通过略有不同的选择进行一些简单的权衡,以支持成本。

例如,一些低功耗PA不需要驱动放大器,因此 可能不是必需的。由于许多小型蜂窝应用的RF功率较低, 环行器可以用简单的TR开关代替。最后,如果只是本地 需要的面积性能 双级LNA可以用简单的 单级液化钠。结果是一个低成本的选择,仍然提供良好的无线电 性能。图 13 显示了一个示例。许多其他排列 可在广泛的频率范围内适应各种可能性 和电源选项。

图 13.备用收发器信号链。

结论

此处审查的5G技术设备可用于通信 应用并实现适合5G开发的低成本实施, 尤其是那些实施O-RAN O-RU解决方案的公司。其中包括来自 RadioVerse系列以及RF放大器,时钟恢复/同步, 和以太网供电/负载点调节。这种高度集成在一起 设备集已准备好实施5G小蜂窝,宏蜂窝,微蜂窝, 以及大规模 MIMO 应用。

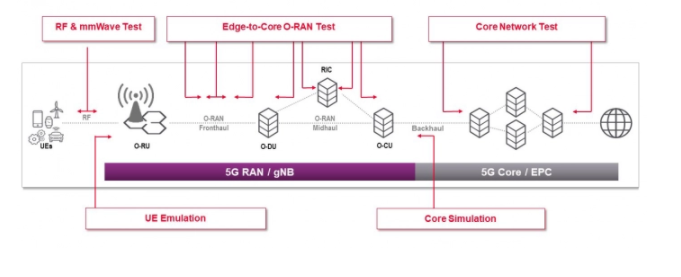

图 14.具有可重新频段射频前端的 5G 原型平台。

当与 FPGA 中提供的合适的 PHY 和软件结合使用时, eASIC, 或ASIC,可以开发一个完整的O-RU解决方案,如图14所示。这 解决方案是与英特尔、Comcores 和 Whizz Systems 的合作伙伴共同开发的。 这些解决方案不仅满足所需的射频特性,还满足成本 以及实现低成本、高性能部署所需的功率预算 O-RAN平台。

审核编辑:郭婷

-

收发器

+关注

关注

10文章

3435浏览量

106045 -

射频

+关注

关注

104文章

5591浏览量

167837 -

MIMO

+关注

关注

12文章

594浏览量

76874

发布评论请先 登录

相关推荐

O-RAN测试解决方案和用例解析

用于O-RAN无线解决方案的5G技术设备

用于O-RAN无线解决方案的5G技术设备

评论