引 言

放心铁子们,本文会从最基础的讲起,适合刚接触电子的童鞋,就算躺在床上,认真看完本文你将无痛地对数字电路有个全面的了解!

数电是一块硬骨头,对于很基础的概念我会细说,对于一些进阶的概念我会尽量用语言解释,所以我会尽量把数字电路涉及的知识点都囊括到,旨在让各位先见识数字电路的全貌,为以后的学习打基础!

下图是数字电路的知识框架,棕色的知识我会详细说说,大家可以马上掌握,蓝色的知识我会尽量用语言讲明白。希望对大家有帮助。

正 文

为什么要学数电?毫不夸张地说,数电带来了信息化时代。大家身边所有的电器,里面都会有一块或多块电路板,上面基本都会有若干个芯片,芯片内部里面跑的全是数字信号0和1。

作为当代人类最高智慧的结晶,芯片的重要性不言而喻,而芯片的最最基本原理,就是数字电路。各位想要为国家芯片事业做贡献的有志少年,数电一定要学好。

OK,下面的内容环环相扣,事不宜迟,我们开搞!

1 数制与编码

数 制

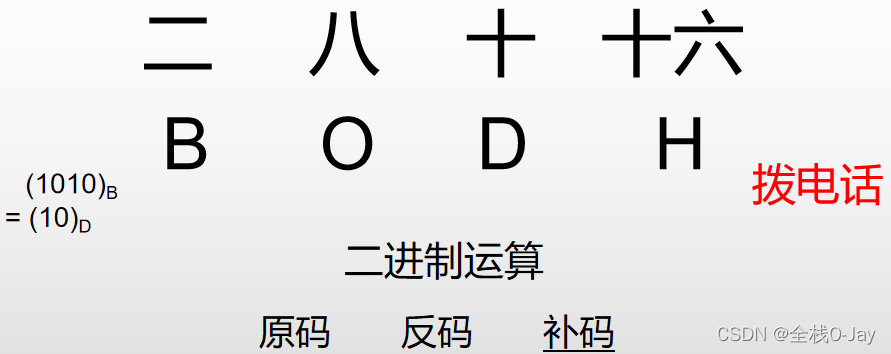

数电里面跑的全是0和1,所以科学家们引入了二进制。十进制我们熟悉,9之后就进一位;二进制就是1之后就进一位。10这个数字,在二进制里,就是十进制的2,同理1010,在二进制里,就是十进制的 23 + 0 + 21 + 0 = 8 + 2 = 10

除了二进制,为了方便表示多位二进制,还有八进制和十六进制。当然只是给一个10我们不知道它是十进制还是二进制,所以一般我们用括号括住数字,然后在右下角表上字母BODH,表示二进制、八进制、十进制和十六进制。这有个小技巧,BODH可以读作“拨电话”,现在你肯定记住啦哈哈。对于这四个进制,要懂得熟练地进行相互转换!

二进制当然也可以运算,要引入原码、反码、补码三个概念。反码是除了符号位全部取反,补码是反码+1,对于正数,原码反码补码不变!负数就按照上面规则变换为补码后正常加减,结果再转为原码就是答案,有个技巧是补码取反再+1就是反码。

编 码

上面说的十进制转为二进制就是一种编码。在数电里有很多的编码方式,都有其意义。这里列出个人觉得挺重要的两个。

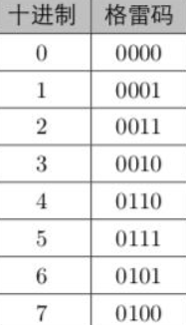

1、格雷码:任意相邻的两位之间只相差一位!在正常工作电路中,输入时常会变化,若输入突然变化多个位,很容易导致输出不稳定,有毛刺。若把输入编为格雷码,会有不错的效果。格雷码在后面讲到的卡诺图化简中会有极大的用处。

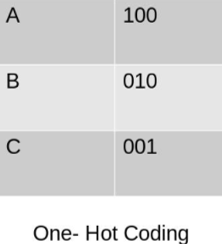

2、独热码:这是最简单的一种编码了,每个状态只有一位是1其他都是0,简单且暴力,在后面设计有限状态机的状态变量时常常使用。

2 门电路

下面进入门电路,这里会涉及模电的知识。数电是由模电发展而来的,他们之间的紧密关系,就在门电路这章里体现。

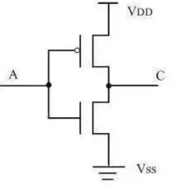

学过模电那肯定很熟悉MOSFET场效应管。在数电中,1表示高电平,0表示低电平,晶体管都处于开关状态,即可以看成一个开关。用一个NMOS和一个PMOS,NMOS下拉,PMOS上拉,就形成一个CMOS,一个CMOS就是最简单的一个非门!!!

咱们看,输入的A为0时,上拉的PMOS导通,输出C为1。输入为1时,下拉的NMOS导通,输出为1,所以这个电路实现输出对输入取反的逻辑功能,就叫其非门。

常用的逻辑门还有与门:有0出0;或门:有1出1;与非门:有0出1;或非门:有1出0;

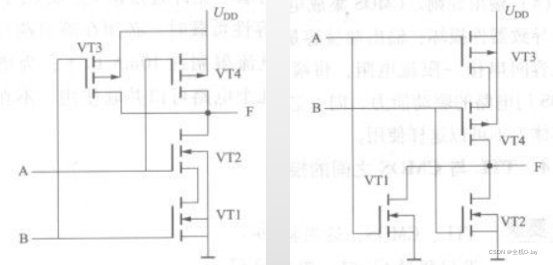

下图中左图是与非门,右图是或非门。(技巧:只看下拉的NMOS!串在一起,就是与非门,并在一起,就是或非门。)

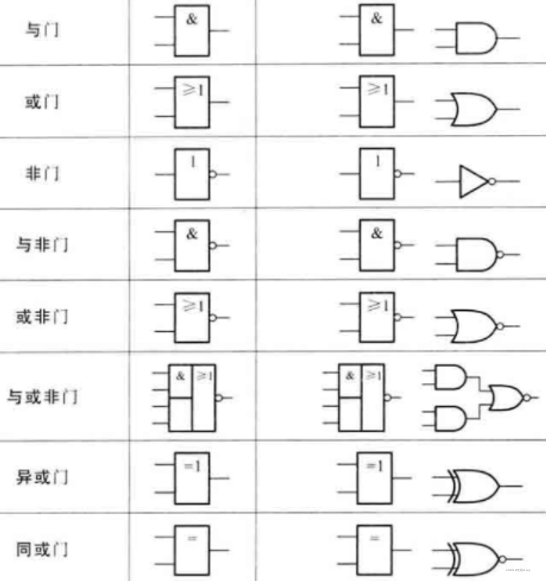

在数电,逻辑门还有许多许多:

大家也要很熟悉右边对应的逻辑符号哦。所以至此,了解了逻辑门的内部构造后,我们可以把它封装成一个个逻辑符号,就如同我们把集成运放电路封装成运放符号一样。接下来,我们就可以放下模电,进入纯逻辑的数字电路!

3 逻辑代数

在数电里,我们描述一个电路的功能,有三种方式。逻辑表达式,真值表和逻辑电路图。

这仨说的是一个事情!就如同西红柿和番茄。

知道了其中任何一个,其他两个你就知道了。但其中最重要的,还是真值表,我们的关注点更多会落在它上面。真值表一写出来,所有东西都明了了。

真值表的左边,是变量的所有情况,如果两个变量,那就是有 22=4 种状态,同理三个变量就 23=8种状态。真值表的右边,是不同状态输入电路之后的输出。我们在输出端一般只关注1,像上面的真值表,有三个1,则把他们对应的状态都相或,即写成标准与或式(最小项之和),

Y = A ′ B ′ + A ′ B + A B ′

经过化简,就是 Y = ( A B ) ′ Y = (AB)‘Y=(AB) ′。

还有一个技巧,当输出很多1时,我们可以只关注0,那么写出来的就是 Y′的表达式,再取反一下就行!

化 简

逻辑表达式很复杂时,我们如何化简?常用的有公式法和卡诺图法。

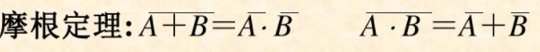

公式法:有大名鼎鼎的摩根公式

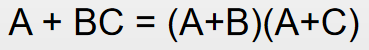

还有下面这个公式也是用得非常非常多,推导的话由左往右推比较难,我们试试由右往左推,则会非常简单。

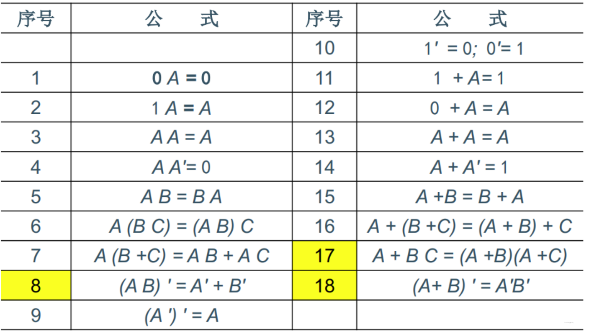

其他公式(图来自网络):

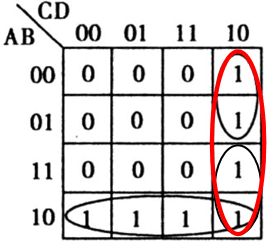

卡诺图化简

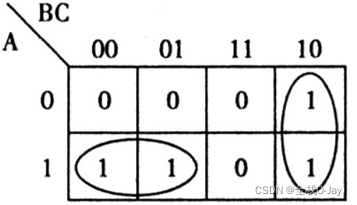

学过数电的童鞋都会惊叹卡诺图的巧妙,它的本质就是前面说的格雷码的逻辑相邻性,我们拿到一个真值表,就可以画出一个卡诺图。三变量的输入有8个状态,然后在对应的状态框框中写上它对应的输出,注意,卡诺图中的变量时用格雷码编码,看下图中的BC就能知道,只有这样才能利用上它的逻辑相邻性,这样,一个卡诺图就画好了,但这只是开始。怎么利用它进行化简?

下图中我给分别相邻的两个1画了两个圈圈,圈圈代表里面的状态相或,因为逻辑相邻性,则两个状态只有一位不同,所以由公式法(A+A’=1)可以消去这一位!即现在这两个3位的状态 A′BC′+ABC′可以由一个2位的状态代替,即 BC′!

因为前面说过整个输出的逻辑表达式就是所有输出为1的状态相或,所以我们把所有1圈完,得到的BC‘+AB’就是输出!所以在卡诺图上画圈圈就可以把一个复杂的表达式化简。

前面是最简单的例子,要想正确使用卡诺图化简,要遵守两个游戏规则:

1、把1圈完;

2、圈大且少。

第二个尤为重要,即我们画圈圈时,圈要尽量大,还要尽量少,这样才能最好地化简一个表达式。

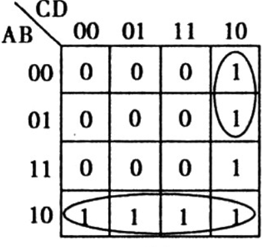

比如下图

这样圈正确吗?大大地错误!没圈完1。下面这样呢?

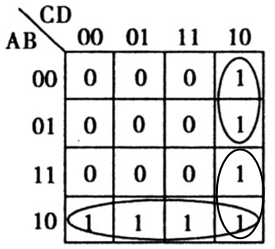

还是不行!因为圈不够大。下面才为正确:两个圈圈搞定,结果是 CD‘ + AB’

卡诺图还有很多很多的技巧,这里说不完,推荐给大家一个很好的b站视频:BV16E411s7TE

4 组合逻辑电路

终于!我们来到了数电的重头戏之一,组合逻辑电路。其实下面我们才真正开始进入数电。

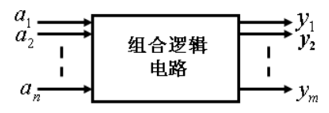

在数电中,所有的电路,可以分为两类,一类就是组合逻辑电路,还有一类是时序逻辑电路,这俩占了数电的大半江山。对于组合逻辑电路,定义为输出只由输入决定。你可能会问,那还会由什么决定?还会被状态决定!这就是时序逻辑电路的特性,等下会讲,先搞定这个组合逻辑电路。

小规模集成电路SSI

如上面这个图,电路全是由基本逻辑门组成,我们称其为小规模集成电路,集成就是逻辑门集成了若干个晶体管嘛,而晶体管是由N型半导体和P型半导体形成,这些半导体是由沙子提炼的硅SI掺杂而成,怎样,模电数电就串起来了。

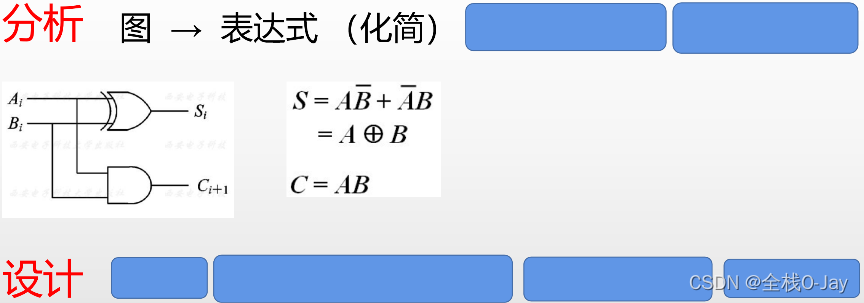

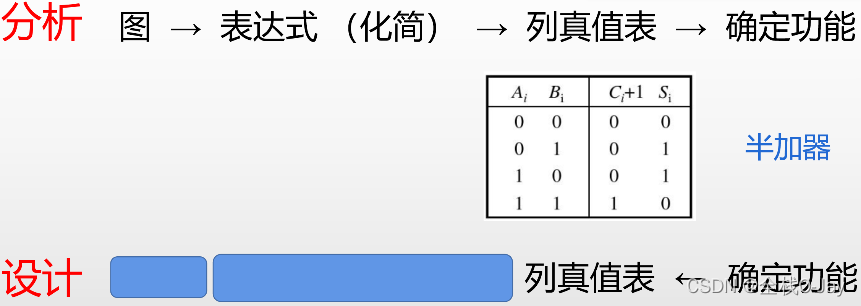

对于SSI,我们无非就搞两件事情,分析和设计。

分析:就是给我一个电路图,我对他一顿分析得出它的功能。图→功能

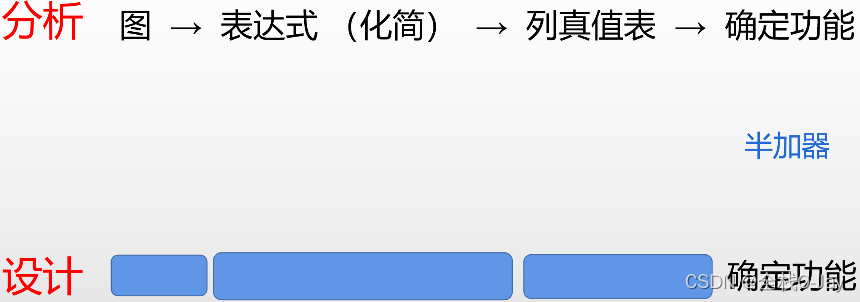

设计:就是我想实现一个功能,通过设计画出一个对应电路图。功能→图

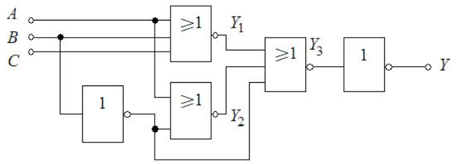

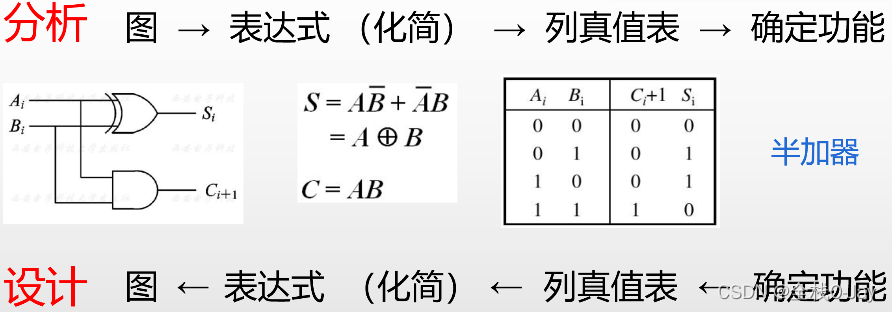

先看分析:现在我有一个电路图:

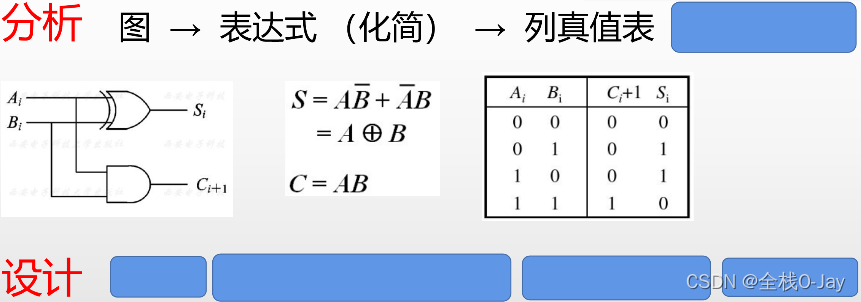

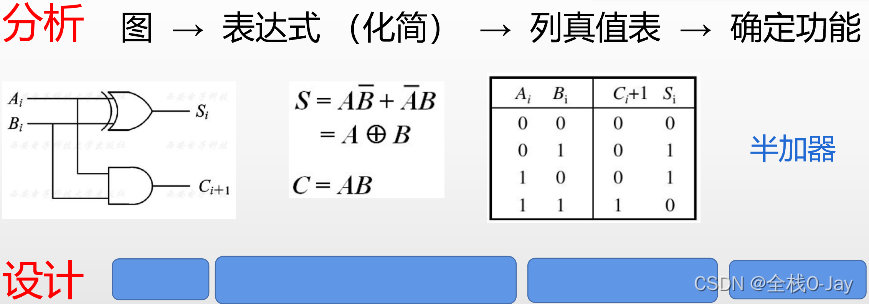

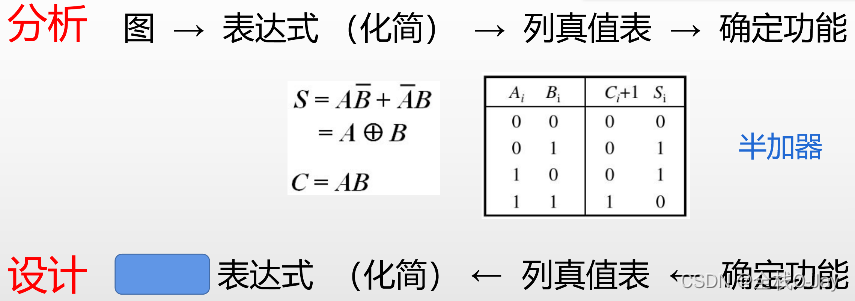

然后我可以轻松地将他的表达式写出,最好再用上化简知识化简一下:

然后由表达式我再轻松列出真值表:

由真值表,我们就能分析出它的功能!这回事一个半加器电路(C为进位,S为和),很重要的哦。

再看看设计,现在我们拿到一个想要实现的功能:

由这个功能我们列出对应的真值表,

由真值表轻松地写出相应的逻辑表达式:

对着表达式,我们就能画出它的电路图啦!

你看,组合逻辑电路的设计是分析的逆过程,就是这么程序化,送分的。

中规模集成电路MSI

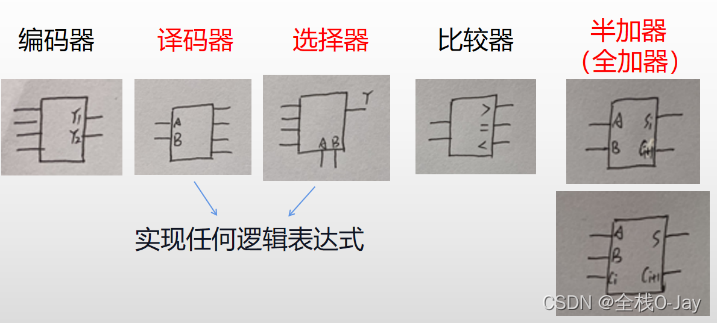

一些逻辑门组合在一起能实现特定的功能,比如上面讲的半加器,我们将其封装起来,就成了MSI。

上图就把所有常见的LSI列了出来,

编码器:如第一根引脚输入1,则输出为00;第二根引脚输入1,则输出为01,依此类推;

译码器:如输入为00,则第一根引脚输出1;如输入为01,则第二根引脚输出1,依此类推;

选择器:比较两个输入,如相等就在相等的引脚输出1;

加法器:半加器前面讲过,全加器就是输入多了一位以前的进位。

译码器和选择器尤为重要,因为它们很常用,且能实现任意的组合逻辑表达式。

高规模集成电路LSI

同理,就是一些MSI组合在一起能表示一个更全面的功能,就将其封装在一起,变成LSI。

不如PLD(可编程逻辑器件)和 FPGA,这章不是重点,但我想说一下FPGA,这个芯片是相对于单片机来说的另一大控制芯片,使用硬件描述语言(HDL)编程,并行执行代码且性能更强大,目前它的缺点就是太贵了,我相信以后随着成本下来,它就逐渐进入我们生活,带来更加智能的世界。

5 触发器

正式讲时序逻辑电路之前,要讲讲时序逻辑电路的单位模块,触发器。

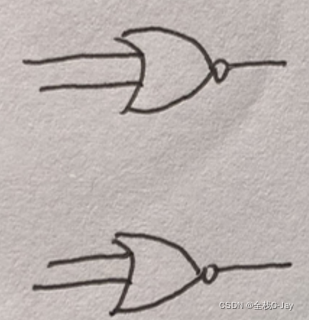

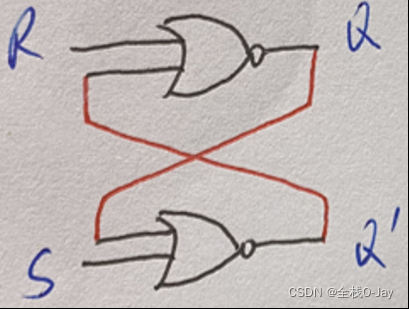

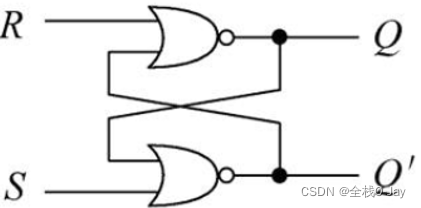

在平静祥和的日子里,两个普普通通的或非门在路上走着,非常纯真无邪,

但是突然,一个科学家对它们做了这样的处理:哈哈哈别害怕

这一搞,整个时代向前推进了一大步!因为这就是RS触发器!

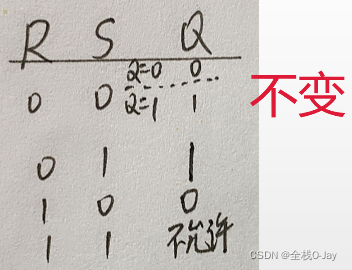

我们来看看它的真值表:

相信大家都能分析出来,先说说输入为11时为什么不允许,因为11会得到输出00,如果这时输入再从11变为00,那问题就出现了,电路会处于不定的状态,这肯定不行,所以就禁止了输入为11的情况。我们重点看看输入为00时,当电路的状态Q为0时,输出为0;当电路的状态Q为1时,输出为1!组合逻辑电路大为震惊,因为明明输入是一样的00,为什么输出会不同?因为电路的状态不同,这就是触发器的魅力,也是时序逻辑电路的基础,也是数电的超级重点!

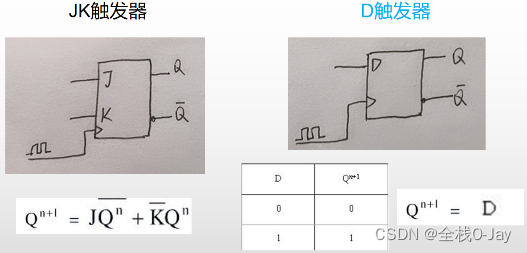

RS是最初的触发器,所以会有一些小问题,随着时代进步,触发器也经历了许多迭代,好奇的童鞋可以从你们的书上了解这段历史,这里我直接列出现在用的最多的两款触发器:D触发器和JK触发器。

这两款触发器都有一个时钟端,用于输入时钟脉冲CLK,输出会随着时钟CLK的变化而刷新,且他们的时钟触发方式是边沿触发,即在CLK的上升沿或下降沿触发,非常的方便。

上图中下面的公式为触发器的输出方程,对于时序逻辑电路来说就是状态方程,是需要我们记住的,相当于这款触发器的说明书。我们着重关注D触发器!因为它方程最简单,是最易学的。

6 时序逻辑电路

Finally,我们来到了数电的重中之中,也是其魅力所在,时序逻辑电路。

关于它的意义我可以再举一个例子,有一个机器我每按一下按钮它会依次输出12345,这对于组合逻辑电路来说是不可能的任务,因为每一次输入都是相同的按一下按钮,为什么输出会不同,它不理解,而时序逻辑电路说我可以!因为它能记住当前的状态,从而知道下一步应该怎么走。

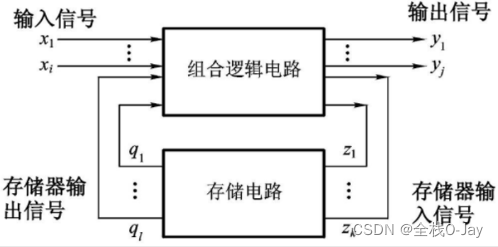

观察上图能知道时序逻辑电路里面也有组合逻辑电路,是由发展而来,主要是下面的那个存储电路,能把电路的现态(现在的状态)给记住!从而影响次态(下一次触发的状态)。

因为时序逻辑电路的主角是触发器,也正是由于触发器,它引入了时钟和状态这俩重要概念,使我们能通过电路实现的功能更加丰富。

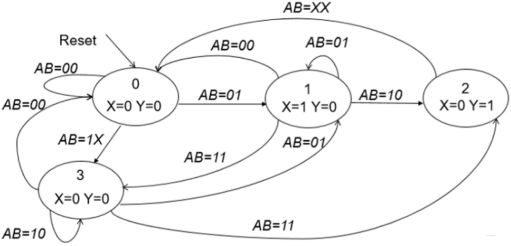

FSM(有限状态机)

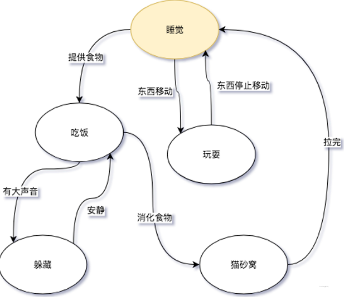

对于时序逻辑电路,它所有的状态变换都可以画出来,即状态转换图,就如同真值表描述了整个组合逻辑电路的功能,状态转换图描述了整个时序电路的功能。这样在不同状态之间跳来跳去的电路或机器,我们就叫它有限状态机(Finite State Machine)。(所以FSM肯定是时序逻辑电路)

比如下面这个就是一只猫在一天里的状态变化:

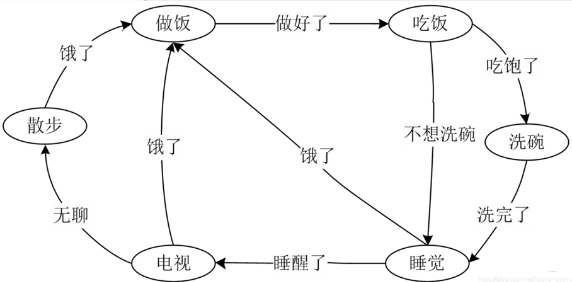

这是某人一天的状态变化:

写专业点(给状态编码),可以是下面这样,先别害怕,很好分析的:

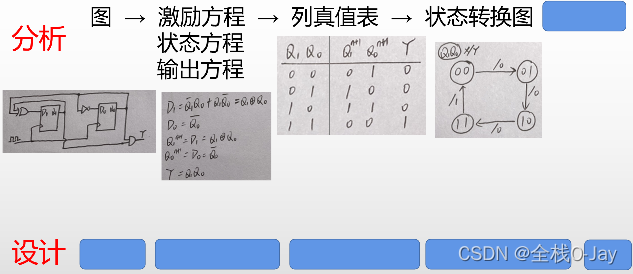

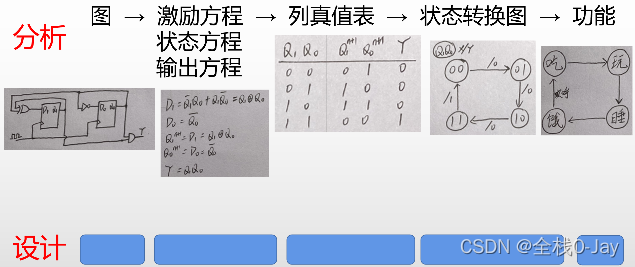

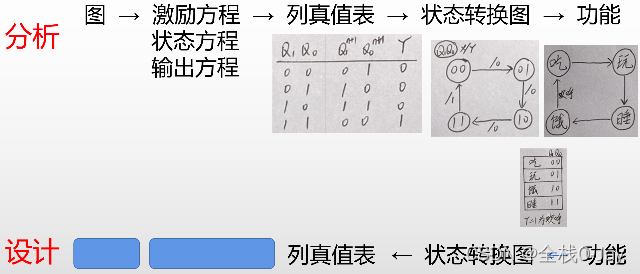

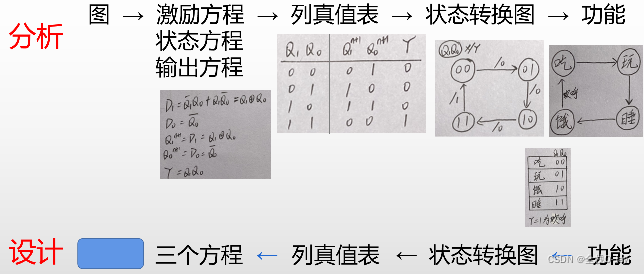

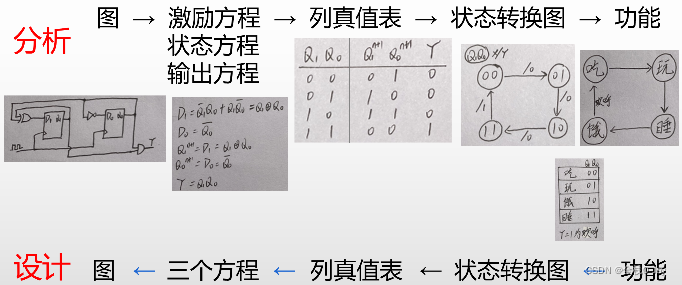

FSM的分析和设计

各位应该还记得前面组合逻辑电路的分析和设计是多么的简单,FSM的分析和设计与其概念一样,分析就是图→功能,设计就是功能→图,但过程很不一样,也是很简单的!

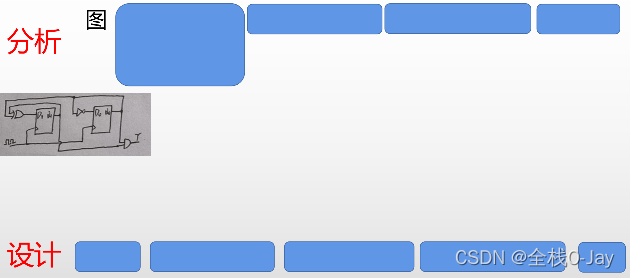

先看分析,现在我拿到一个电路图,由两个D触发器组成,所以我知道这个电路状态变量为2,即有4个状态:

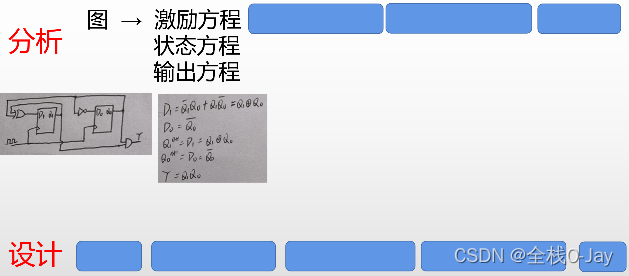

由这个电路图我可以写出三个方程,激励方程(输入方程)、状态方程和输出方程。

激励方程就是触发器的输入端的方程,D1和D0由图看很容易写出表达式;

状态方程就是我们之前背的触发器的“说明书”,有激励方程就能轻松写出Q1n+1和Q0n+1;

输出方程最简单,看着输出端Y,写出它的表达式就行。

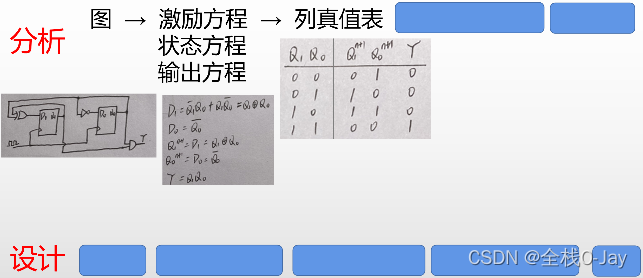

由状态方程和输出方程就可以列出真值表!

由真值表就可以画出这个FSM的状态转换图:( X/Y 表示 输入/输出 ,该电路没有输入所以X没有)

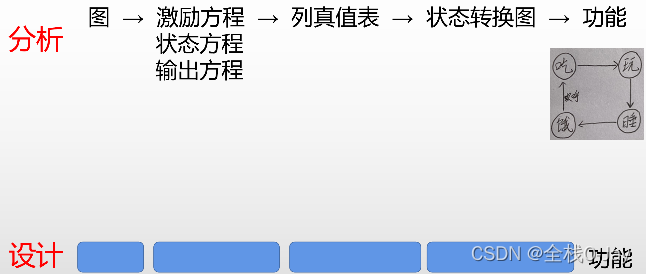

看着这个状态转换图,我们可以发现它的含义,啊,原来它是我的一天的状态变化,吃饱了就玩,玩累了就睡,睡醒了就感到饿,饿时突然有吃的,我就会“欢呼”。(欢呼代表输出为1)

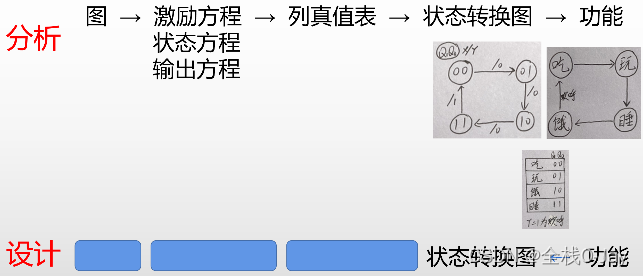

现在来看看设计过程!我有一个功能(我的一天状态变化),现在想画出一个实现该功能的电路:

先经过状态编码,将吃编码为00,玩编码为01,饿编码为10,睡编码为11,欢呼定义为输出1,ok,现在就可以画出整个功能的状态转换图了!

有状态转换图,我们画出对应的真值表,也叫状态转换真值表:

由真值表,我们细心地先看着Y项写出输出方程,再看着Q1n+1和Q0n+1写出状态表达式,再由我们背的触发器“说明书”,写出D1和D0的激励方程,搞定!

三个方程有了,电路图轻松画出!

7 进阶

至此整个数电最基础的知识我都讲到了,虽然很基础,但是越基础的东西越重要,其实电路的分析和设计也可以搞得很难,上面那些只是便于大家理解最简单的例子,想要深入掌握他们还得靠日积月累的做题和巩固,这篇文章只是帮到大家形成知识框架。

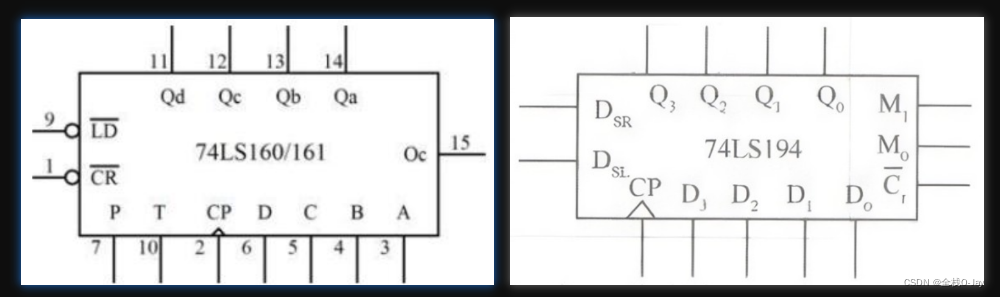

74LS160、74LS194

之后大家会学到74LS160、74LS194这两个芯片,非常非常的重要,一个是计数芯片,一个是移位芯片,就如译码器和选择器能实现任意组合逻辑电路,它们能实现任意的时序逻辑电路,所以很多题目都会考到它们,让你用这俩芯片之一设计一个现实生活中的功能。

施密特触发电路、单稳态电路、多谐振荡电路

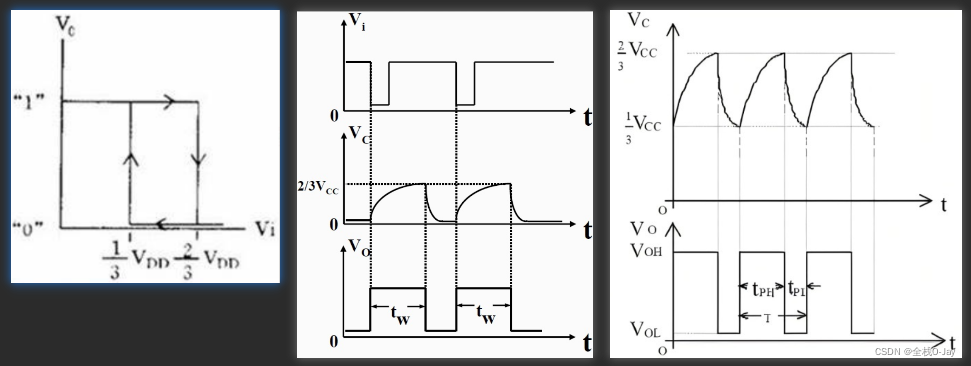

这三个电路会在波形的发送与转换这一章学习到,三个电路都能用逻辑门手搭出来,实现的电路有多种,但波形就是下面这样,分别是施密特触发电路、单稳态电路、多谐振荡电路。

施密特触发电路就是输入增大到一个A值,输出取反,但是输入随后减小到A值时,输出没变化,要继续减小到B值,输出再取反,然后它也还是要增大到A值,输出才变化,这就是这电路的规则,很有意思!

单稳态指输出的稳定状态只有一个,输入刺激以下输出可能会变,但过一段时间它会自己回到稳态。超市的门就是单稳态,你推开之后它会自动回到关闭状态。

多谐振荡电路一般就是生成一个方波或三角波。

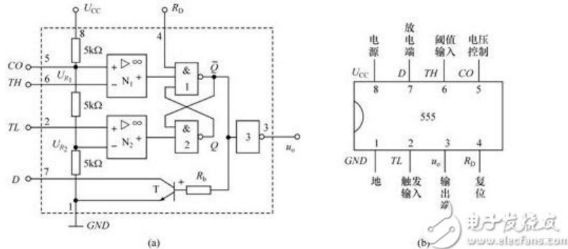

555定时器

555定时器的重要性就相当于模电中的运放,它每一年的销量都处于芯片的前列,因为它简单且太实用了,上面说到的三个电路也可以通过555搭建出来。因为篇幅有限,555的知识得靠各位从书中理解了。

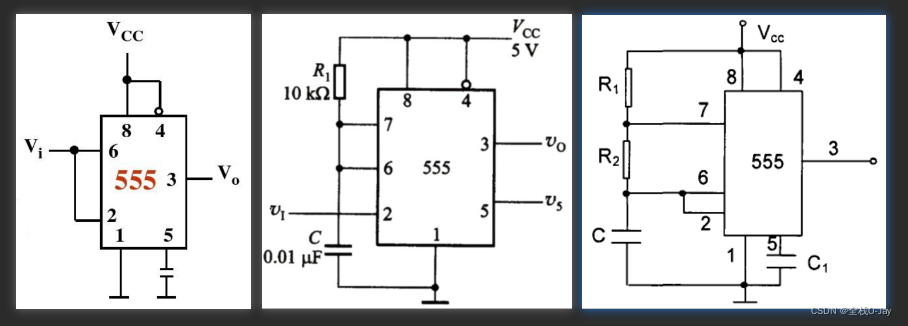

以下分别是555实现施密特触发电路、单稳态电路、多谐振荡电路的电路

AD/DA电路

AD:模拟到数字转换

DA:数字到模拟转换

这章你们会学到如何自己手搭一个AD和DA电路。

E N D

最后再看一下数电所有知识的知识框架,希望能帮助各位对数电形成大致的了解。

审核编辑 :李倩

-

芯片

+关注

关注

454文章

50689浏览量

423016 -

二进制

+关注

关注

2文章

794浏览量

41637 -

数字电路

+关注

关注

193文章

1605浏览量

80570

原文标题:IC知识干货:一文极速理解数电!(建议收藏)

文章出处:【微信号:IC修真院,微信公众号:IC修真院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DAC81408的建立时间为12uS,如何理解数据手册中的12uS建立时间这个参数呢?

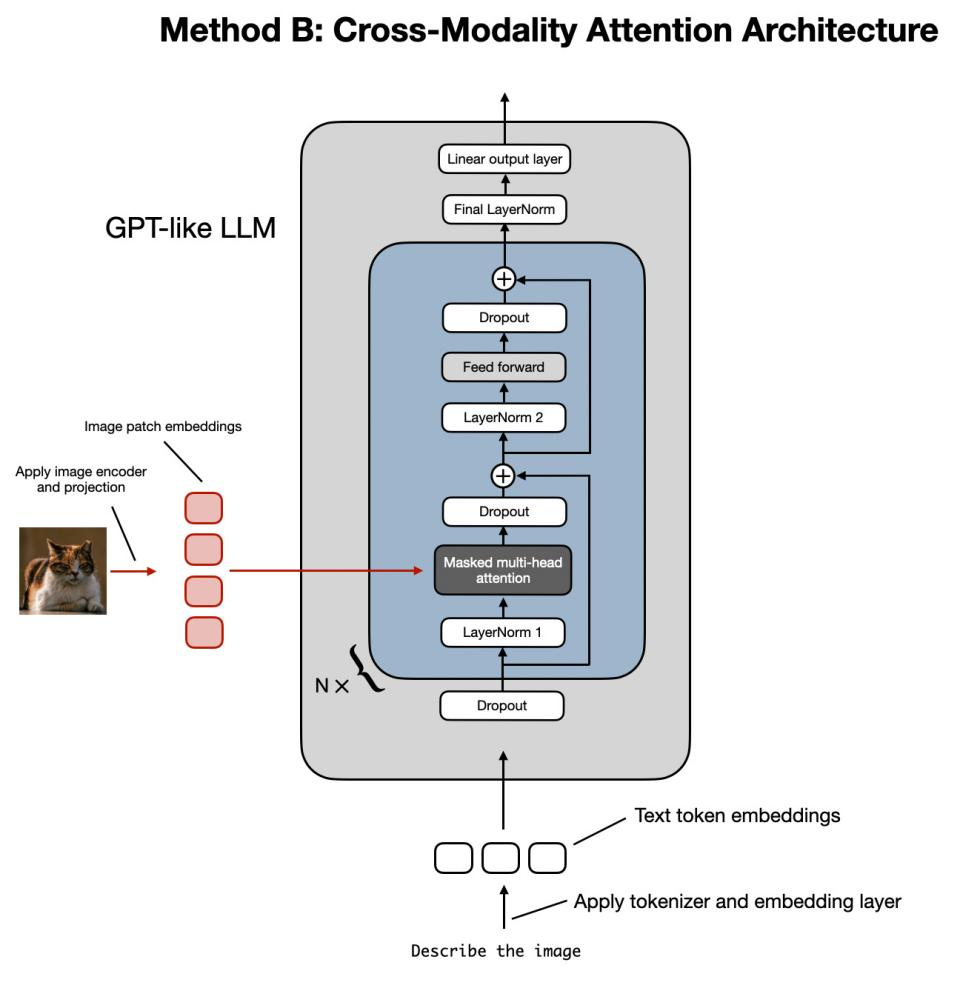

一文理解多模态大语言模型——下

一文理解多模态大语言模型——上

比亚迪仰望U9刷新中国汽车极速记录

如何理解PCB设计的爬电距离?

新一代智能插件AOI用极速编程颠覆了传统AOI认知

电口模块还是光模块、DAC、AOC?一文解析通信接口的优劣之选

深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别

一文极速理解数电!

一文极速理解数电!

评论