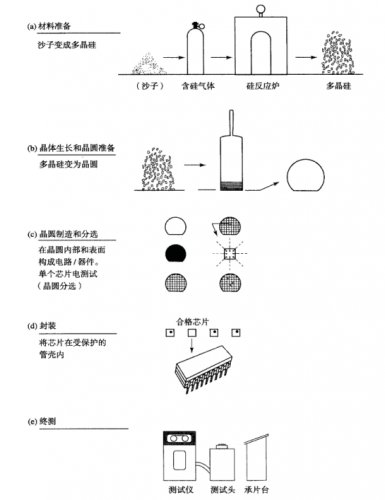

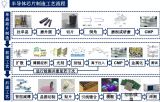

半导体集成电路是将很多元件集成到一个芯片内, 以处理和储存各种功能的电子部件。而芯片制造主要分为5个阶段:材料制备、晶体生长或晶圆制备、晶圆制造和分拣、封装、终测。如下图所示:

半导体生产阶段

半导体集成电路是在晶圆的薄基板的基础上,通过制造多个相同电路而产生的。如同制作披萨时添加配料之前先做面团一样,晶圆作为半导体的基础,是指将硅(Si)、砷化镓(GaAs)等生成的单晶柱切成薄片的圆盘。本文就将讲述晶圆制造的相关基础知识。晶圆制造(wafer fabricaTIon)是在晶圆表面上或表面内制造出半导体器件的一系列生产过程。正文开始前,首先介绍一些晶圆术语,以方便后续理解。

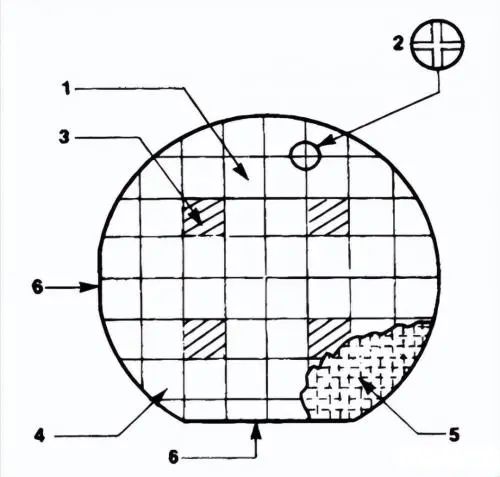

•芯片(chip、die)、器件(device)、电路(circuit)、微芯片(microchip)或条码(bar):所有这些名词都是指占大部分面积的微芯片图形。

•划片线(scribe line、saw line)或街区(street、avenue):晶圆上用来分隔不同芯片的间隔区。划片区通常是空白的,但有时也会在间隔区放置对准标记(十字mark)或测试结构(testkey)。

•工程试验芯片(engineering die)和测试芯片(test die):这些芯片与正式芯片不同,它主要用于对晶圆生产工艺单额电性能测试监控。

•边缘芯片(edge die):晶圆边缘残缺的芯片。这部分芯片占比越高产生的损耗就越大,晶圆尺寸增大可以减小边缘芯片的比例。

•晶圆的晶面(wafer crystal plane):晶格方向,与器件的方向是相关的。

•晶圆定位边(wafer flat/notche):分主定位边(major flat)和副定位边(minor flat),如下图定位边表示这是一个P型<100>晶相的晶圆。

芯片制造工艺

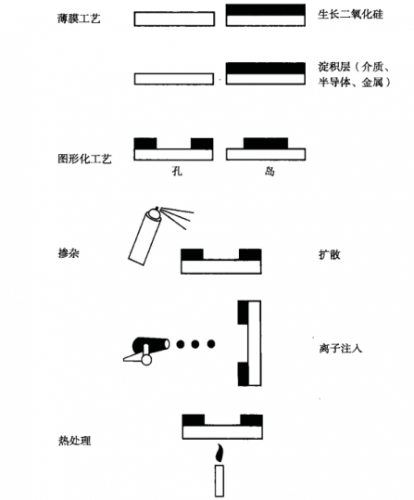

芯片制造主要根据薄膜工艺、图形化工艺、掺杂和热处理4个基本的工艺步骤来生产出特定的器件。

晶圆制造基本工艺

薄膜工艺

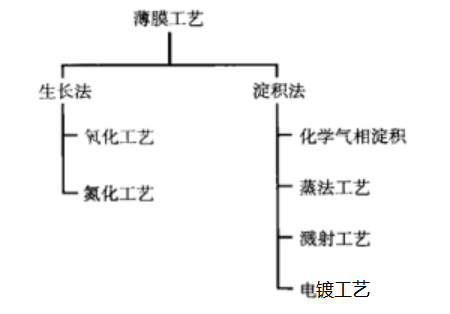

薄膜工艺(layering)是在晶圆表面形成薄膜的加工工艺。在芯片制造过程中,需要在晶圆表面形成各种各样的薄膜。这些薄膜可以是绝缘体、半导体或者半导体,它们由不同材料使用多种工艺技术生长或沉积而成。

薄膜工艺

以下列举了薄膜制备的工艺分类和工艺与材料的对照表。

薄膜工艺分类

工艺与材料对照表

图形化工艺

图形化工艺(patterning)是通过一系列步骤将晶圆表面薄膜的特定部分去除以形成特定图形的工艺。图形化工艺的目标是根据设计需要在晶圆上形成尺寸精确的特征图形,在晶圆上的位置要正确且与其他关联层的关联也要正确。图形化工艺也被广泛称为光掩模(photomasking)、掩模(masking)、光刻(photolithography)。

图形化工艺是4个基本工艺步骤中最关键的,其确定了器件的关键尺寸。图形化工艺过程的错误可能会导致图形的歪曲或套准不好,最终对器件的电性能产生影响。图形化工艺在现代晶圆生产过程中要完成30层或更多。

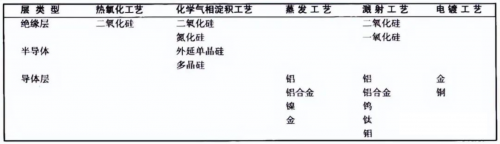

光刻工艺依靠光刻模板(reTIcle)和掩模版(mask)将特定图形转移至晶圆上。光刻模板可以直接用于进行光刻也可以用来制造掩模版。掩模版就是在玻璃底板表面镀铬,进行光刻步骤时光束会穿过未镀铬的亮场部分曝光在晶圆上的光刻胶上已达到图形转移的目的。

光刻模板和掩模板

光刻模板和掩模板一般由工厂的单独部分制造或者从外部供应商购买。每个电路都有自己的光刻母版和掩模板。

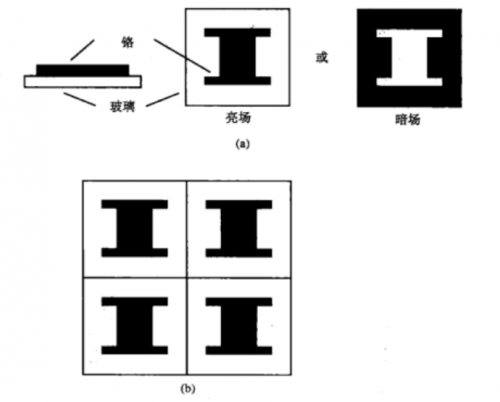

以下为基本十步图形化工艺:

光刻十步法工艺

掺杂

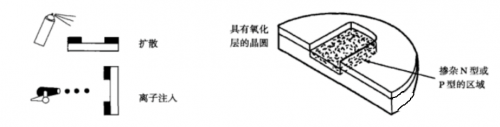

掺杂是将特定量的杂质通过薄膜开口引入的晶圆表层的工艺过程。掺杂有两种工艺方法:热扩散(thermal diffusion)和离子注入(ion implantaTIon)。热扩散是在1000℃下,掺杂原子通过扩散化学反应迁移带暴露的晶圆表面,形成一层薄膜。离子注入是掺杂原子离子化后,被电场加速到很高的速度,从而注入至晶圆表层。

掺杂技术

热处理

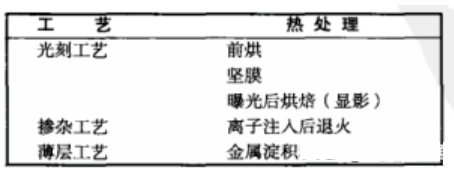

热处理是将晶圆加热或冷却来达到特性结果的工艺步骤。热处理过程中晶圆没有增加或减少任何物质。离子注入后会有一步重要的热处理过程,掺杂原子的注入会造成晶圆损伤,热处理可以修复损伤,这称为退火(anneal),温度在1000℃左右。金属导线制程后会有一步热处理过程以确保金属连线与晶圆表面紧密熔合从而确保良好的导电性。

热处理表

晶圆制造实例

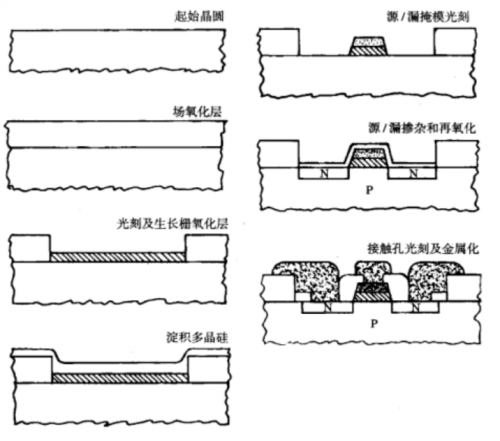

硅栅MOSFET工艺步骤

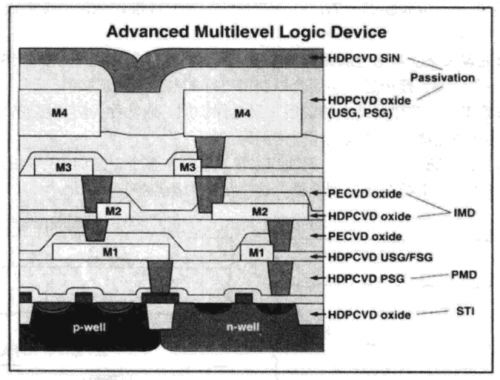

现代芯片结构

还要说明的是,半导体产业包括生产晶圆的晶圆产业以及以晶圆为材料设计和制造的晶圆加工产业——制造行业 (Fabrication, FAB)。另外,还有组装产业,它将 加工过的晶圆切割成晶粒,并包装好以防止受潮或受压。

审核编辑 :李倩

-

集成电路

+关注

关注

5404文章

11718浏览量

364753 -

半导体

+关注

关注

335文章

28029浏览量

225638 -

晶圆制造

+关注

关注

7文章

287浏览量

24213

原文标题:晶圆制造相关术语及工艺介绍

文章出处:【微信号:射频美学,微信公众号:射频美学】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

芯片制造的画布:晶圆的奥秘与使命

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺

晶圆制造中的T/R的概念、意义及优化

晶圆制造recipe(工艺配方)的定义、重要性、种类及构建和验证方式

WD4000系列晶圆几何量测系统:全面支持半导体制造工艺量测,保障晶圆制造工艺质量

WD4000系列晶圆几何量测系统:全面支持半导体制造工艺量测,保障晶圆制造工艺质量

晶圆制造相关术语及工艺介绍

晶圆制造相关术语及工艺介绍

评论