本应用笔记讨论了MAX11613 ADC与高输入源阻抗的精度使用的方法。

介绍

无缓冲ADC因其设计简单而常用。但是,这些ADC的采集时间有限,需要输入信号在分配的时间内建立。这些ADC跟踪输入信号的间隔必须长于输入信号的建立时间,才能获得精确的转换结果。因此,需要低输入源阻抗。

逐次逼近寄存器 (SAR) ADC 架构

逐次逼近寄存器(SAR)ADC经常用于采样速率低于每秒5兆采样(Msps)的中高分辨率应用。SAR ADC的分辨率通常为8至20位。它们具有低功耗和小尺寸。这些特性使ADC成为各种应用的理想选择,如便携式/电池供电仪器、笔式数字化仪、工业控制和数据/信号采集。

SAR ADC基本上实现了二进制搜索算法。因此,虽然内部电路可能以几兆赫兹(MHz)运行,但由于逐次逼近算法,ADC采样速率只是数字的一小部分。

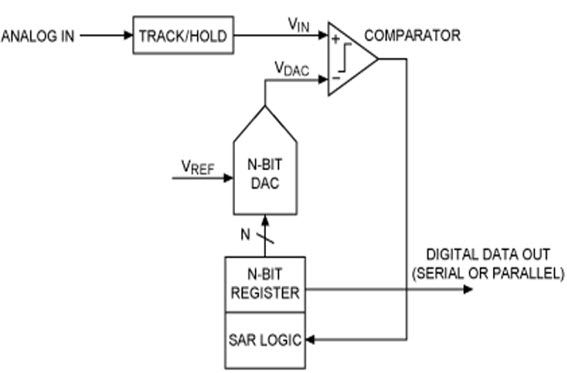

SAR ADC的基本架构非常简单(图1),但实现它有很多变化。模拟输入电压(V在) 处于跟踪/保持状态。N 位寄存器首先设置为中间量程(100...00,其中最高有效字节 (MSB) 设置为 1),以实现二叉搜索算法。这会强制 DAC 输出 (V代数转换器) 为 V裁判/2,其中 V裁判是ADC的基准电压。进行比较以确定 V 是否在小于或大于 V代数转换器.比较器输出为逻辑高电平或1,如果V电压为1,则N位寄存器的MSB保持1在大于 V代数转换器.相反,比较器输出为逻辑低电平,寄存器的MSB为逻辑0,如果V为V。在小于 V代数转换器.然后,SAR 控制逻辑移动到下一个向下的位,强制其为高电平,然后进行另一次比较。序列一直向下持续到最低有效字节 (LSB)。转换完成,N位数字字在寄存器中可用。

图1.简化的N位SAR ADC架构。

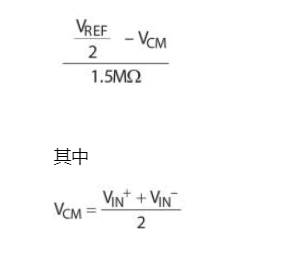

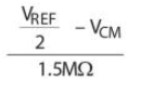

MAX11163等效输入电路

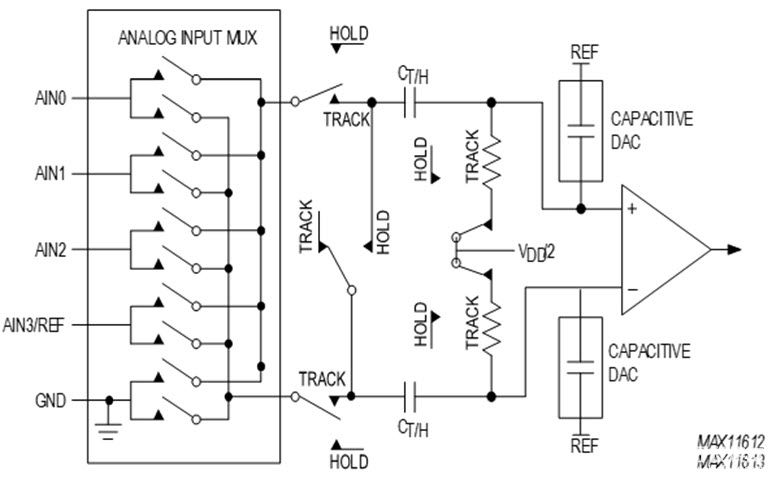

MAX11613模拟输入架构包含一个模拟输入多路复用器(mux)、一个全差分采样保持(T/H)电容、T/H开关、一个比较器和一个全差分开关电容式数模转换器(DAC)(图2)。模拟输入多路复用器连接C电镀在单端模式下的模拟输入与差分模式下的+和–模拟输入之间。

图2.MAX11613等效输入电路

T/H 开关位于轨道位置和 C电镀在采集间隔期间对模拟输入信号充电。T/H 开关在采集间隔结束时移动到保持位置,将电荷保留在 C 上电镀作为输入信号的稳定样本。开关容性DAC在转换间隔期间进行调整,将比较器输入电压恢复到12位分辨率限制内的0V。此操作需要 12 个转换时钟周期。相当于转移11pF x(V)的电荷在+ - V在-) 从 C电镀到二进制加权电容DAC,形成模拟输入信号的数字表示。

如果源阻抗较高(>1.5k?),采样精度可能会受到影响,这会导致输入信号的建立时间长于给定的采集时间。使用不同的源阻抗值进行了以下实验。

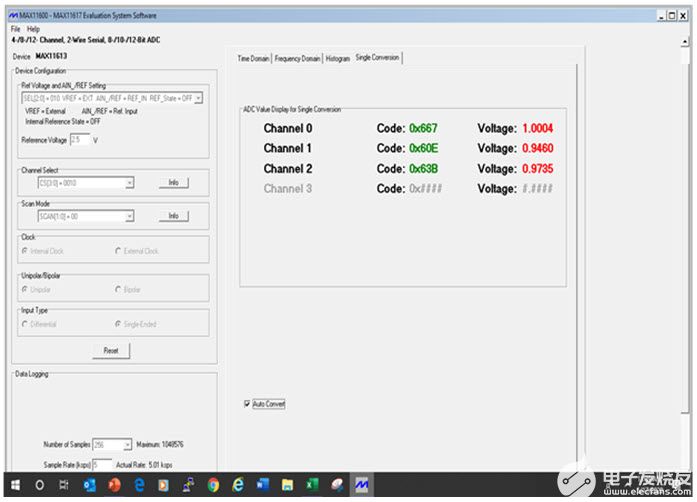

实验

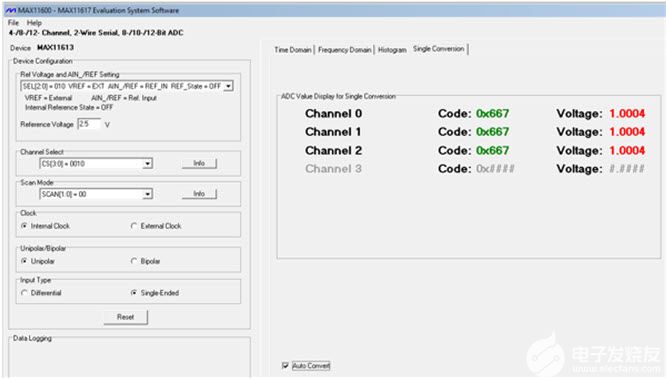

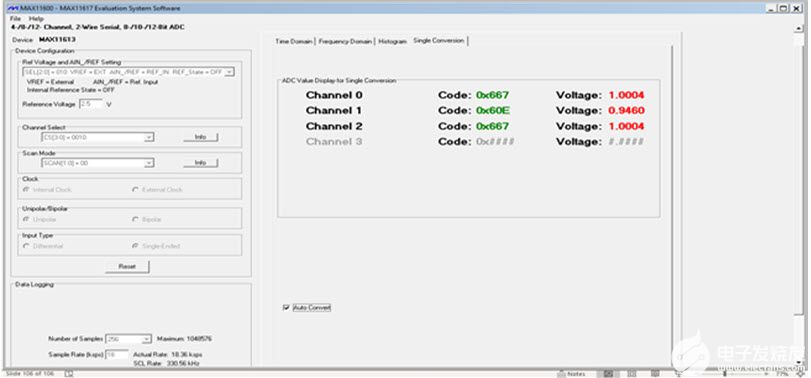

MAX11163配置为测量三个通道的数据:CH0, CH1和 CH1以查看高阻抗源对测量精度的影响。图3显示了具有三种不同源阻抗的数据。CH0有低 50?源阻抗。CH1有 10k?源阻抗,带有一个额外的 100pF 电容器,从模拟输入连接到地。CH1有 10k?源阻抗。C的实测数据H0(1.0004V) 在输入电压为 1.0000V 时误差约为 -0.04%。C的实测数据H1(0.9460) 的误差约为 5.5%。MAX11613测得的1.0000V输入电压为0.9735,输入端没有额外的100pF电容。误差约为 2.69%。

图3.MAX11613从1.0000V输入电压捕获不同源阻抗的数据。

准确性改进

可以使用三种方法来最小化具有较高源阻抗的采样误差。

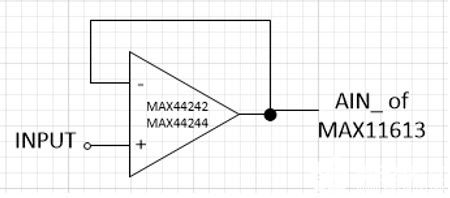

方法 1.缓冲放大器

MAX44244配置为缓冲放大器(图4)时,提供低输出阻抗,用于MAX11613精确捕获信号。MAX44244还具有2μV的极低失调,非常适合与MAX11163配对,用于高精度测量,输入阻抗高达1MHz。MAX44244是缓冲放大器的最佳选择,用于高达10MHz的更高输入频率。

图4.MAX44242/MAX44244缓冲放大器

结果表明,当缓冲放大器连接在具有高输入阻抗的两个通道之后时,所有三个通道的低精度误差仅为-0.04%。

图5.缓冲放大器跟随C的数据H1和 CH1(高输入源阻抗)。

方法 2.高 CEXT 电容

通过在MAX11613 ADC的模拟输入端在通道2(CEXT = 0.1μF)安装高外部电容,器件的测量精度误差大幅提高至-0.04%,就好像输入具有低阻抗源(图6)一样。0.1μF的高电容可以存储足够的电荷,以便对内部采样电容(C在).因此,建立时间仅为R在× C在而不是更长的(R源+ R在) × C在.因此,准确性显着提高。

图6.1.0000V输入的数据。CH0源阻抗为 50?。CH1源阻抗是10K?100pF到地面。CH1源阻抗是10K?0.1μF接地。

提高测量精度的第二种方法仅适用于直流或近直流输入信号,因为至少0.1μF的高输入电容(CEXT)是这样的。 该 0.1μF 电容器提供 1/(2 × 3.1416 × 10k? × 0.1μF) = 159Hz 与 10k?输入源阻抗。

方法 3.更低的外部 SCL 串行时钟频率

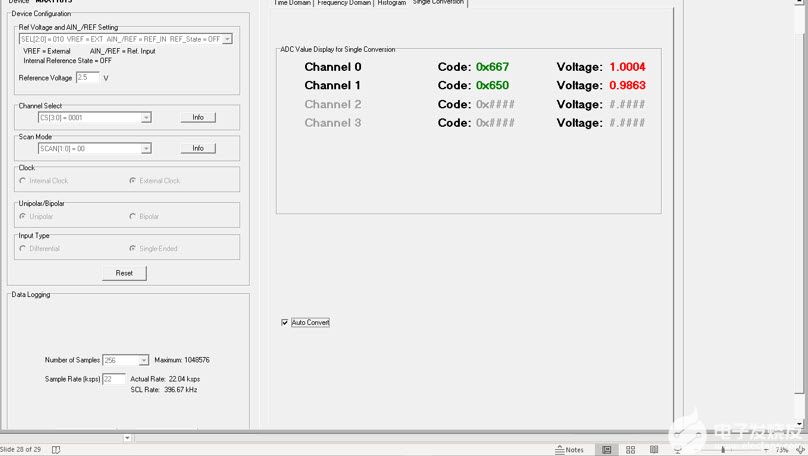

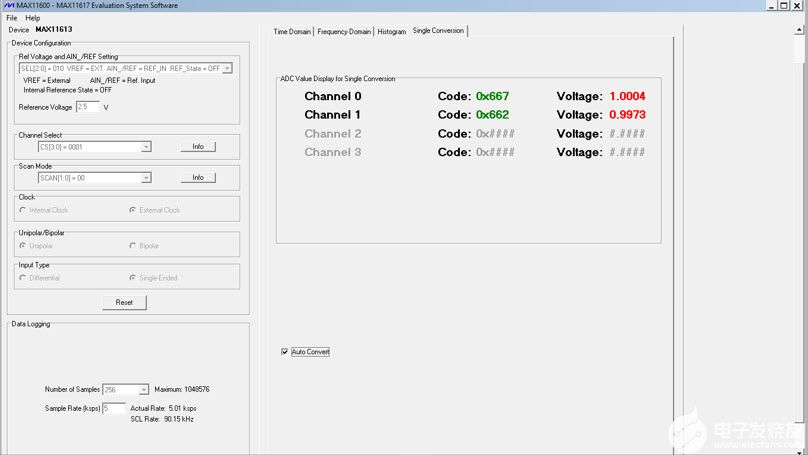

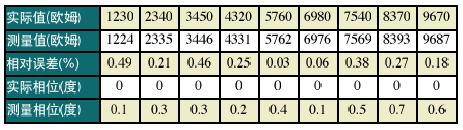

如果模拟输入源阻抗较高,则采集时间常数会延长,并且转换之间必须留出更多时间。实现高转换精度的第三种方法是降低外部SCL串行时钟频率,以提供所需的额外转换时间。图7和图8分别描述了SCL= 400kHz时1.37%和SCL= 90kHz时0.27%的精度误差。

图7.R源CH0= 50?, CH1= 10k?/1000pF, V在= 1.0000V, V模数转换器(CH0) = 1.0004V (误差 = -0.4%),V模数转换器(CH1) = 0.9863V (误差 = 1.37%), f标准及校正实验所= 400kHz。

图8.R源CH0= 50?, CH1= 10k?/1000pF, V在= 1.0004V, V模数转换器(CH0) = 1.0004V (误差 = 0%), V模数转换器(CH1) = 0.9973V (误差 = 0.27%), f标准及校正实验所= 90kHz。

结论

本文介绍了三种方法,以提高MAX11163在高输入源阻抗下的测量精度。缓冲放大器方法是使用MAX44242实现高达5MHz高输入频率的最佳方案。MAX44244具有极低的失调电压,仅为2μV,输入频率高达1MHz,因此可提供较低的精度误差。对于高达 100Hz 的直流或低输入频率,更简单、成本更低的解决方案是使用从模拟输入连接到地的 0.1μF 高值电容器,为内部采样电容器 (C电镀).提高转换精度的最便宜的方法是简单地降低外部SCL串行时钟频率,这可以通过软件更改来实现。

审核编辑:郭婷

-

寄存器

+关注

关注

31文章

5343浏览量

120404 -

SAR

+关注

关注

3文章

416浏览量

45974 -

adc

+关注

关注

98文章

6500浏览量

544721

发布评论请先 登录

相关推荐

Easy Drive™ ADC 简化高阻抗传感器的测量

利用传感器和ADC提高精度

ADC误差的产生以及如何提高ADC的精度

利用AD5933的高精度生物阻抗测量方案

Easy Drive ADC简化高阻抗传感器的测量

芯海CS1256|带人体阻抗测量模块BIM功能和24位ADC的AFE

如何利用高输入源阻抗提高ADC测量精度

如何利用高输入源阻抗提高ADC测量精度

评论