今年,第 68 届年度 IEEE 国际电子器件会议 (IEDM) 全面恢复,来自世界各地的近 1,500 名工程师(亲临现场)每年都会返回旧金山市中心,讨论半导体行业的最新发展。虽然学术界和工业界都有大量有趣的论文,但台积电的那篇论文带来了可怕的坏消息——虽然逻辑仍在或多或少地沿着历史趋势线扩展,但 SRAM 扩展似乎已经完全崩溃。

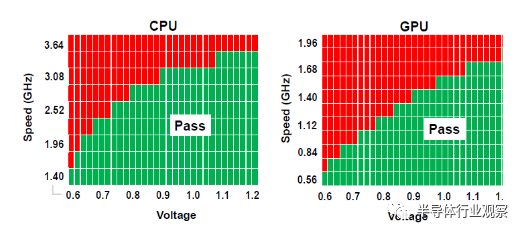

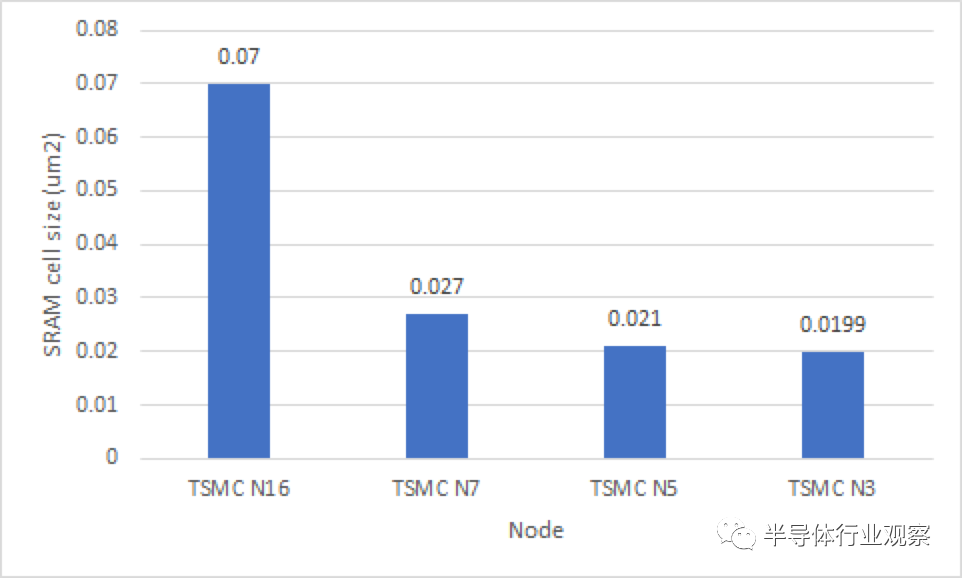

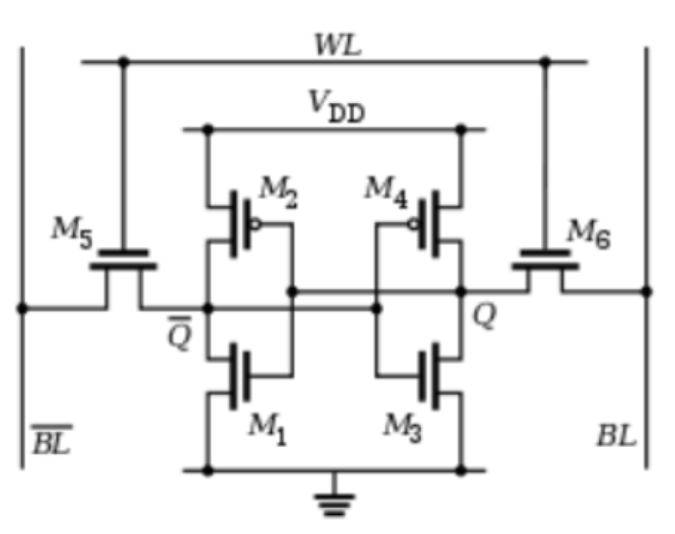

在会议上,台积电谈到了原始基础 N3 (N3B) 节点以及增强型 (N3E),后者是N3B 稍微宽松一些的变体。台积电展示原型测试芯片配备了一个由超过 35 亿个晶体管和一个可完全运行的 256Mbit SRAM 宏组成的逻辑电路(图 1)。SRAM 存储单元面积为 0.0199μm 2,是有史以来最小的。我们确认 SRAM 宏即使在 0.5V 的电压下也能完美工作(图 2)。

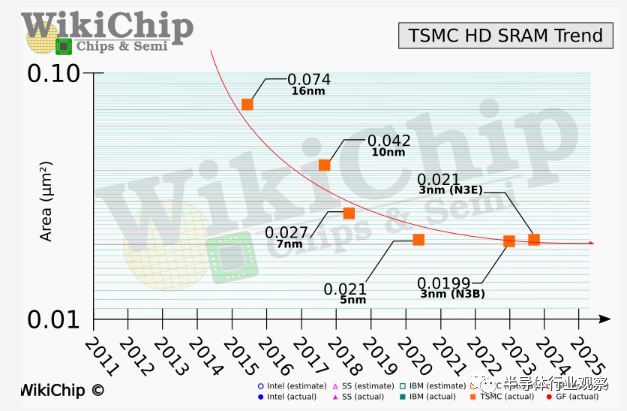

有趣的是,对于新的 N3E 节点,高密度 SRAM 位单元尺寸达到 0.021 µm²,这与他们的 N5 节点的位单元大小完全相同,并没有缩小。N3B 变体预计不会进入太多产品,但确实具有缩放 SRAM 位单元;然而,在 0.0199µm² 时,它仅缩小了 5%(或缩小了 0.95 倍)。

就粗略的内存密度而言(假设 ISO 辅助电路开销),N3E 大致为 31.8 Mib/mm²,并将增加到 33.55 Mib/mm² 或 1.75 Mib/mm²(230 KB)的改进。

这是一些严重的坏消息!从这个角度来看,虽然据说 N3B 和 N3E 都提供了 1.6 倍和 1.7 倍的芯片级晶体管缩放,但 SRAM 的 1.0 倍和 1.05 倍缩放是灾难性的。现在,我们仍然希望台积电在某个时候为 N3 推出更密集的 SRAM 位单元变体,我们确实希望在未来看到 SRAM 的某种程度的微缩,但好的旧微缩 SRAM 微缩似乎已经死了。

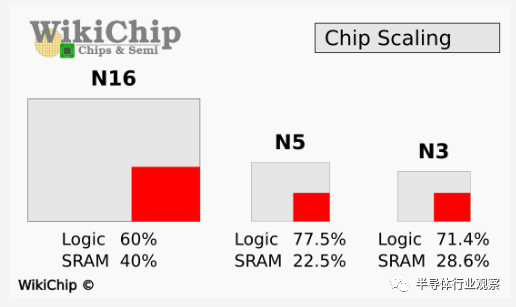

考虑一个假设的 100 亿晶体管芯片,其中包含 40% 的 SRAM 和 60% 的逻辑,位于 TSMC N16 上。忽略实际限制和模拟/物理/等,这样一个假设的芯片将约为 255 平方毫米,其中 45 平方毫米或 17.6% 用于 SRAM。将完全相同的芯片缩小到 N5 将产生一个 56 平方毫米的芯片,其中 12.58 平方毫米或占芯片的 22.5% 用于 SRAM。将芯片进一步缩小到 N3(基于我们最初但未完全确认的值)将产生一个 44 平方毫米的芯片,其 SRAM 密度相同为 12.58 平方毫米,现在占面积的近 30%。

当然,这种影响不会在所有方面都感受到同样的影响。芯片上 SRAM 和缓存的百分比因目标市场和整体能力而异。然而,对于一些 AI 硬件初创公司来说,架构要求芯片的很大一部分被 SRAM 覆盖,这些工程师将比其他人更快地遇到更多挑战。

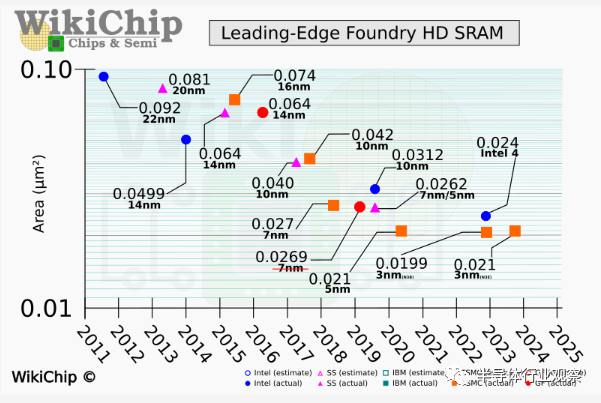

SRAM 微缩的崩溃并不仅限于台积电。我们已经指出 SRAM 缩放速度变慢的问题已经有一段时间了。例如,虽然英特尔仍在缩减其 SRAM 位单元,但该公司最近宣布的Intel 4 进程SRAM 缩放比例已从历史上的 0.5-0.6 倍放缓至 0.7-0.8 倍。对于 Intel 4,我们的估计密度(ISO 辅助电路开销与 TSMC 相比)为 27.8 Mib/mm² 或 4 Mib/mm² 或落后 13%。期望 Intel 的 Intel 3 工艺能够匹敌或击败它们并非不切实际。

那么,我们该何去何从?事实上,目前唯一可行的 SRAM 替代品就是更多的 SRAM,因此我们预计 SRAM 会直接占用更多的面积。这并不是说我们不期望更多的 SRAM 扩展。虽然我们确实希望台积电和其他代工厂生产更密集的 SRAM,但历史上的扩展似乎已经正式结束。Imec 等一些研究机构提出了更高密度的 SRAM 位单元。例如,在去年的 IEDM 2021 上,Imec 在一个假设的“超越 2 纳米节点”上展示了大约 60 Mib/mm² 的 SRAM 密度,大约是今天密度的两倍,该节点使用utilizing forksheet晶体管和先进的双面互连方案。

除了 SRAM,业界一直在研究许多其他替代内存架构。新兴的内存技术包括 MRAM、FeRAM、NRAM、RRAM、STT-RAM、PCM 等。与 SRAM 相比,这些新兴的内存位单元提供了独特的权衡,例如在较低的读/写规范下具有更高的密度、非易失性能力、较低的读写周期能力,或者在可能较低的密度或速度下具有较低的功耗。虽然它们不是 SRAM 的直接替代品,但向前发展它们可能会扮演 4 级或 5 级缓存的角色,其中较低的性能权衡可以通过更高的密度来抵消。

目前,该行业似乎已经到了一个有趣的拐点。

审核编辑 :李倩

-

台积电

+关注

关注

44文章

5651浏览量

166664 -

sram

+关注

关注

6文章

768浏览量

114730 -

晶体管

+关注

关注

77文章

9705浏览量

138463

原文标题:我们将见证SRAM的死亡?

文章出处:【微信号:光刻人的世界,微信公众号:光刻人的世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SRAM和DRAM有什么区别

SRAM1/2/3可以使用LPDMA通过LPTIM触发ADC4搬运数据到SRAM4吗?

请问如何使用片外SRAM?

请问ESP32上的SRAM1是否可用?

XMC7200是否支持从外部QSPI/OctalSPI闪存到XMC7200内部SRAM的M-DMA传输?

用MDK将UCOS+UCGUI下载到外部SRAM中调试慢怎么解决?

STM32CubeIDE STM32F407+外部SRAM如何将数值指定存储到外部RAM?

Microchip推出容量更大、速度更快的串行SRAM产品线

Microchip推出容量更大、速度更快的串行 SRAM产品线

STM32F4定义在SRAM2数组里的数据可以memcpy到CCM中的数组吗?

GD32F4的TCMSRAM(紧耦合SRAM)该如何使用?

SRAM CLA和SRAM有什么区别

我们将见证SRAM的死亡?

我们将见证SRAM的死亡?

评论