当今的电子应用通常需要不止一个5 V或3.3 V电源电压。需要 10、20 或更多的电压并不罕见。除此之外,电压域具有相同的电压电平,但必须作为域单独生成,也就是说,这些电压必须产生两次。一个例子是实现两个相同的电压来提供模拟和数字负载。这种分离可防止相互干扰,并在不同时间为各种负载提供能量。

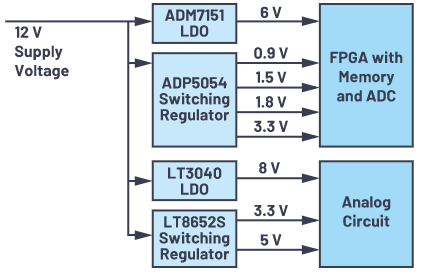

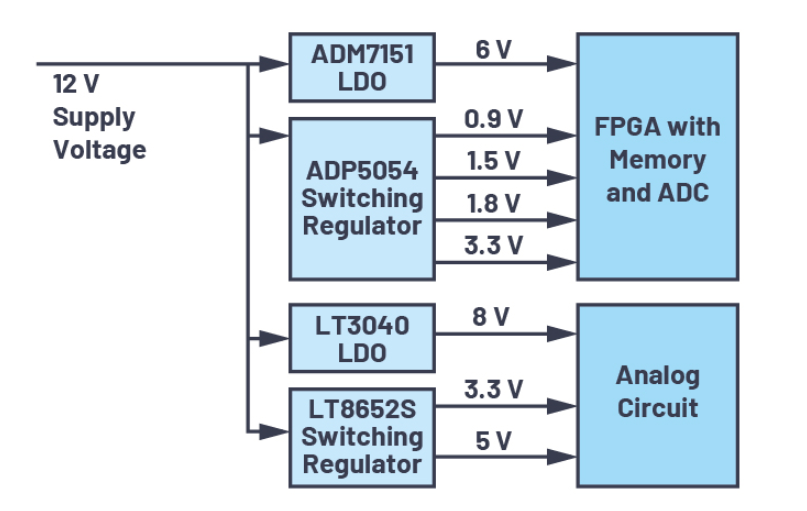

图1显示了具有众多不同电压域的系统框图。这些电压由单独的开关稳压器和线性稳压器产生。各个电压转换器的选择在很大程度上取决于所需的转换效率、要产生的电压,尤其是各个负载消耗的电流。因此,各个电压转换器的设计差异很大。

图1.典型的电子系统需要八个电压。

此外,每个转换器各个电压的延迟将不同。这会导致不同电压域中不受控制的斜坡上升,从而导致功能问题和系统损坏。

因此,通常需要可靠的上电序列,以确保每个电压在正确的时间达到其目标值。通常,关断时还必须遵循特定的关断顺序。

在具有多个电源电压的系统中,监控不同电压的能力可能很重要。在只有两个电压域的系统中看似微不足道的事情对于许多电压变得非常复杂。因此,许多定序器器件还具有内置监控器或电压监控功能。

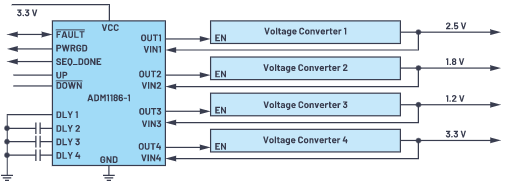

图2所示为ADM1186-1模拟时序控制器IC。它可以控制和监视四个电压域。电压的上电和断电通过控制相应电压转换器上的使能(开/关)引脚来实现。电压转换器的导通时间可以通过使用小电容器的时间延迟来调节。相应的输出电压通过相应的监控引脚进行监控。当所有电压都建立后,时序控制器电路产生电源良好信号。

图2.ADM1186-1模拟时序控制器解决方案,用于监控多达4个电压转换器。

ADM1186-1等模拟时序控制解决方案易于使用。它们具有具有多个电压的系统所需的所有功能。它们与数字定序器的不同之处在于,它们的设计不太复杂,并且系统中需要的数字监控功能更少。例如,他们可以没有PMBus或类似的协议。

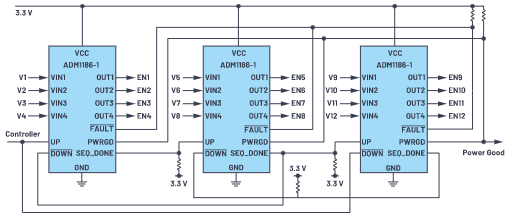

在图1所示的示例系统中,使用了八个电压域。如何对具有四个以上电压域的系统进行排序和监控?为此,可以将多个ADM1186-1电路组合成一个序列,并且可以将任意数量的ADM1186-1时序控制器连接在一起。

市场上有许多使用耦合单个测序仪进行此类测序的例子。然而,ADM1186-1之所以脱颖而出,是因为它还支持上电期间的完整时序控制,以及在链接应用中使用时关断,如图3所示。类似的解决方案可以提供连接各种时序控制器IC的可能性,但它们只提供单个电压的受控斜坡上升,而不是受控的下序,即在菊花链星座中,电压的断电。

图3.多个ADM1186-1器件链接在一起,用于对12个电压的上电和关断进行排序。

可靠的受监控上电和关断在许多现代系统中非常重要,使用ADM1186-1等解决方案可以灵活地实现,只需很少的开发工作。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17749浏览量

250588 -

控制器

+关注

关注

112文章

16385浏览量

178391 -

开关稳压器

+关注

关注

4文章

794浏览量

73483

发布评论请先 登录

相关推荐

可靠的上电和关断顺序

可靠的上电和关断顺序

评论