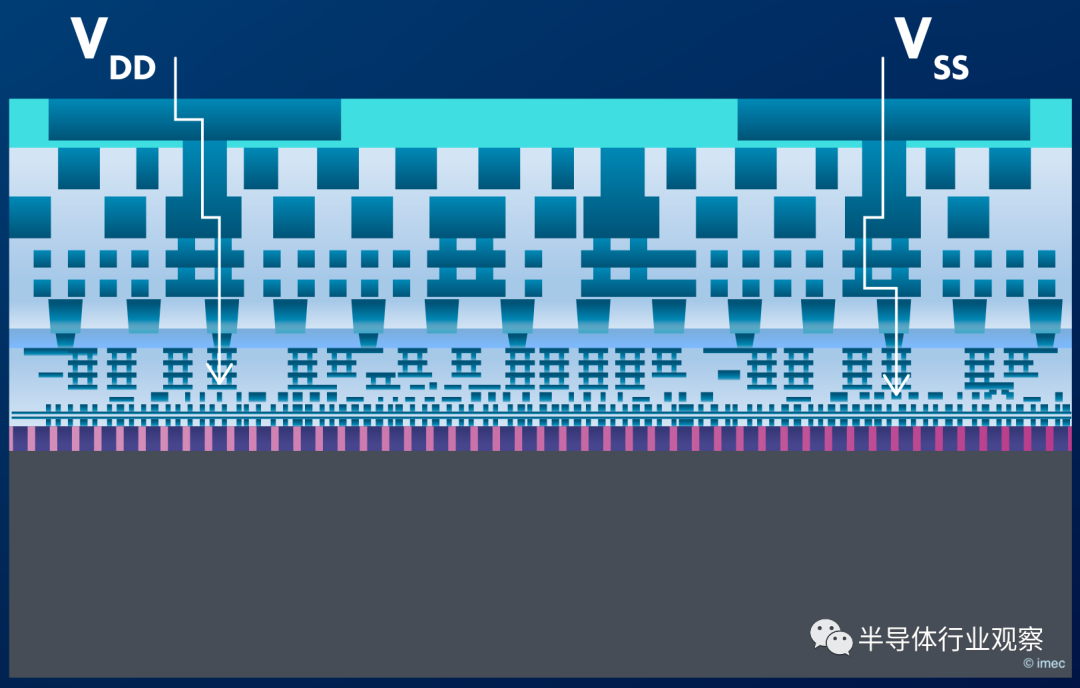

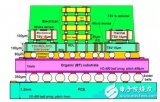

芯片上的供电网络(power delivery network)旨在最有效地为die上的有源器件提供电源和参考电压(即 VDD和 VSS)。传统上,它被实现为通过晶圆正面的后端线 (BEOL) 处理制造的低电阻金属线网络。供电网络与信号网络共享这个空间,即设计用于传输信号的互连。

为了将功率从封装传输到晶体管,电子穿过 BEOL 堆栈的所有 15 到 20 层通过金属线和通孔,这些金属线和通孔在接近晶体管时变得越来越窄(因此电阻更大)。在途中,它们会失去能量,从而导致功率传输或IR 下降。当到达更接近晶体管时,即在标准单元级别,电子最终进入在BEOL 的 M int层中组织的 V DD和 V SS电源和接地轨。这些轨道占据了边界处和每个标准单元之间的空间。

从这里,它们通过中间互连网络连接到每个晶体管的源极和漏极。

图1.传统前端供电网络的示意图。

但随着每一代新技术的出现,这种传统的 BEOL 架构都难以跟上晶体管缩放路径的步伐。如今,“电源互连”在复杂的 BEOL 网络中争夺空间的竞争越来越激烈,至少占布线资源的 20%。此外,电源和接地轨在标准单元级别占据了相当大的面积,限制了标准单元高度的进一步缩放。在系统级,功率密度和 IR 压降急剧增加,这让设计人员难以维持稳压器和晶体管之间的功率损耗允许的 10% 余量。

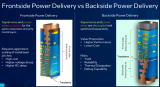

背面供电网络的承诺

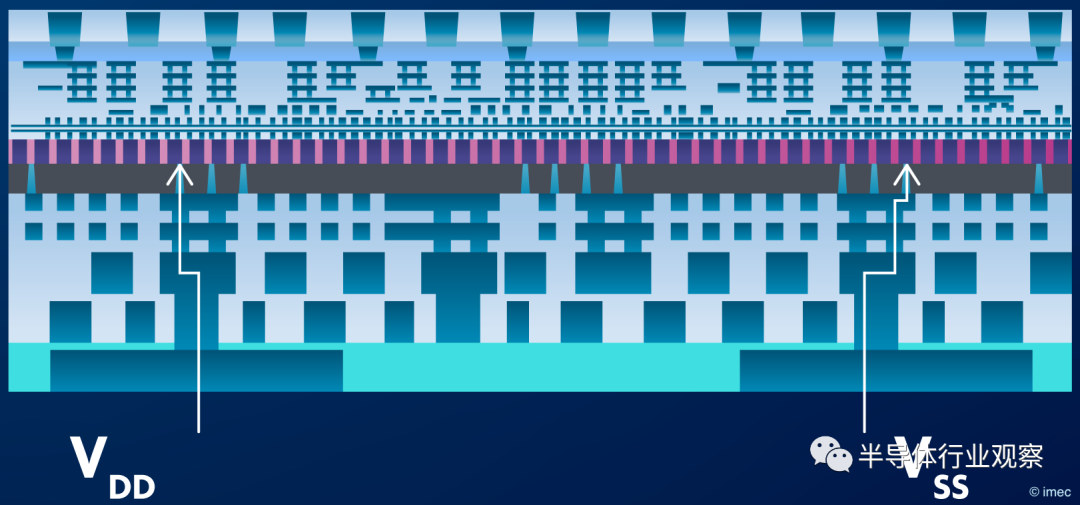

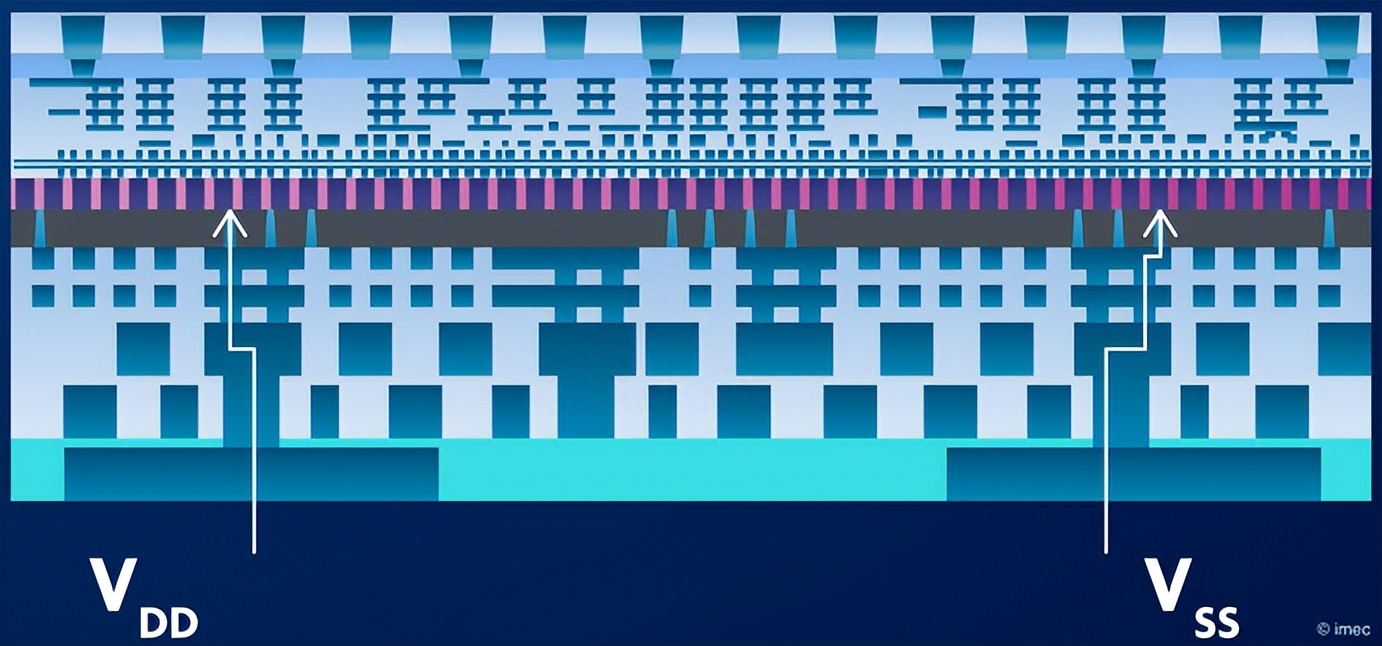

背面供电网络有望解决这些问题。这个想法是通过将整个配电网络移动到硅晶圆的背面来将电力传输网络与信号网络分离,而硅晶圆目前仅用作载体。

从那里,它可以通过更宽、电阻更小的金属线将电力直接输送到标准电池,而电子无需穿过复杂的 BEOL 堆栈。这种方法有望降低 IR 压降,提高功率传输性能,减少 BEOL 中的布线拥塞,并且如果设计得当,还可以进一步扩展标准单元高度。

图2.背面供电网络允许将供电与信号网络去耦。

埋地电源轨和纳米硅通孔:关键技术构建块

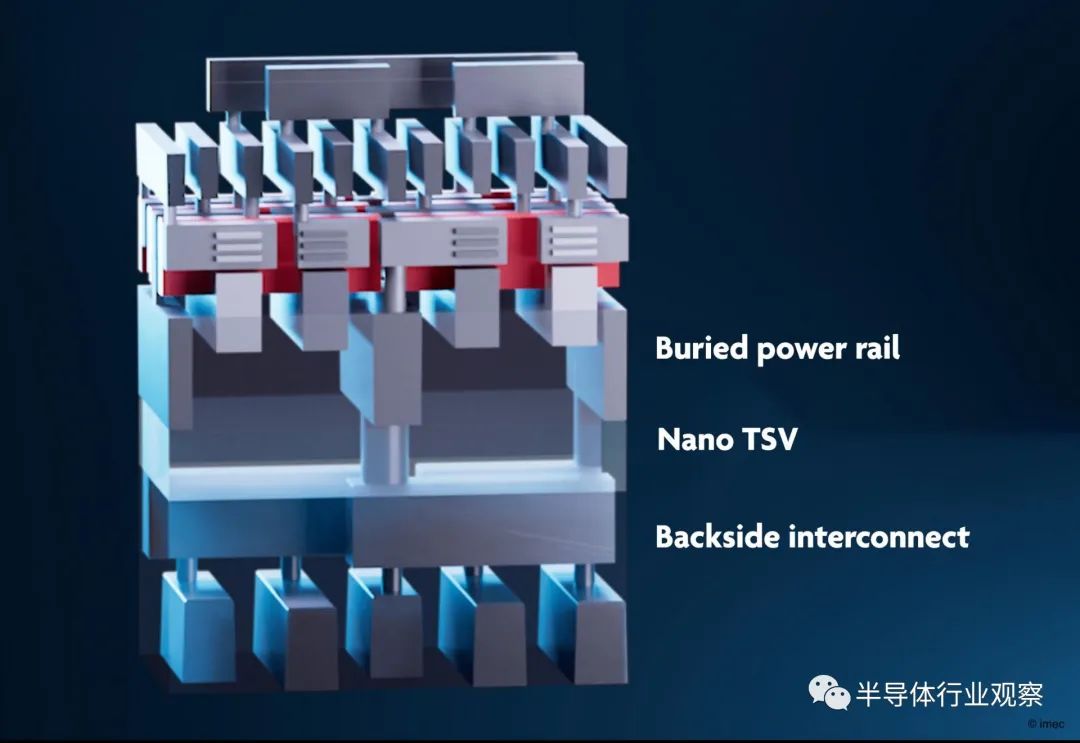

在详细介绍制造背面供电网络的工艺流程之前,我们先介绍两种技术推动因素:埋入式电源轨 (BPR) 和纳米硅通孔 (nTSV)。

BPR 是一种技术缩放助推器,可进一步缩放标准单元高度并减少 IR 压降。它是埋在晶体管下方的金属线结构——部分在硅衬底内,部分在浅沟槽隔离氧化物内。它承担了传统上在标准单元级别的 BEOL 中实现的 VDD和 VSS电源轨的作用,这一从 BEOL 到生产线前端 (FEOL) 的历史性转变允许减少 M int轨道的数量,从而进一步缩小标准单元。此外,当垂直于标准单元设计时,可以放宽导轨的尺寸,从而进一步降低 IR 压降。

当与 nTSV 结合时,BPR 的潜力可以得到充分利用,nTSV是在减薄晶圆背面加工的高纵横比通孔。它们一起允许以最有效的方式将功率从晶圆背面传输到前端的有源器件,即在降低 IR 压降方面获得最大收益。

图3.背面供电网络实施的示意图,其中纳米片通过 BPR 和 nTSV 连接到晶圆的背面。

量化承诺

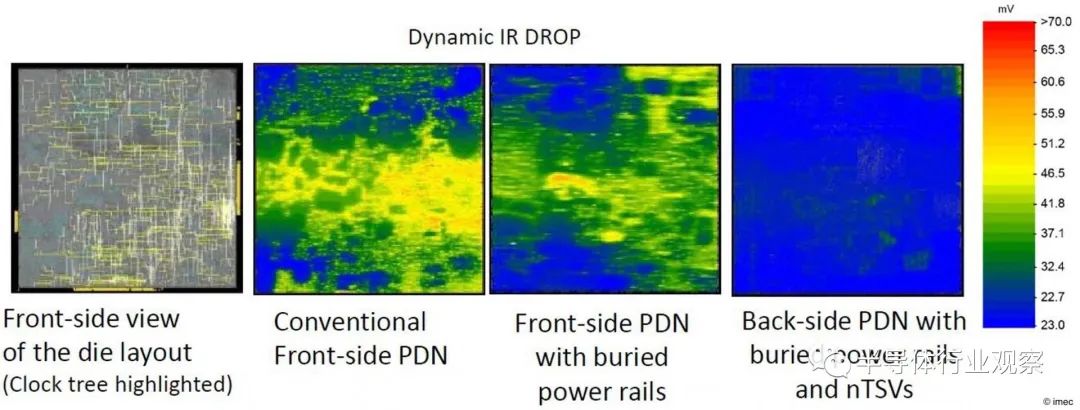

在 2019 年 IEDM 会议上,imec 研究与 Arm合作对这些承诺进行了量化。Arm 在其采用高级设计规则设计的中央处理器 (CPU) 之一上运行了仿真。他们比较了三种供电方式:传统的前端供电、结合 BPR 的前端供电以及在 BPR 上使用 nTSV 的背面供电。就功率传输效率而言,后者显然是赢家。片上功率热图显示,与传统的前端功率传输相比,具有前端功率传输的 BPR 可以将 IR 压降降低约 1.7 倍。但是背面供电的 BPR做得更好:它们将 IR 压降大大降低了 7 倍。

图4在动态 IR 压降方面比较不同的功率传输方法。

整体流程

下面,我们阐明了 BSPDN 的一个具体实现的工艺流程,其中nTSV——在极薄的晶圆背面处理——落在 BPR的顶部。这些器件,例如在晶圆正面处理的按比例缩放的 FinFET,通过 BPR 和 nTSV 连接到晶圆的背面。

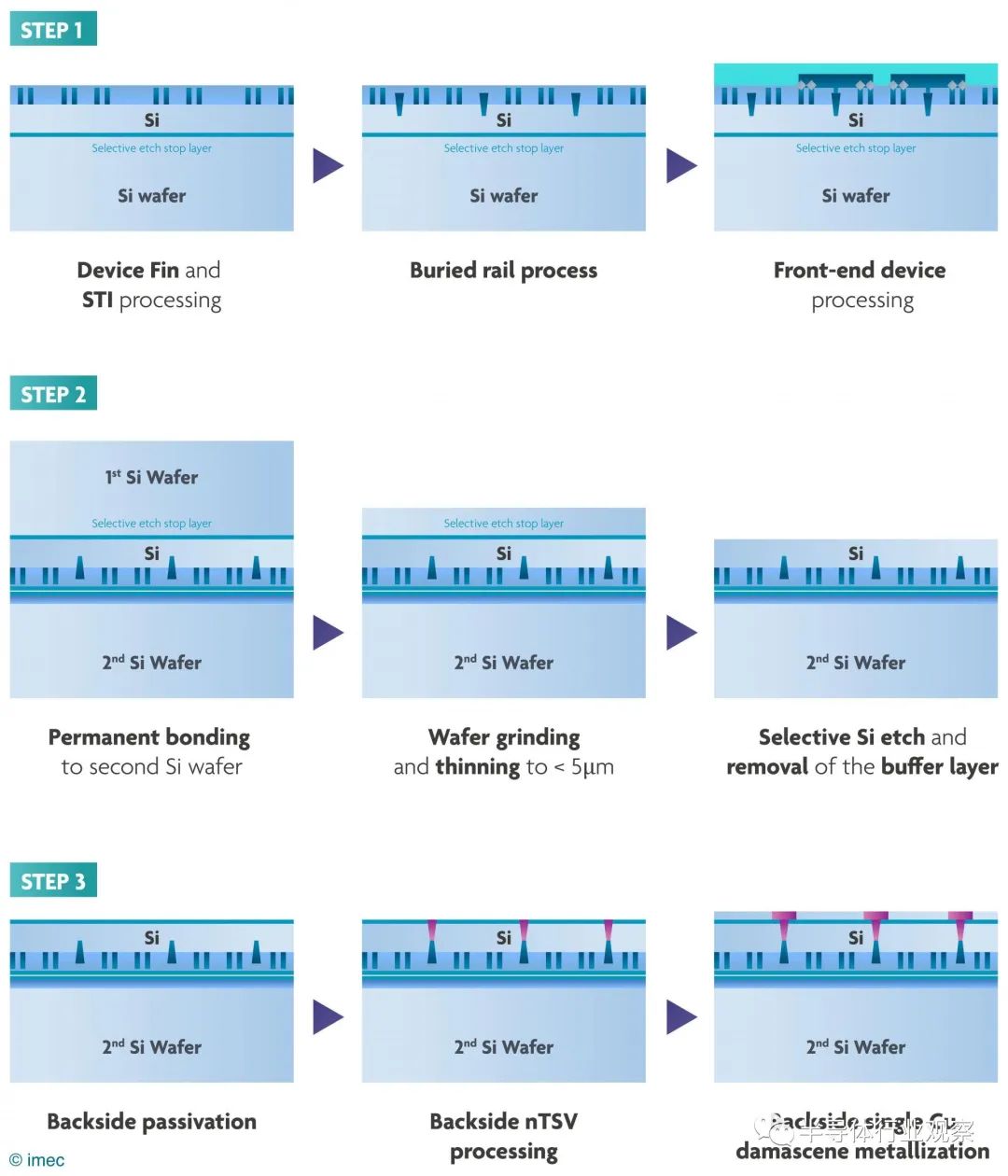

图5.BPR 连接到 nTSV 的背面供电网络的工艺流程。为简化起见,步骤 1 中的一些细节已在步骤 2 和 3 中省略,包括 BPR 与设备之间的连接。

第一步:埋轨正面处理

工艺流程从在 300mm Si 晶圆顶部生长 SiGe 层开始。SiGe 层随后用作蚀刻停止层以结束晶圆减薄(步骤 2)。接下来,在 SiGe 层的顶部生长一个薄的 Si 覆盖层:制造器件和埋入电源轨的起点. 埋入式电源轨是在浅沟槽隔离之后定义的。在 Si 覆盖层中蚀刻的沟槽填充有氧化物衬里和金属,例如 W 或 Ru。由此产生的掩埋轨道通常宽约 30 纳米,间距约 100 纳米。然后金属凹陷并被电介质覆盖。在 BPR 实施后完成器件(在本例中为按比例缩放的 FinFET)的处理,并且 BPR 通过 VBPR 过孔和 M0A 线连接到晶体管源/漏区。铜金属化完成正面处理。

第 2 步:晶圆间键合和晶圆减薄

翻转包含器件和 BPR 的晶圆,并将“有源”正面键合到覆盖载体晶圆上。这是通过在室温下使用 SiCN-to-SiCN 电介质熔接,然后在 250°C 下进行键合后退火来实现的。

然后,可以将第一个硅片的背面减薄到 SiGe 蚀刻停止所在的位置。通过顺序背面研磨、化学机械抛光 (CMP) 以及干法和湿法蚀刻步骤的组合实现减薄。SiGe 层在下一步中被移除,晶圆已准备好进行 nTSV 处理。

第 3 步:nTSV 处理和连接到 BPR

在沉积背面钝化层后,通过硅对准光刻工艺从晶圆背面对nTSV 进行图案化。nTSV 蚀刻穿过 Si(几 100nm 深)并落在 BPR 的尖端。接下来,nTSV填充有氧化物衬里和金属 (W)。在这个特定的实现中,它们以 200 纳米间距集成,而不会占用标准单元的任何面积。该流程通过处理一个或多个背面金属层来完成,通过 nTSV 将晶圆的背面电连接到正面的 BPR。

仔细研究关键流程步骤

实施背面供电网络为芯片制造增加了新的步骤。在过去的几年里,imec 展示了各种关键技术构建模块,逐渐解决了新生产步骤的挑战。

BPR:在生产线前端引入金属

在建议的制造流程中,在器件处理之前,埋入式电源轨在 FEOL 中实现。这种实施意味着金属导轨要经受后续设备制造过程中应用的高温工艺步骤。对于芯片制造商而言,这似乎与几十年前将 Cu 引入 BEOL 一样具有破坏性。因此,用于制造 BPR 的金属的选择至关重要。Imec 可以成功地展示由难熔金属(如 Ru 或 W 等具有高度耐热性的金属元素)制成的埋地电源轨的集成。在随后的 FEOL 处理过程中保持金属导轨盖住是避免前端污染的一项额外措施。

Imec 认为,在可扩展性和性能方面,使用 nTSV 结合 BPR 是一种非常有前途的实现方案。背面供电网络的其他实现也存在,每一种都在供电性能、标准单元面积消耗和前端离线复杂性之间进行权衡。

晶圆减薄:最小化厚度变化

需要将晶圆极度减薄到几 100 纳米的 Si,以暴露 nTSV 并最小化它们的电阻率(以及因此的 IR 压降)。这严重限制了允许的厚度变化,这可能在不同的晶圆减薄步骤期间引起。Imec 与多个合作伙伴合作改进用于蚀刻的化学物质。例如,最终的湿法蚀刻能够实现在 SiGe 层上停止的高选择性软着陆工艺。在减薄工艺的最后一步,SiGe 蚀刻停止层在需要对 Si 具有非常高选择性的专用化学物质中被去除。这样,可以暴露 Si 覆盖层,总厚度变化低于 40nm。

另一个问题是由于(否则会散热)Si 基板的极度变薄对器件自热的热影响。初步建模工作表明,自热效应在很大程度上可以被晶圆背面的金属线抵消,金属线提供额外的横向热扩散。目前正在进行更详细的热模拟以获得更多见解。

晶圆键合:精确的 nTSV/BPR 对准

晶圆键合步骤固有地扭曲了第一个“有源”晶圆。这种变形挑战了在晶圆背面图案化 nTSV 所需的光刻步骤。更具体地说,它挑战了 nTSV 需要与底部 BPR 层对齐的精度。由于我们处理的是标准单元尺寸的特征,因此覆盖要求应优于 10nm。然而,传统的光刻对准不能充分补偿晶圆变形。

幸运的是,晶圆间键合技术的进步可以显着降低对准误差和畸变值。此外,通过使用先进的光刻校正技术,覆盖错误相对于 BPR 结构的 nTSV 光刻可以减少到小于 10nm。

不会降低设备性能

一个重要的问题仍然存在:新添加的工艺步骤,例如 BPR 集成、晶圆减薄和 nTSV 处理,是否会影响前端制造的器件的电气性能?

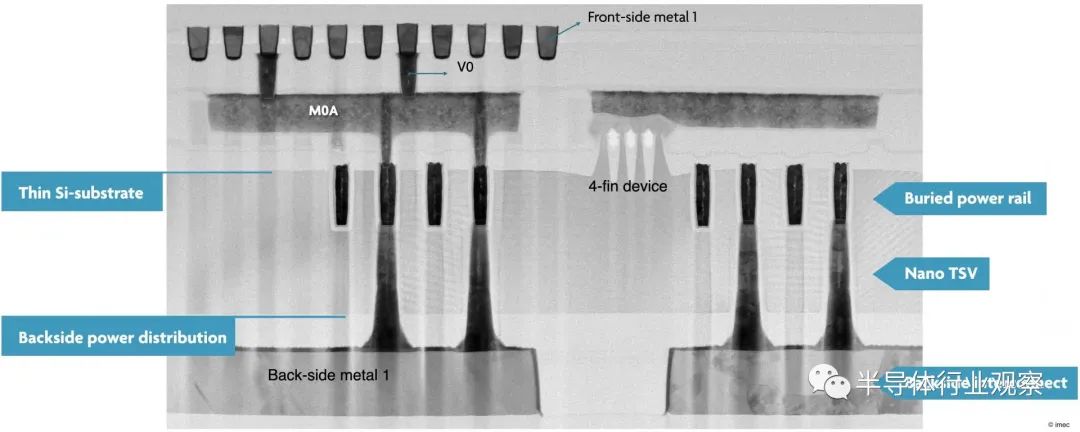

为了回答这个问题,imec 最近使用上述制造流程和改进的工艺步骤制造了一个测试产品。在此测试工具中,按比例缩小的 FinFET 通过 320 纳米深的 nTSV 落在 BPR 上,以严格的覆盖控制连接到晶圆的背面。BPR 还通过 M0A 层和 V0 通孔连接到正面金属化层。除其他外,这种正面连接使研究人员能够评估背面处理前后设备的电气性能。通过该测试工具,imec 表明FinFET 性能不会因 BPR 实施和背面处理而降低,前提是在最后执行退火步骤以获得最佳器件特性。

图6.TEM 图像显示按比例缩放的 FinFET 连接到晶圆的背面和正面。

应用领域:高级逻辑 IC 和 3D-SOC 的扩展

一些芯片制造商已经公开宣布在 2nm 及以下技术节点的逻辑 IC 中引入背面供电网络。这是纳米片晶体管取得进展的时候。然而,新颖的路由技术可用于范围广泛的晶体管架构。Imec 的路线图预见了它在先进技术节点中的引入,以及 6T 标准单元中的纳米片晶体管。与 BPR 的结合将有助于将标准电池高度推至 6T 以下。

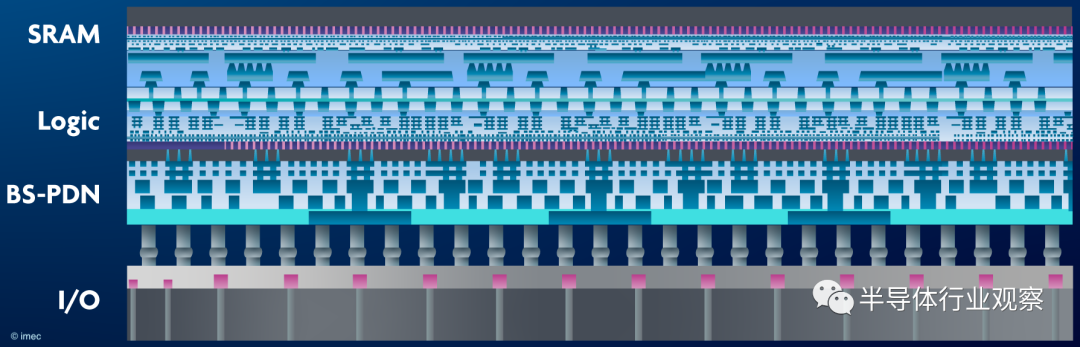

但应用领域不仅仅局限于 2D 单芯片 IC:它还有望提高3D 片上系统的性能(3D SOC)。想象一下 3D-SOC 实现,其中一些或所有存储器宏被放置在顶部裸片中,而逻辑被放置在底部裸片中。在技术方面,这可以通过将“逻辑晶圆”的有源正面粘合到“存储晶圆”的有源正面来实现。在此配置中,两个晶圆的原始背面现在位于 3D-SOC 系统的外部。我们现在可以考虑利用“逻辑晶圆”的“自由”背面来为耗电大的核心逻辑电路供电。这可以通过与为 2D SOC 提议的相同的方式来完成。主要区别是:原来的虚拟覆盖晶圆——之前为了使晶圆变薄而引入——现在被第二个有源晶圆(在本例中为存储晶圆)取代。

图7.具有背面功率传输实施的 3D-SOC 的示意图。

尽管这种设计尚未通过实验实施,但从 IR 压降角度进行的初步评估非常令人鼓舞。使用高级节点研究过程设计套件 (PDK)在逻辑上的内存分区设计上验证了所提出的解决方案。使用 nTSV 和 BPR 实施背面供电网络显示出可喜的结果:与传统的正面供电相比,底部裸片的平均和峰值 IR 压降减少了 81% 和 77%。这使得背面供电成为高级 CMOS 节点中 3D IC 供电的理想选择。

对于 2D 和 3D 设计,通过在背面添加特定设备(例如 I/O 或 ESD 设备),可以将利用晶圆自由背面的概念扩展到其他功能。例如,Imec 将背面处理与实现 2.5D(即柱状)金属-绝缘体-金属电容器 (MIMCAP) 相结合,用作去耦电容器。2.5D MIMPCAP 将电容密度提高了 4 到 5 倍,从而进一步改善了 IR 压降。结果源自用实验数据校准的 IR 压降建模框架。

总结

未来的芯片很可能会打破通过前端供电的传统。具有背面金属、埋入式电源轨和 nTSV 的背面供电网络在降低 IR 压降、释放 BEOL 布线压力和改进标准单元高度缩放方面显示出明显的优势。BPR集成、晶圆键合、晶圆减薄和nTSV工艺等关键工艺步骤正在逐步完善,为新的布线技术引入先进的逻辑技术节点和未来的3D SOC做准备。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17697浏览量

249923 -

芯片

+关注

关注

455文章

50697浏览量

423046 -

稳压器

+关注

关注

24文章

4222浏览量

93751

原文标题:如何从背面为芯片供电

文章出处:【微信号:cetc45_wet,微信公众号:半导体工艺与设备】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MAX40660数据手册中的示例为单电源轨+3.3V供电,请问用+/-1.8V供电是否可行?

如何使用Fly-buck™为低电压、低功耗工业应用供电

ADP505x可为多个电源轨和紧凑式设计的中型FPGA供电

为Xilinx Zynq 7000系列FPGA供电所需电源轨的参考设计

埋入式电源轨和纳米硅通孔技术为为背面芯片供电

埋入式电源轨和纳米硅通孔技术为为背面芯片供电

评论