JESD204B接口一般用在高速的AD和DA芯片上,用于传输采集到的数据。该接口相比LVDS可以减少大量的IO管脚,所以正在逐步取代LVDS接口(引用wp446-jesd204b.pdf)。

Xilinx提供了JESD204B对应的IP和相应的phy。本文主要介绍xilinx-JESD204B的使用方法,基本上都是从pg066手册得到的总结,但也有自己的一些心得。

JESD204有很多的分支,包括A,B,C等,主要的区别是支持的速率不同。最早的JESD版本不支持精确的延时,后来版本不断升级,现在使用JESD204协议通过使用sysref和sync达到了精准延时的效果,毕竟现在的速率达到几十G,没有精确的延时不能达到具体的设计要求。JESD204B的subclass0是没有精准延时的,subclass1使用sysref,subclass2使用sync。由于有了精准的要求,所以对sysref和sync的时序要求很高。

言归正传,使用xilinx的JESD204B IP核,最简单的方式是通过使用example design开始,并且pg066中也是这么建议的,为什么?第一是简单,官方已经提供给了一个教程,自己照猫画虎就行了;最重要的是,单独的JESD204B IP核一般不能使用,需要有对应的PHY,因此如果不使用example design,自己就得再例化一个JESD204 PHY的IP,所以使用example design方便了很多,所以这种方法最简单。

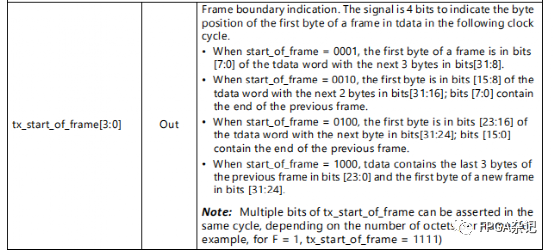

这个IP的接口比较简单,查看pg066基本都能了解是干什么用的,我只介绍一下tx_start_of_frame这个信号。手册对这个信号的介绍如下图所示:

我重点关注 Note 部分,这部分的意思是说tx_start_of_frame信号会根据每帧包含的字节个数而使多个bit置位,并举例说明:当F=1(F表示的每帧包含的字节个数)时,tx_start_of_frame信号为4’b1111。同样的在仿真example design时,testbeach中F=2,查看波形可以看到tx_start_of_frame为4’b0101。但为什么会出现多bit 置 1 呢?这是因为发送数据tx_data的位宽为32bit,而当F很小时,tx_data的32bit数据中包含多个数据帧,所以导致tx_start_of_frame信号的多bit置 1 。即当F=1时,表示一帧数据只有一个字节,所以tx_data(32bit)中包含4个数据帧,而每个字节都是起始位,所以tx_start_of_frame为4’b1111;同理,当F=2时,表示一帧数据包含两个字节,所以tx_data包含2个数据帧,起始位置在第1和第3字节,所以tx_start_of_frame为4’b0101。而F为较小时比较常见,尤其是在AD采集芯片中,因为AD芯片输出的有效数据的位宽通常为8、12、14,转换之后的F值就是1或者2。

PS:看到了一个好的博客,附上链接,不知道让不让转发,在博客中没有看到禁止项,有问题请及时联系我。https://blog.csdn.net/weixin_41974812/article/details/117220777

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8610浏览量

151213 -

Xilinx

+关注

关注

71文章

2167浏览量

121466 -

lvds

+关注

关注

2文章

1043浏览量

65818 -

JESD204B

+关注

关注

5文章

76浏览量

19140

原文标题:JESD204B学习手册

文章出处:【微信号:FPGA杂记,微信公众号:FPGA杂记】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

JESD204B的系统级优势

JESD204B串行接口时钟的优势

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

如何采用系统参考模式设计JESD204B时钟

JESD204B协议介绍

JESD204B的优势

JESD204B SystemC module 设计简介(一)

JESD204B标准及演进历程

JESD204B使用说明

JESD204B学习手册

JESD204B学习手册

评论