已发表的文章

本章节将简要介绍安森美(onsemi)近期正在进行的研究。参考文献部分列出了相关出版物,可为读者提供希望获取的所有细节,以便更深入地了解这些技术主题。

偏置温度不稳定性 (BTI)

众所周知,BTI是硅器件的退化模式,由于在半导体/氧化物界面或附近产生陷阱或陷阱电荷,MOSFET的阈值电压漂移,最终导致导通电阻增加的不利影响。SiC MOSFET也受到影响,而且需要应对宽带隙材料,这使得研究工作更加复杂。在直流模式和开关模式下,都需要充分了解材料的行为。

多年来,安森美一直将SiC/SiO2界面表征及其本征可靠性评估作为工作重点之一,并建立了一个研究网络,通过选定的研究合作伙伴和实验技术,研究和改善界面状态和迁移率(见图4)。

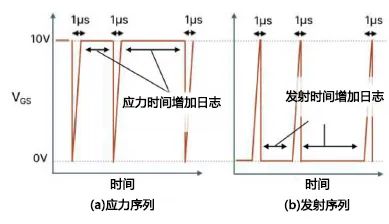

通过使用高温(正和负)栅极偏置应力,对封装后的器件进行导通和关断状态的静态BTI评估,包括应力后电气参数的漂移分析。动态 BTI评估则需要更全面的方法。安森美投入相应资源来研究超快速偏置温度不稳定性(UF-BTI),并对施加正(PBTI)或负(NBTI)栅极应力(或两者)时的阈值电压(Vth)漂移进行测量和建模,如图10所示。

图10 用于研究SiC MOSFET上超快速BTI的应力/测量/发射序列示意图

在PBTI期间,“视在”Vth将漂移到更高的电压(由于电子俘获),而在NBTI期间,“视在”Vth将漂移到更低的电压(由于电子发射或空穴俘获)。PBTI具有一个长久可恢复分量,而NBTI只是部分可恢复。

传统的IDVG表征方案无法捕获快速分量。但在典型开关应用中(100 kHz,即大约5到10 秒),快速BTI分量将占主导地位,有可能成为潜在的应用障碍。

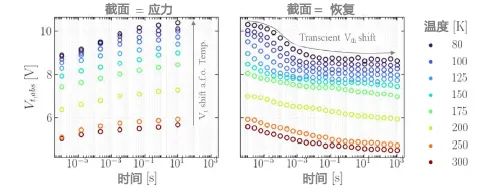

安森美收集的数据低至秒级范围,并且覆盖了广阔的温度范围,包括低温。

图11 VG = +10 V的PBTI期间和后续恢复期间

Vth漂移与时间和温度的函数关系

图12 Vg = -10 V的NBTI期间和后续恢复期间

Vth漂移与时间和温度的函数关系

具体步骤如下:

◆提取俘获发射时间(CET)图(Vth漂移由俘获的电荷引起,分布在能量和空间中)。图11显示了在10 V PBTI应力条件下,Vth在应力期间和后续恢复期间的漂移,图12则为-10 V NBTI应力下

◆Vth漂移的直流和交流建模(快速BTI分量用于应用,慢速BTI分量用于长期本征可靠性)

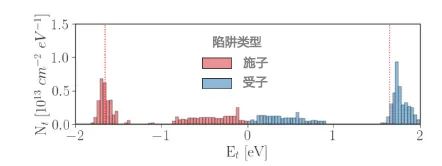

◆提取物理模型(缺陷类型、能量和深度),如图13所示

◆预测实际应用要求下的寿命。

图13 在NBTI和PBTI(使用Comphy模型)之后拟合绝对Vth漂移

从而可提取陷阱分布

低温UF-BTI研究结果已在ISPSD2022上发表[4]。

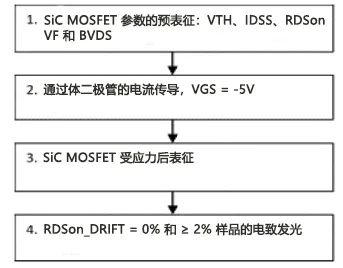

体二极管退化

SiC MOSFET中的体二极管应力引起的双极退化会导致导通电阻增加,这是由正向偏置时流经体二极管的电流触发的。这种退化有时也会报告为正向电压漂移或关断状态的泄漏增加。图14描述了该测试程序,而图15则显示了脉冲测量期间的正向压降VF和电流ID。

图14双极退化测试程序

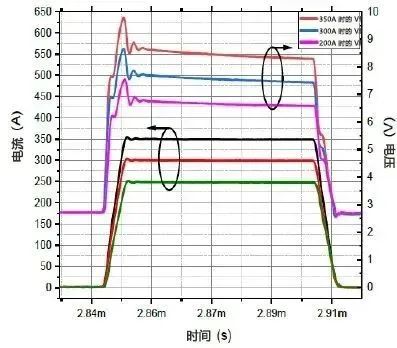

图15 在250、300和350 A 且VGS = -5 V时的脉冲电流测量期间

测得的体二极管瞬态正向压降VF和电流ID

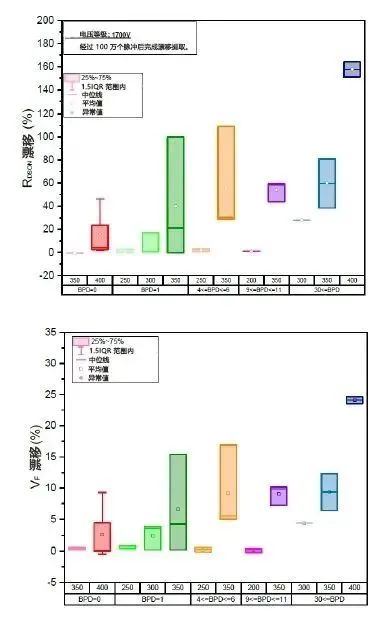

安森美评估了这种退化机制——最近在ECSCRM2021 [2]上发表了一项研究结果,对SiC MOSFET裸片中的BPD进行独立映射[CX1],以建立体二极管应力后的RDSon漂移与器件中BPD数量之间的相关性。RDSon和VF漂移随器件中BPD数量的增加而明显增加。然而,必须使用极高的电流密度(J > 1600 A/cm2)才能观察到无BPD时MOSFET的显著退化(图16)。

图16 1700 V 25 mΩ SiC MOSFET上的RDSon和VF漂移与BPD数量以及电流的关系

体二极管应力为100 万个50 秒的长脉冲

安森美针对所有SiC技术节点实施了以下措施:

◆实行目检,对每个生产晶圆进行全面的基晶面位错(BPD)扫描

◆采用高掺杂的外延缓冲层,将限制BPD堆垛层错的发展

◆最后,对最大电流密度的设计规则进行了定义,将其保持在每个MOSFET的安全工作区域内。

由于综合考虑了这三个因素,可以认为,安森美SiC MOSFET技术在高达1200 V时不受体二极管退化效应的影响。

动态应力

动态条件下的退化是与宽带隙材料相关的问题之一。安森美已在内部开发的测试台上开展动态应力研究(样本量有限)。下面我们介绍一个室温动态栅极应力测试的示例。

关于较大样本量(例如三个批次,每批次80 件)的动态应力测试,目前正在开发(内部开发以及与设备供应商合作开发)相应解决方案。

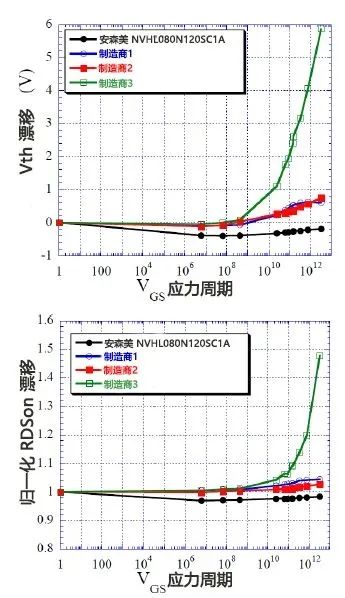

室温动态栅极应力:在T = 25℃、VDS = 0 V条件下,使用在-8 V 和20 V之间切换、占空比为50%的栅极驱动器,实施瞬态且无过冲的VGS应力[3]。

图17 安森美的商用1200 V 80 mΩ SiC MOSFET和其他三个制造商的1200 V SiC MOSFET产品的Vth漂移和归一化RDSon漂移

在不同的时间间隔后中断应力测量,以运行由Vth和RDSon组成的测试程序。图17显示了安森美的商用1200 V 80 mΩ SiC MOSFET以及其他三个制造商的1200 V SiC MOSFET产品的Vth漂移和归一化RDSon漂移(其中两个制造商的VGS = -8 V,超出了数据手册的额定值)。

总结

如本白皮书所述,安森美开发了一套全面的跨部门合作方案来评估SiC产品,高效且可靠地将其投放于市场。

缜密的设计方法、严格的生产监控、制造控制、充分的筛选和稳健的认证计划相结合,为SiC产品的稳定与可靠奠定了基础。

本文简要介绍了一些SiC器件所特有的挑战,进而引述了安森美对其进行表征和建模的方法。

我们已发表的文章提供了安森美正在进行的物理参数研究(欲了解最新研究成果,请阅读参考文献)。

参考文献

[1]

SiC 栅极氧化物寿命提取和建模的充电击穿 (QBD) 方法——P. Moens1、J. Franchi1、J. Lettens1、L. De Schepper1、M. Domeij1 和 F. Allerstam1——1安森美——ISPSD 2020

[2]

1700 V SiC MOSFET 的脉冲正向偏置体二极管应力与基晶面位错的独立映射——S. Kochoska1、M. Domeij1、S. Sunkari1、J. Justice1、H. Das1、H. Lee1, X.Q.Hu1 和 T. Neyer1——1安森美——ECSCRM 2021

[3]

平面型 SiC MOS 技术的栅极氧化层可靠性和 Vth 稳定性——M. Domeij1、J. Franchi1、S. Maslougkas1、P. Moens1、J. Lettens1、J. Choi1 和 F. Allerstam1——1安森美——ECSCRM 2021

[4]

碳化硅金属氧化物半导体场效应晶体管的低温超快偏置温度不稳定性陷阱分析——F. Geenen1、F. Masin2、A. Stockman1、C. De Santi2、J. Lettens1、D. Waldhoer3、M. Meneghini2、T. Grasser3 和 P. Moens1——1安森美比利时;2意大利帕多瓦大学;3奥地利维也纳理工大学——ISPSD 2022

往期推荐

碳化硅(SiC)——宽禁带半导体材料的征服之旅(第一部分)

原文标题:碳化硅(SiC)——宽禁带半导体材料的征服之旅(第二部分)

文章出处:【微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

-

安森美

+关注

关注

33文章

2167浏览量

95837

原文标题:碳化硅(SiC)——宽禁带半导体材料的征服之旅(第二部分)

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

碳化硅MOSFET器件国产化替代深度分析:基于英飞凌与基本半导体产品的栅极驱动负压阈值与开关速度校准

宽禁带半导体软开关损耗分析及死区时间自优化算法:针对SiC的极致效率设计

宽禁带电力电子转换半导体工业标准深度分析:JEDEC JC-70 委员会规程对SiC碳化硅器件寿命评估框架

碳化硅(SiC)——宽禁带半导体材料的征服之旅(第二部分)

碳化硅(SiC)——宽禁带半导体材料的征服之旅(第二部分)

![[新启航]<b class='flag-5'>碳化硅</b> TTV 厚度测量技术的未来发展趋势与创新方向](https://file1.elecfans.com/web3/M00/20/D6/wKgZPGhd-raAI0RYAACIgEePWXY565.png)

评论